Method for comparing hierarchical net list of integrated circuit

An integrated circuit, layered technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as repeated errors, incorrect matching, and inability to match

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

[0011] The specific implementation includes two steps:

[0012] 1) Hierarchical preprocessing, including sub-steps such as automatic identification of hierarchical units, breaking up units that cannot be one-to-one in the layout and schematic diagrams, dealing with short-circuit problems, device reduction, filtering of useless floating devices, and identification of gate circuits;

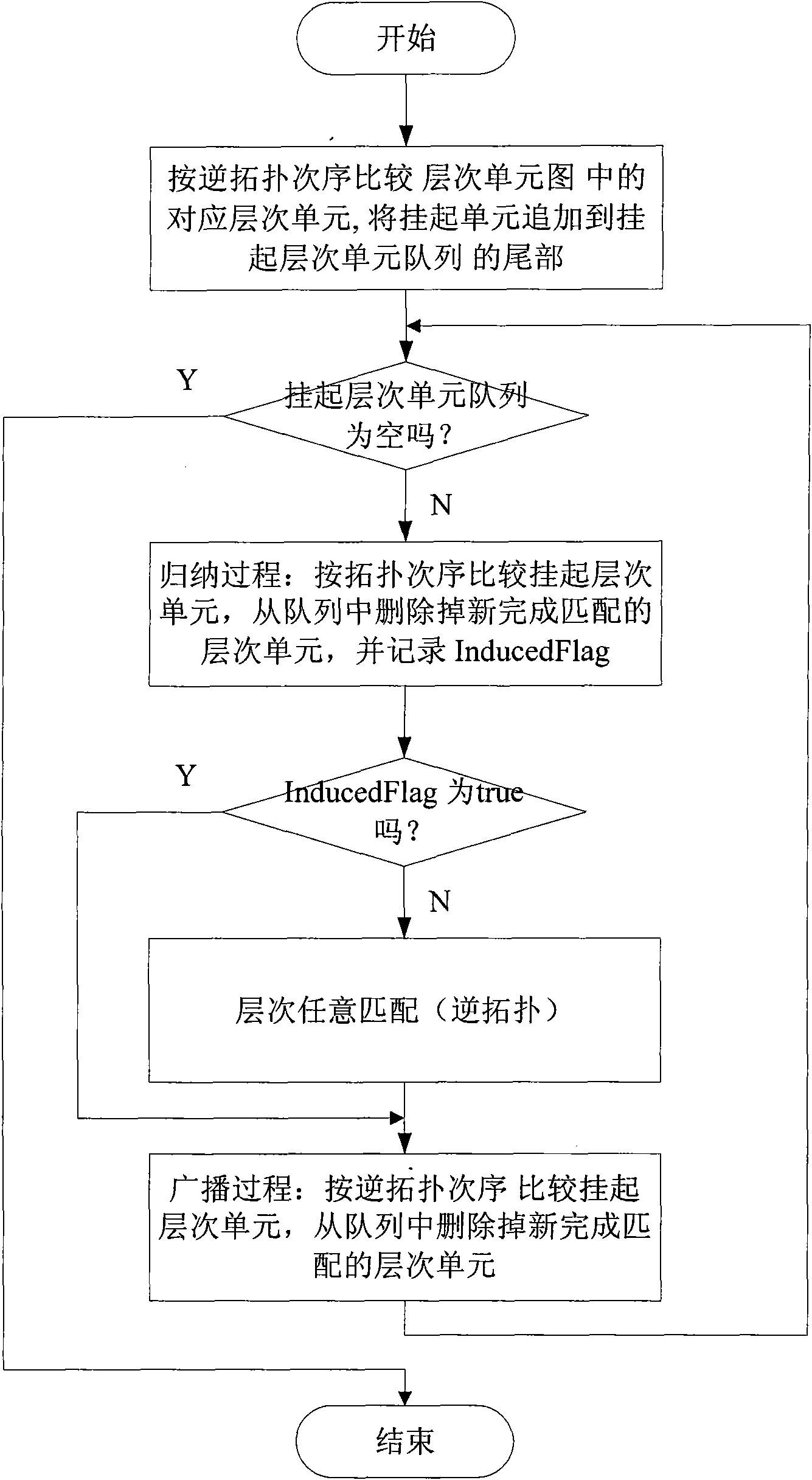

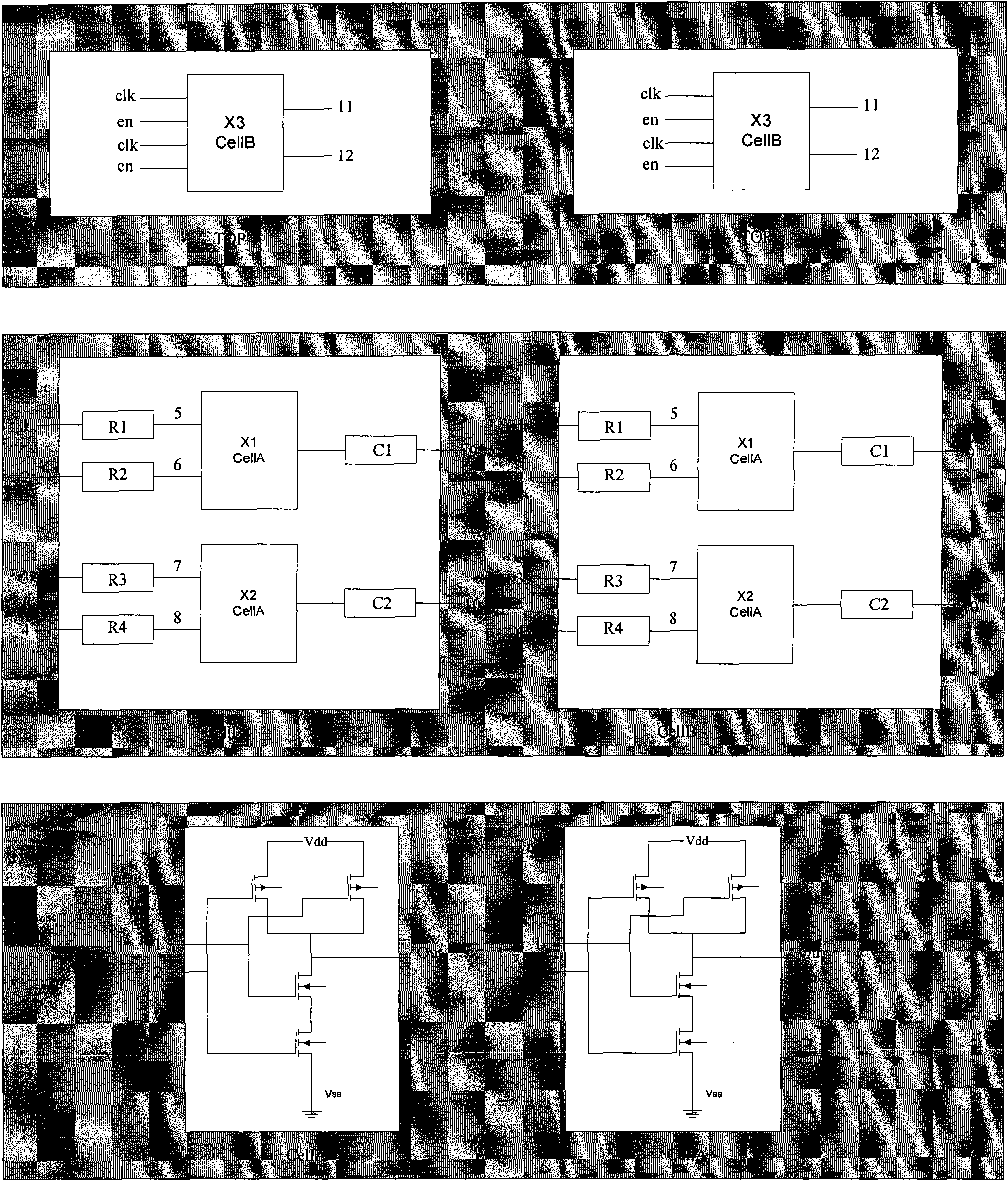

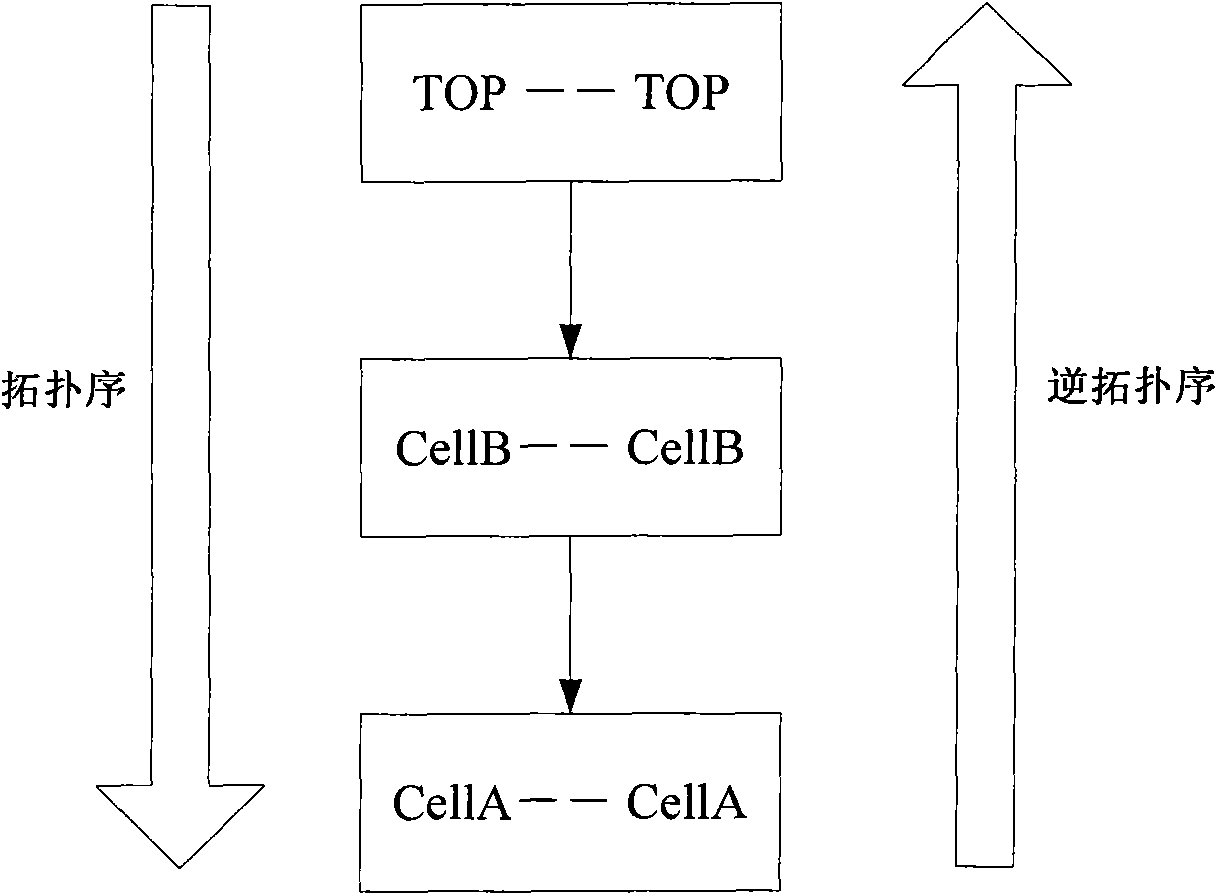

[0013] 2) Hierarchical comparison, as attached figure 1 As shown, the comparison process is as follows: ①Traverse the hierarchical units according to the reverse topological order of the hierarchy, and compare each unit in turn. The internal comparison of the unit uses the signature method to compare the internal devices, unit references and nets. If there are devices directly or indirectly connected to the PORT , unit reference or line network can not determine the matching relationship, this unit will be added to the pending queue; ② if the pending queue is not empty, then traverse the hierarchic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More