Navigating-SoC (System On Chip) simulating, verifying and debugging platform

A chip and platform technology, applied in the field of navigation SoC chip simulation, verification and debugging device platform, can solve the problems of time-consuming, difficult debugging, affecting the design progress, etc., to achieve the effect of perfect chip architecture, optimized code, efficient and reliable work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The technical solution of the present invention is further described below. The following description is only for understanding the technical solution of the present invention, and is not used to limit the scope of the present invention. The scope of protection of the present invention is based on the claims.

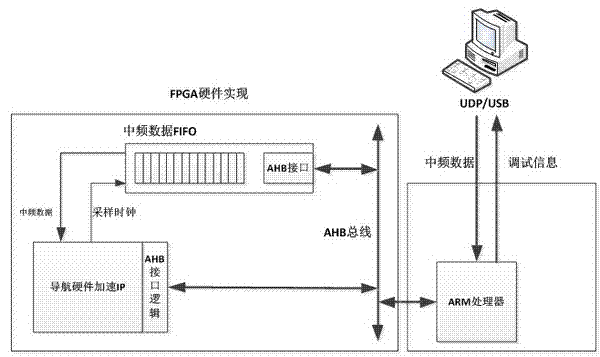

[0054] The navigation SoC chip emulation, verification and debugging platform of the present invention will be further described in detail below in conjunction with the accompanying drawings. The following descriptions are all based on the ARM processor and the AHB bus. If it is other RISC processors or other bus forms, please modify it appropriately.

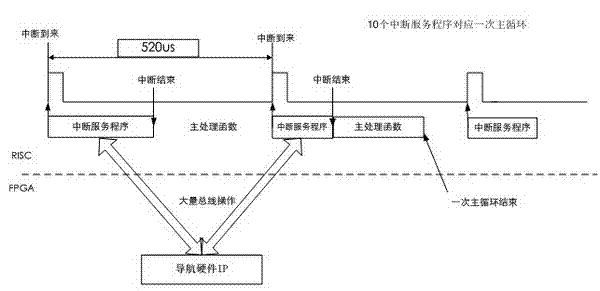

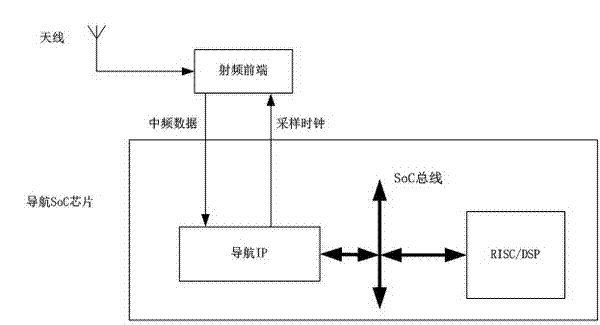

[0055] Step 1, customize the navigation SoC chip verification board. like figure 2 It is a system structure diagram of the navigation SoC chip, which directly obtains intermediate frequency data from the radio frequency front end, and these data enter the hardware acceleration IP for processing, and the RISC proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More