Nonvolatile memory element and method for manufacturing same

A technology of non-volatile storage and manufacturing method, which is applied in the field of non-volatile storage elements and can solve the problems of uneven resistance value and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

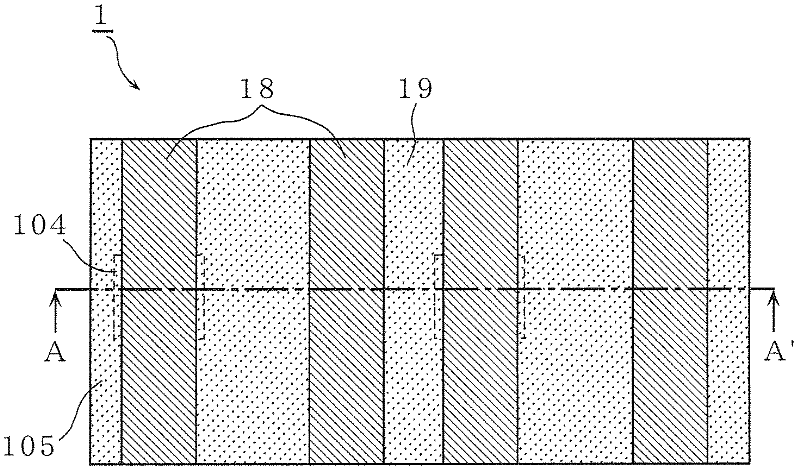

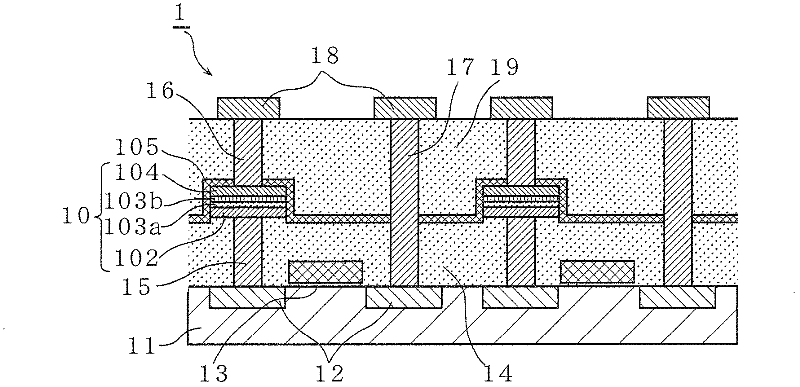

[0095] (Structure of non-volatile memory element)

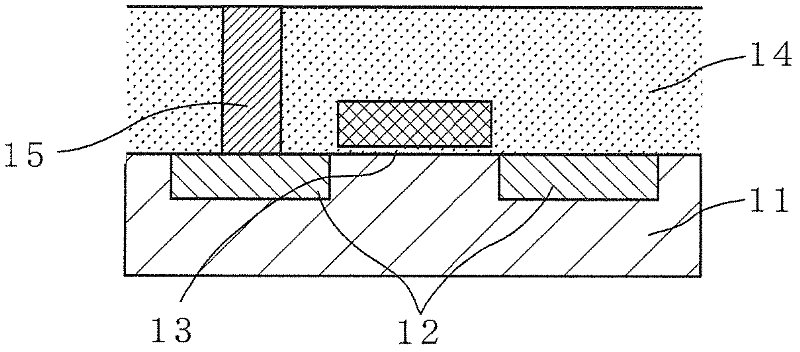

[0096] Figure 1A as well as Figure 1B It is a diagram showing the structure of the nonvolatile memory element according to Embodiment 1 of the present invention. Figure 1A represents a top view, Figure 1B Indicates looking in the direction of the arrow Figure 1A A cross-sectional view of the section of the line A-A'. Figure 1A as well as Figure 1B An example of a case where two variable resistance elements 10 are configured is shown. In this embodiment, an insulating layer that reduces stress is designed as the stress relaxation region layer 105 so as to cover at least the upper electrode layer 104 . Furthermore, the stress relaxation region layer 105 has a function of relieving stress at the interface between the upper electrode layer 104 and the second interlayer insulating layer 19 .

[0097] Figure 1B The shown nonvolatile memory element 1 has a variable resistance element 10, a silicon substrate 11, a sou...

Embodiment approach 2

[0162] (Structure of non-volatile memory element)

[0163] Figure 4A as well as Figure 4B It is a diagram showing the structure of the nonvolatile memory element according to Embodiment 2 of the present invention. Figure 4A shows a top view, Figure 4B showing looking in the direction of the arrow Figure 4A A cross-sectional view of the section of the line B-B'. in addition, Figure 4A as well as Figure 4B is an example showing a case where two nonvolatile memory elements 2 are configured.

[0164] Figure 4B The shown nonvolatile memory element 2 of this embodiment differs from the nonvolatile memory element 1 of Embodiment 1 in the structure of the stress relaxation region layer 205 . Specifically, while the pressure relaxation region layer 105 is formed of a stress-reducing plasma TEOS film or an insulating layer (porous silicon, etc.) The region layer 205 forms an air gap in which there is no insulating layer in contact with the upper electrode layer 104 . O...

Embodiment approach 3

[0182] (Structure of non-volatile memory element)

[0183] Figure 6A as well as Figure 6B It is a diagram showing the structure of the nonvolatile memory element according to Embodiment 3 of the present invention. Figure 6A shows a top view, Figure 6B showing looking in the direction of the arrow Figure 6A Cross-sectional view of the section of the line C1-C1'. in addition, Figure 6A as well as Figure 6B A case of being composed of two nonvolatile storage elements 3 is shown.

[0184] Figure 6B The illustrated nonvolatile memory element 3 of Embodiment 3 differs from the nonvolatile memory element 1 of Embodiment 1 in the structures of the stress relaxation region layer 305 and the second interlayer insulating layer 193 . Specifically, while the pressure relaxation region layer 105 is formed only between the upper electrode layer 104 and the second interlayer insulating layer 19 in Embodiment 1, in this embodiment, the pressure relaxation region layer 305 is no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More