Copper pillar bump with cobalt-containing sidewall protection

A metal protective layer, solder layer technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of high cost and interface delamination, process cost immersion tin layer solder is too cold, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

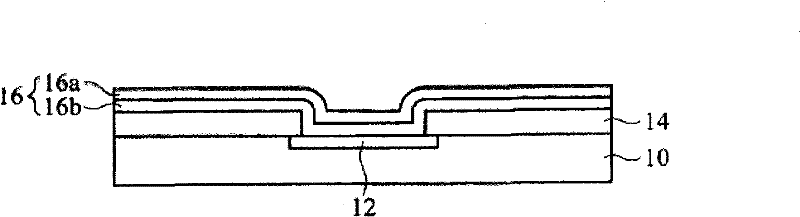

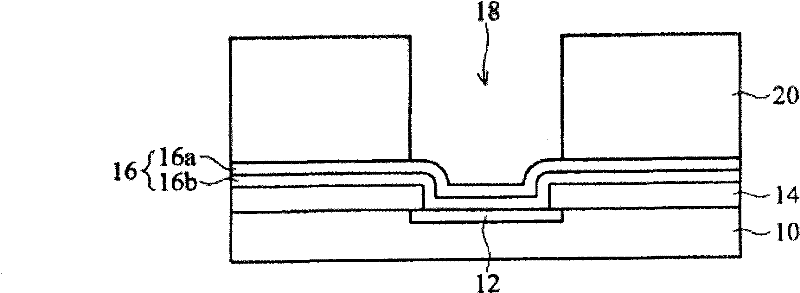

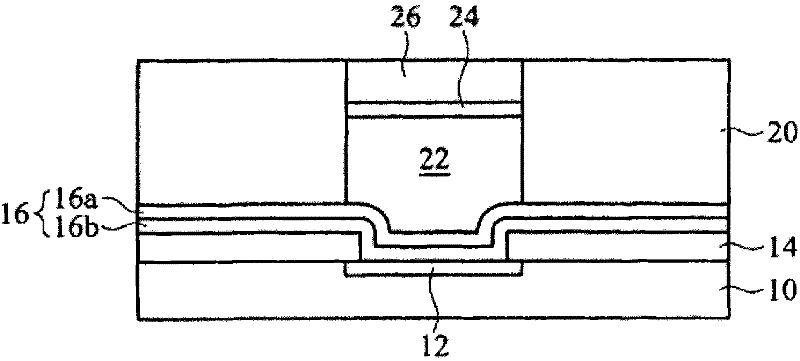

[0031] The present disclosure provides an embodiment of a formation process of a sidewall protection layer for copper pillar bump technology. As used throughout this disclosure, the term "copper pillar bump" refers to a bump structure that includes a conductive copper pillar (pillar or standoff) that includes copper or a copper alloy. Copper pillar bumps can be applied directly to electrical pads, redistribution layers on semiconductor chips for flip-chip assemblies, or other similar applications. In the following description, numerous specific details are set forth to help a more thorough understanding of the present disclosure. However, one of ordinary skill in the art will recognize that the present disclosure may be practiced without these specific details. In some instances, well-known structures and processes have not been described in detail to avoid unnecessarily obscuring the present disclosure. In references throughout the specification, "one embodiment" or "an emb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More