Clock signal loss detecting circuit and clock signal loss detecting method

A technology of clock signal and loss detection, which is applied in the electronic field to achieve the effect of improving overall performance, saving logic resources, and reducing design costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Below in conjunction with accompanying drawing and specific embodiment, further illustrate the present invention, should be understood that these embodiments are only for illustrating the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various aspects of the present invention Modifications in equivalent forms all fall within the scope defined by the appended claims of this application.

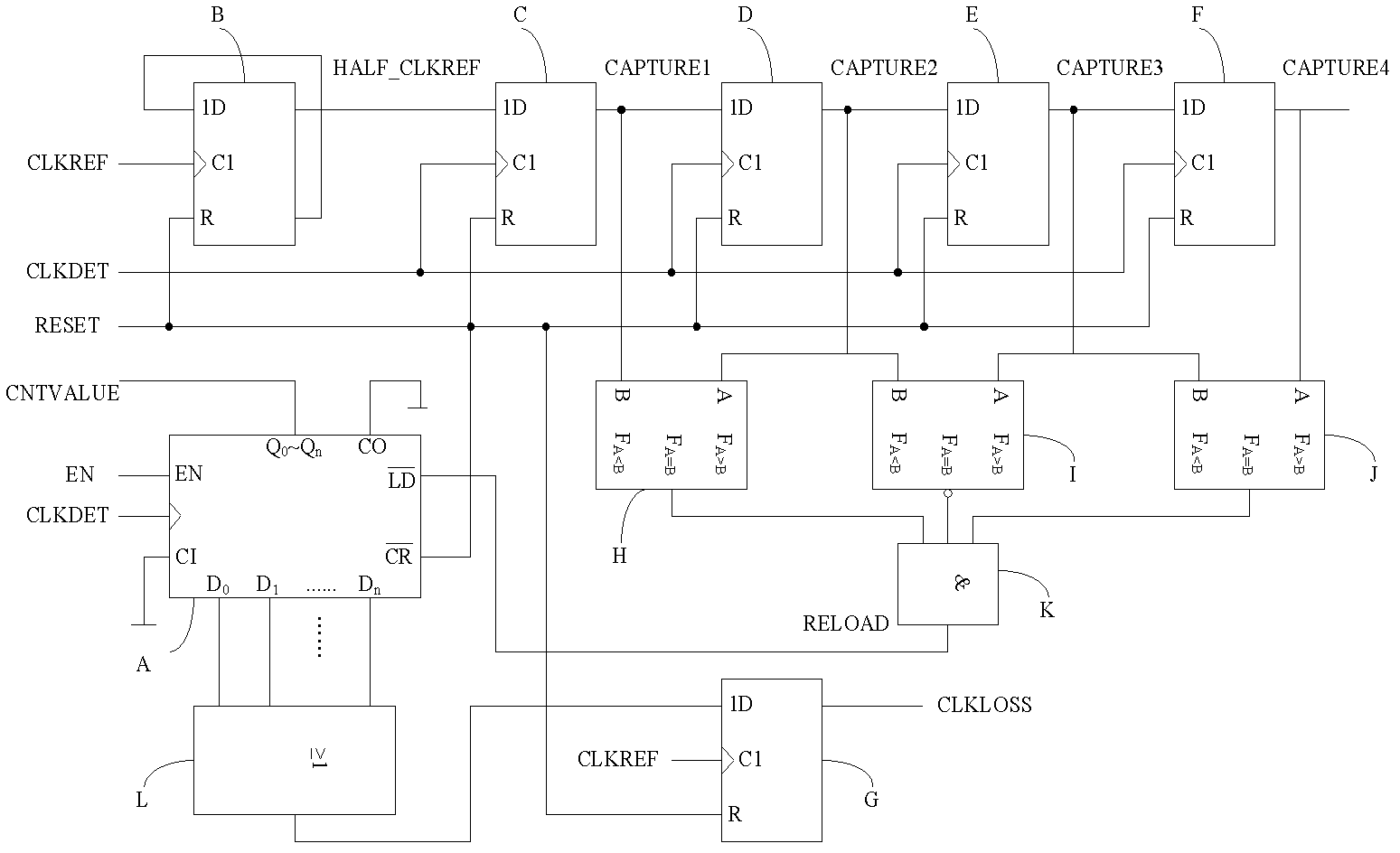

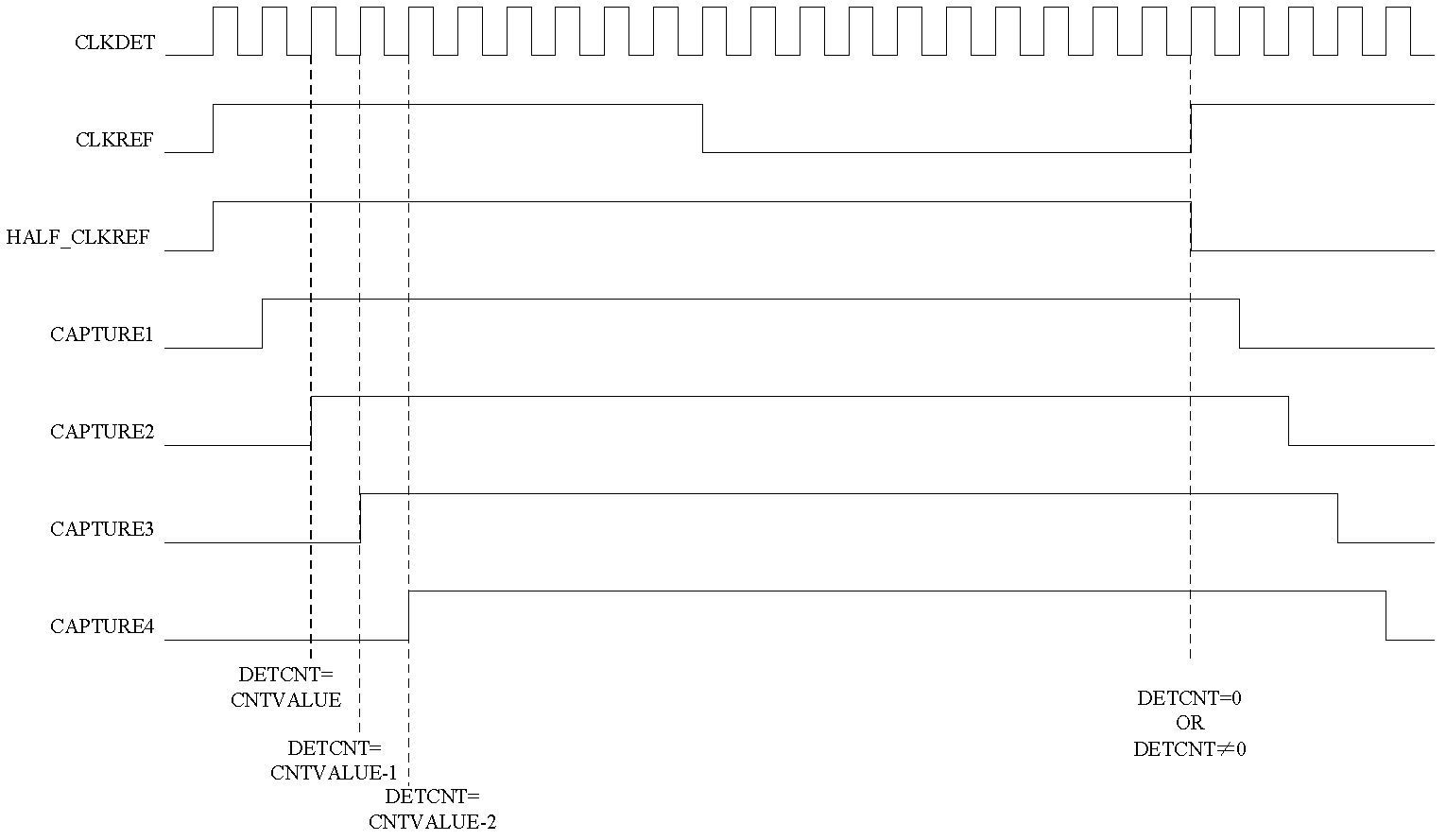

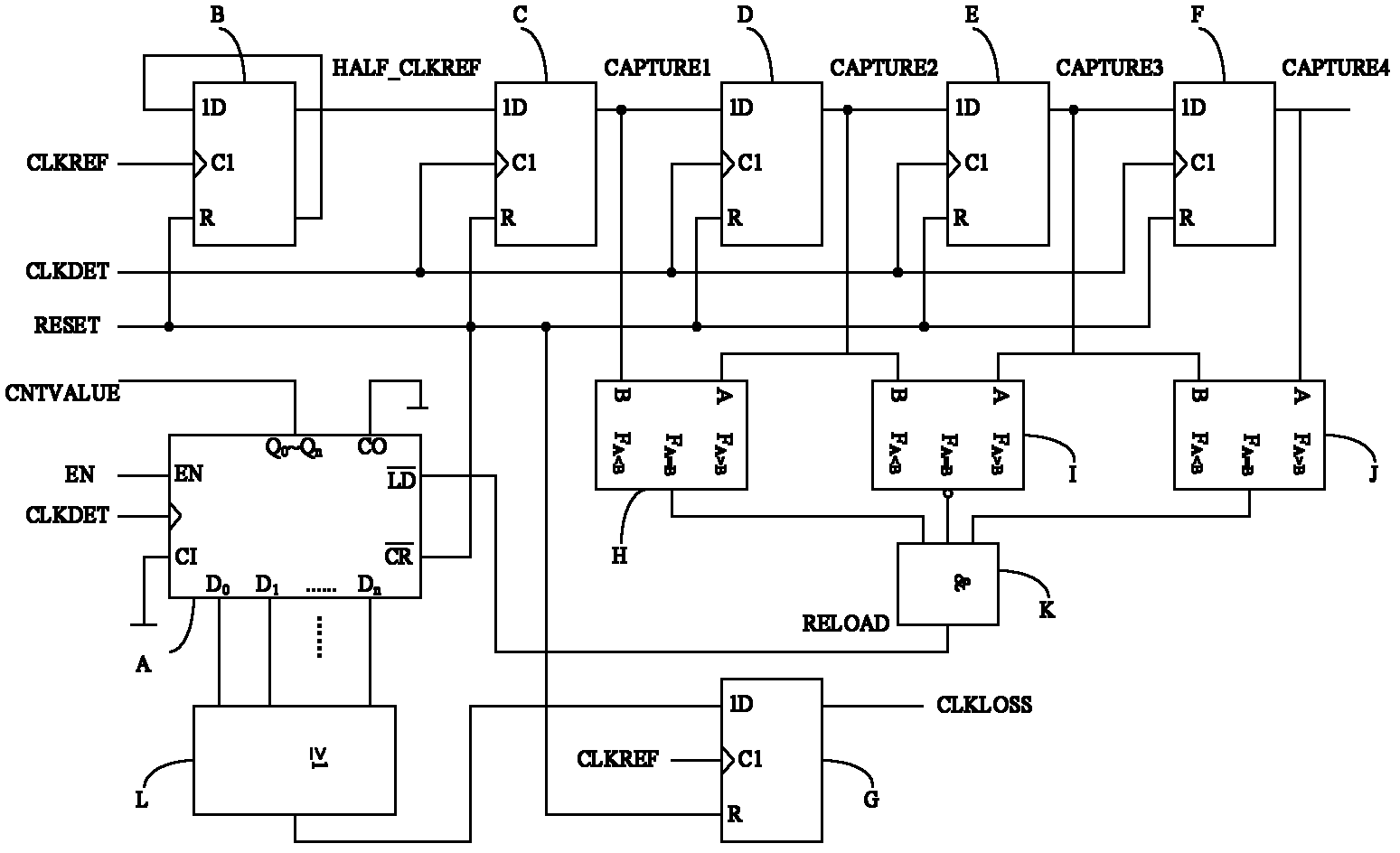

[0025] Such as figure 1 Shown: the clock signal loss detection circuit is an example implemented in language in SoC (system on chip, system on chip). The clock loss detection circuit includes an n-bit integrated counter A, six integrated flip-flops (that is, the first flip-flop B, the second flip-flop C, the third flip-flop D, the fourth flip-flop E, the fifth flip-flop F and the sixth flip-flop G), three one-bit integrated data comparators (ie, the first comparator H, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More