IP (Internet protocol) core verification system

A verification system and technology to be verified, applied in functional inspection, detection of faulty computer hardware, etc., can solve problems such as inability to debug SOC system software, prolong project development time, and inconvenient porting of test incentives, saving development time , easy to transplant, debug simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

test Embodiment 400

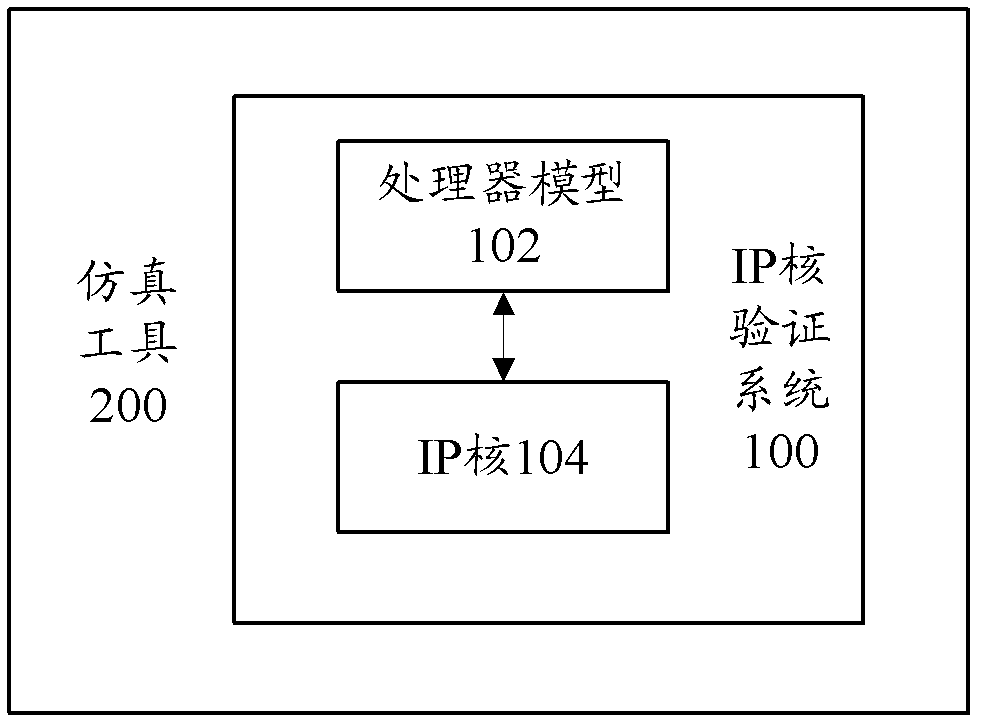

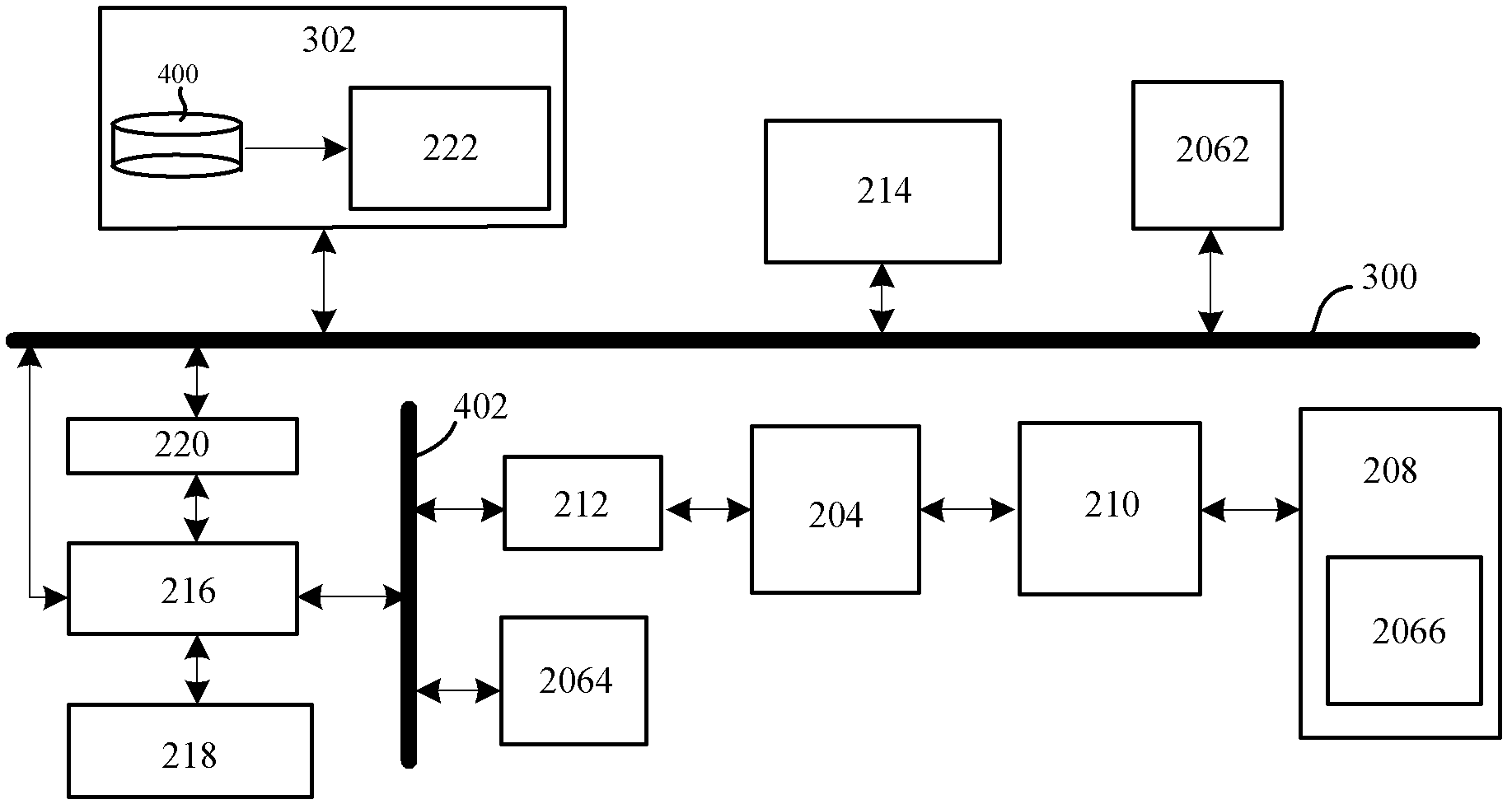

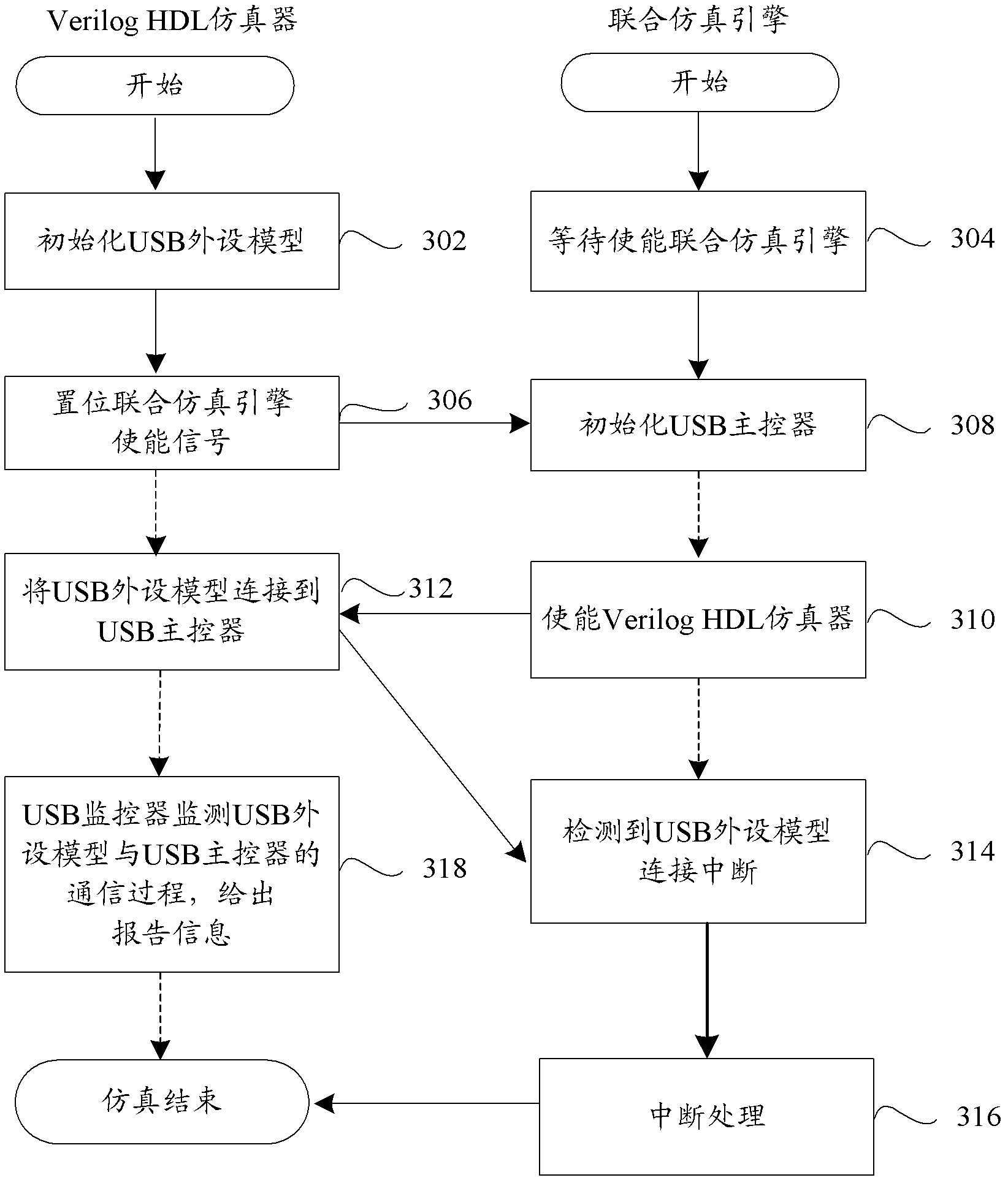

[0029] Such as figure 2 As shown, figure 2 The CPU model 222 in corresponds to figure 1 The processor model 102 in, which can run the test case 400, constitutes the joint simulation engine 302.

[0030] The processor model 102 (or the CPU model 222) is connected to the AHB system bus 300 through the AHB Master interface and transmits the bus signal to the IP core 104 to be verified through the AHB system bus 300. In this embodiment, figure 1 The IP core 104 to be verified shown in may be a USB host controller 204 (for example, a USB2.0 host controller), and the USB host controller 204 is connected to the AHB system through an AHB bridge 212 (a connector with a protocol conversion function) Bus 300.

[0031] In the above technical solution, preferably, the CPU model 222 is written in C-like language, and the test case 400 is written in C language.

[0032] In the above technical solution, preferably, the C-like language is System C language.

[0033] In the above technical solution,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com