Multiplex JTAG (Joint Test Action Group) interface-based FPGA (Field Programmable Gate Array) on-chip logic analyzer system and method

A logic analyzer and interface technology, which is applied in the direction of logic operation inspection and faulty computer hardware detection, can solve the problems of complex communication interface and large memory resources, and achieve the effect of reducing the number of output pins and reducing demand

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

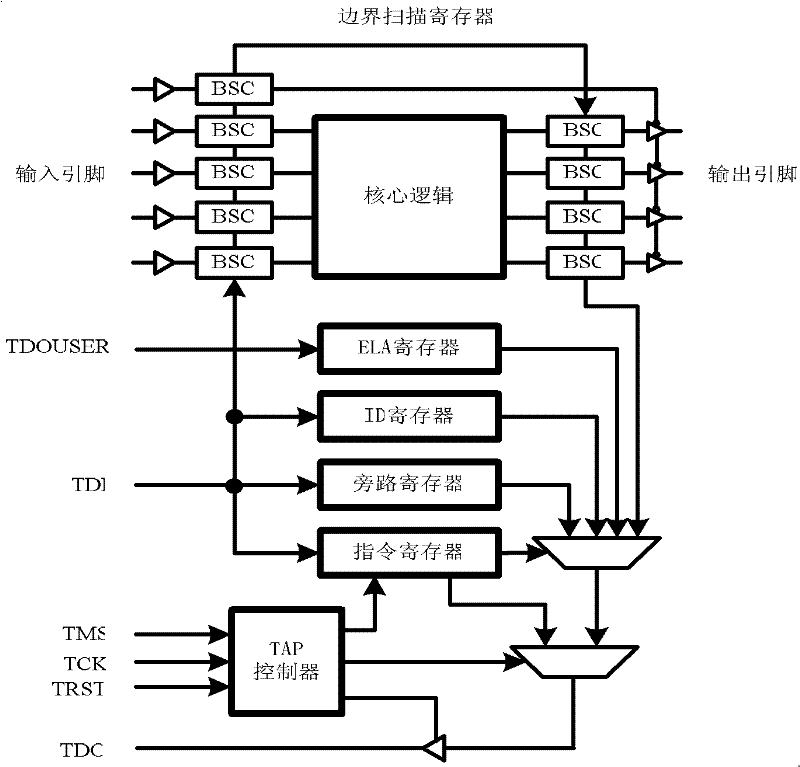

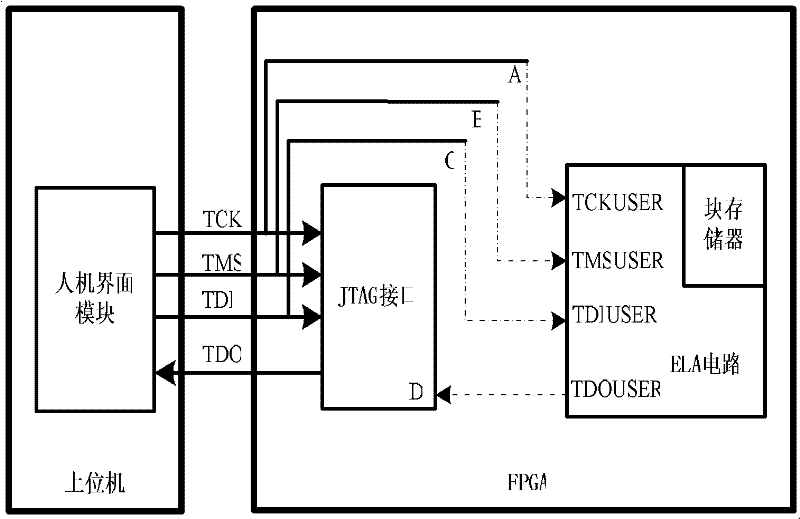

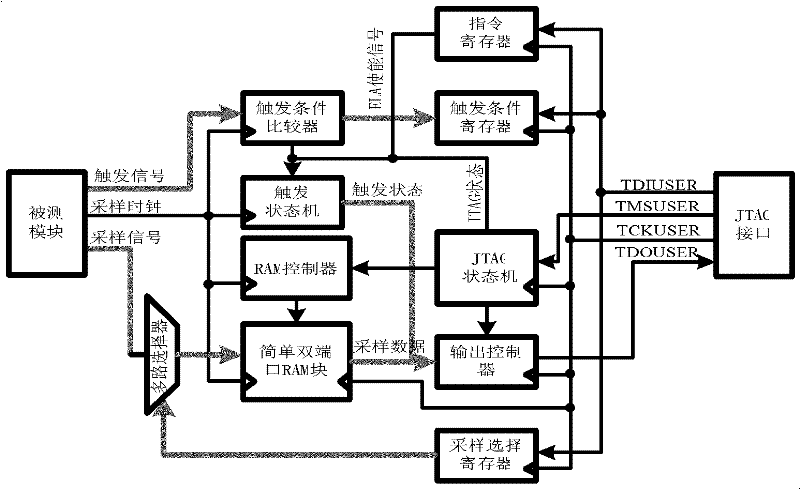

[0058] The core of a field-programmable gate array (FPGA) on-chip logic analyzer system that multiplexes the Joint Test Action Group (JTAG) interface of the present invention is to realize the Joint Test Action Group (JTAG) interface by increasing instructions and wiring constraints The multiplexing of the sampling signal is selected by using the online setting sampling selection register to reduce the demand for on-chip memory resources, and a simple and reliable data transmission protocol is designed to observe the sampling data and trigger status at the same time.

[0059] In order to enable those skilled in the art to better understand the solutions of the present invention, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0060] Such as figure 1 Shown, a kind of Field Programmable Gate Array (FPGA) on-chip logic analyzer system of the multiplexing Joint Test Action Group (JTAG) interface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More