Control method applicable to resistance changing memory resistor of nerve cell circuit

A technology of resistive memristor and control method, which is applied in the field of neuron circuits, can solve the problems of not being too small, restricting large-scale integration, complex peripheral circuits, etc., and achieves precise control of resistance floating, which is conducive to large-scale integration , fast and precise adjustment effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described through the embodiments below in conjunction with the accompanying drawings.

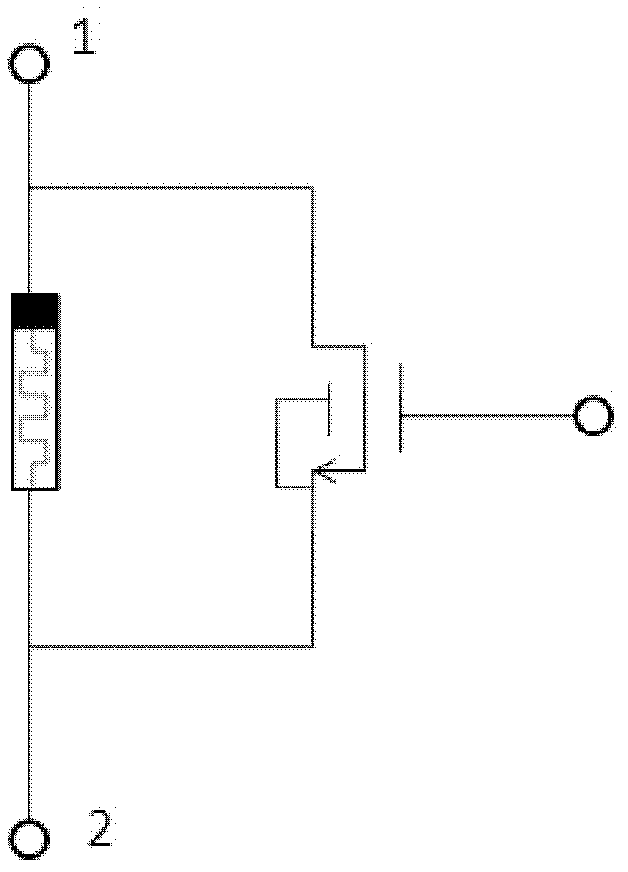

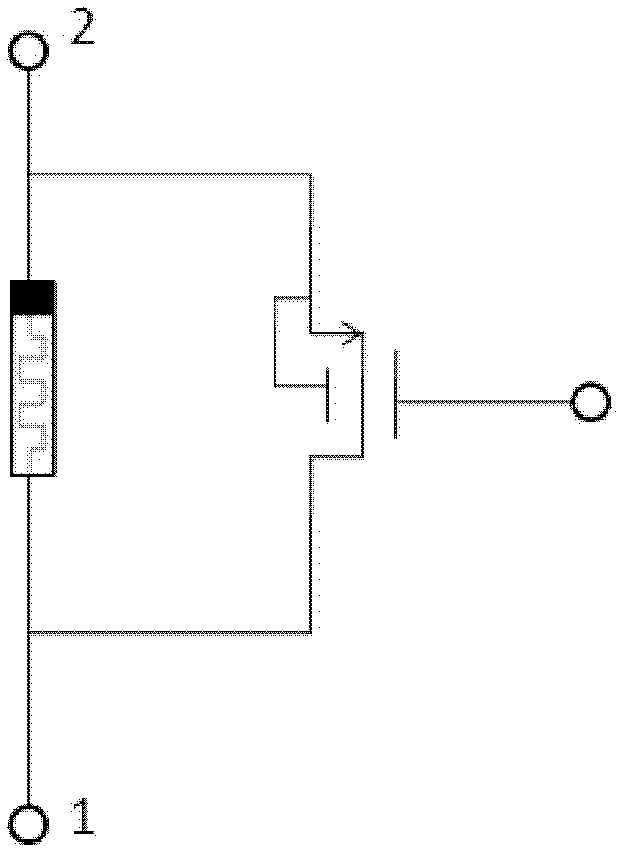

[0018] figure 1 is a schematic diagram of a parallel structure of a bipolar resistive memristor and an NMOS transistor, figure 2 It is a schematic diagram of a parallel structure of a bipolar resistive memristor and a PMOS transistor. In the figure, 1 is the drain terminal of the MOS transistor; 2 is the source terminal of the MOS transistor.

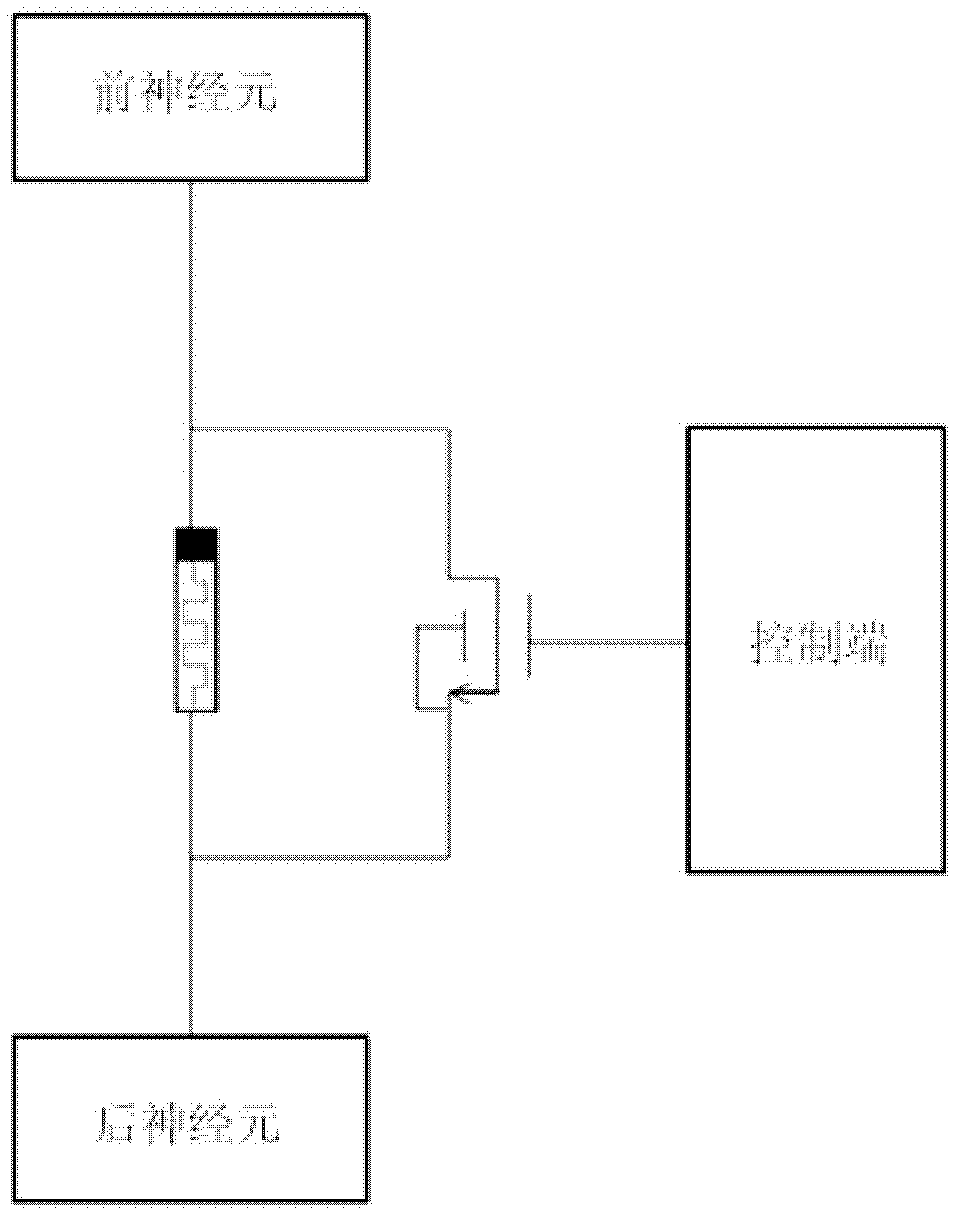

[0019] Taking the NMOS transistor as an example, the parallel structure of the bipolar resistive memristor and the NMOS transistor is connected in the neuron circuit, the positive terminal of the resistive memristor is connected to the drain terminal of the NMOS transistor, and the negative terminal is connected to the source terminal of the NMOS transistor. The drain terminal of the NMOS transistor is connected to the front neuron, the source terminal is connected to the rear neuron, and the gate termi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More