Method for implementing parallel-flash translation layer and parallel-flash translation layer system

A flash memory conversion layer, physical block technology, applied in the direction of memory address/allocation/relocation, input/output to the record carrier, etc., can solve the problem that less consideration is given to the parallel operation properties of flash memory, which restricts the performance of flash memory storage of electronic products, and is not easy to achieve. and other problems to achieve the effect of reducing complexity, improving efficiency, and reducing garbage collection time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

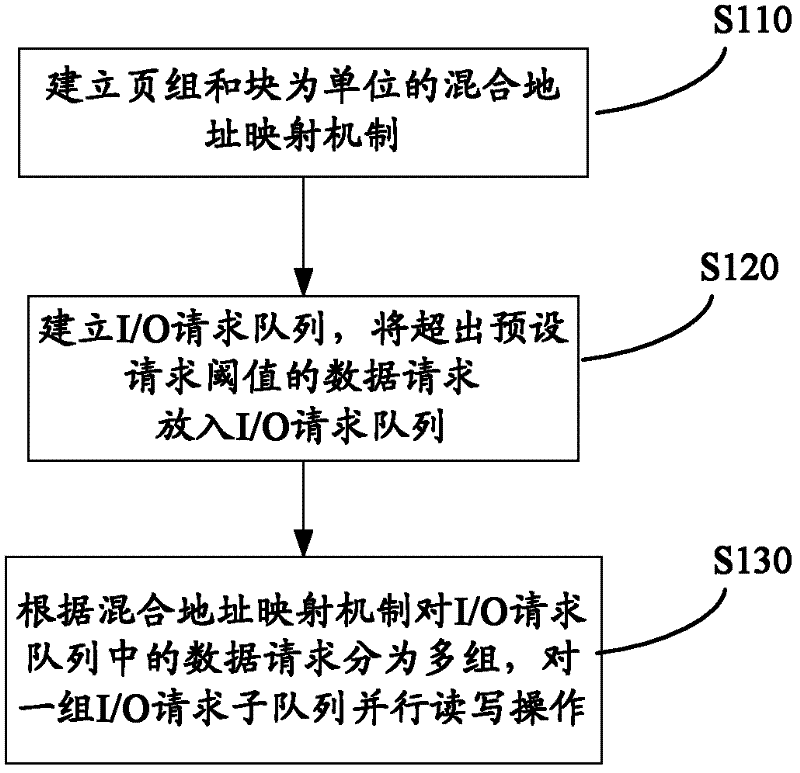

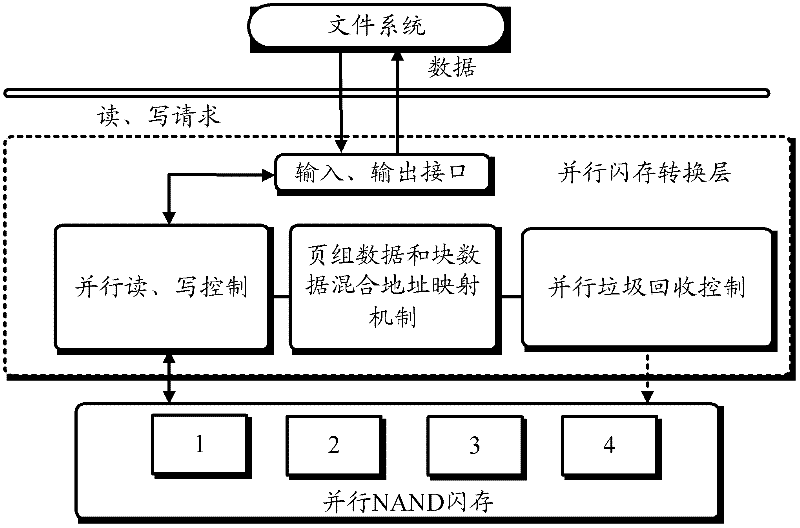

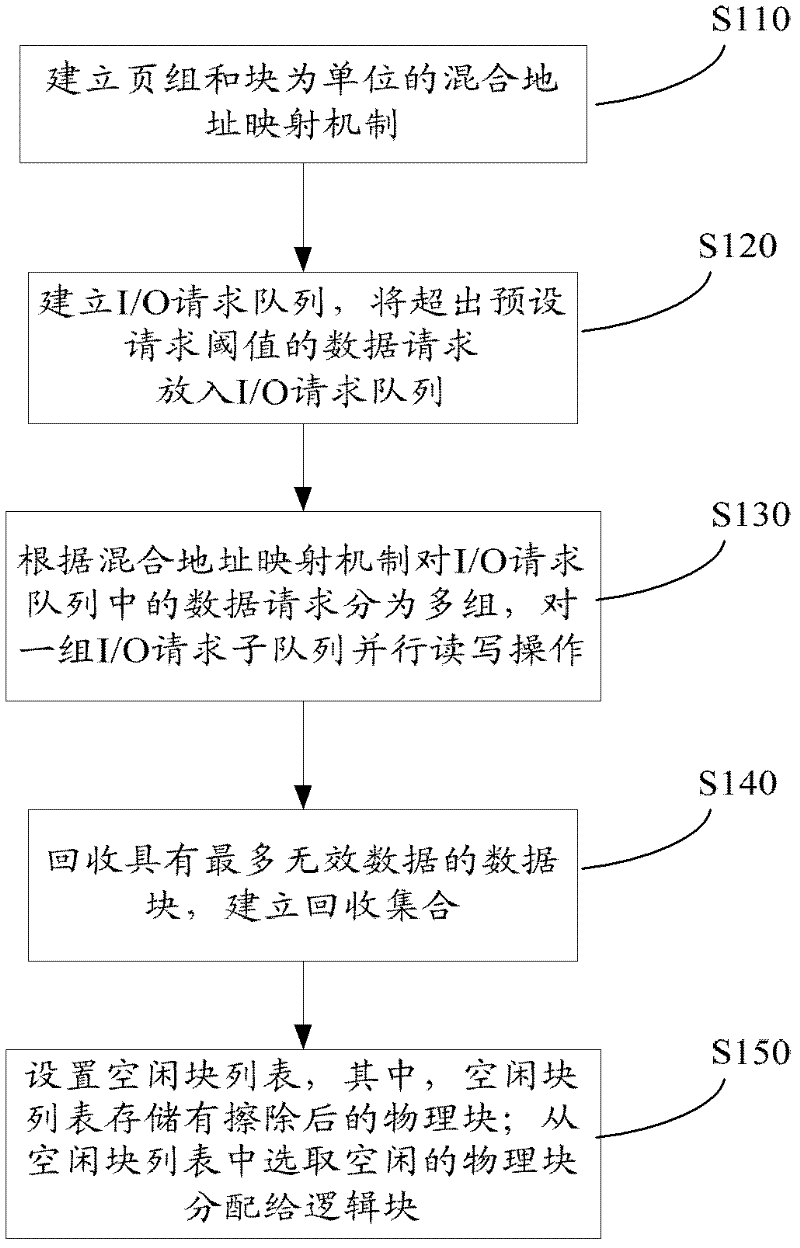

Method used

Image

Examples

Embodiment Construction

[0044] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0045]These and other aspects of embodiments of the invention will become apparent with reference to the following description and drawings. In these descriptions and drawings, some specific implementations of the embodiments of the present invention are specifically disclosed to represent some ways of implementing the principles of the embodiments of the present invention, but it should be understood that the scope of the embodiments of the present invention is not limited by this limit. On the contrary, the embodiments of the present ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More