Interrupt control method for Feiteng server

A control method and server technology, applied in the field of interrupt control of Feiteng servers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] like figure 2 As shown, taking the hardware-based interrupt at the kernel level as an example, the interrupt control method for the Feiteng server of the present invention is described in detail.

[0042] Feiteng server adopts PCI bus standard south bridge CS5536, the chip integrates hardware interface control logic such as USB controller, IDE disk controller, audio controller, RTC real-time clock and PS / 2 interface controller of keyboard and mouse. The south bridge CS5536 is connected to the PCIE bus through the bridge chip PLX8112. These internal hardware controller logic interrupt signals are all routed through the 8259A interrupt controller inside CS5536, and the bridge chip PLX8112 is responsible for converting the interrupt signal in the form of level into the interrupt signal in the form of PCIE2.0 bus message, and passing it to the processor chip. Before the method of this embodiment starts, first make the following connections and settings to the hardware of ...

Embodiment 2

[0063] Taking the interrupt generated by USB OHCI (USB Open Controller Interface) as an example, the interrupt control method for Feiteng server of the present invention is further described. Specific steps are as follows:

[0064] This interface driver supports low-speed USB devices, such as: USB mouse or USB keyboard.

[0065] This embodiment is based on the same FT server as Embodiment 1, and has the same hardware structure.

[0066] (1) if Figure 10 As shown, the USB OHCI initialization process in the Phytium multi-core server platform is as follows:

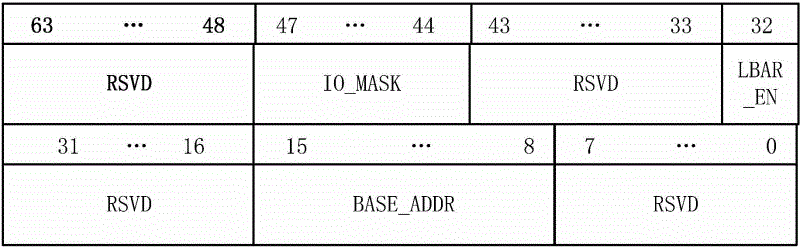

[0067] USB OHCI is a functional logic device interface integrated by CS5536. During the USB OHCI initialization process, first create the OHCI device tree node, and the subsequent USB OHCI driver will directly access the node information; then perform interrupt initialization similar to Embodiment 1; because USB OHCI uses PCI MEM space, then needs to obtain the base address of OHCI MEM, enables the access of MEM simultan...

Embodiment 3

[0073] Adopt the interrupt based on software simulation CS5536 internal equipment, verify the interrupt control method for Feiteng server of the present invention, concrete steps are as follows:

[0074] like Figure 11 As shown, in order to simulate the implementation of the present invention, an interrupt test driver is designed, which mainly includes three modules: an interrupt initialization module, a soft trigger interrupt module, and a soft trigger interrupt handler registration module.

[0075] The interrupt control method implemented by the above-mentioned interrupt test drive includes the following steps:

[0076] (1) Initialization. The initialization process of this embodiment is basically the same as that of Embodiment 1 and Embodiment 2. The only difference is that the time point of initialization is different. Embodiment 1 and Embodiment 2 complete the relevant interrupt initialization during the system kernel startup phase. The initialization of this embodiment...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More