Decomposition and marking of semiconductor device design layout in double patterning lithography

A design layout, double graphics technology, applied in the field of photomasks, can solve problems such as DPL technology troubles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

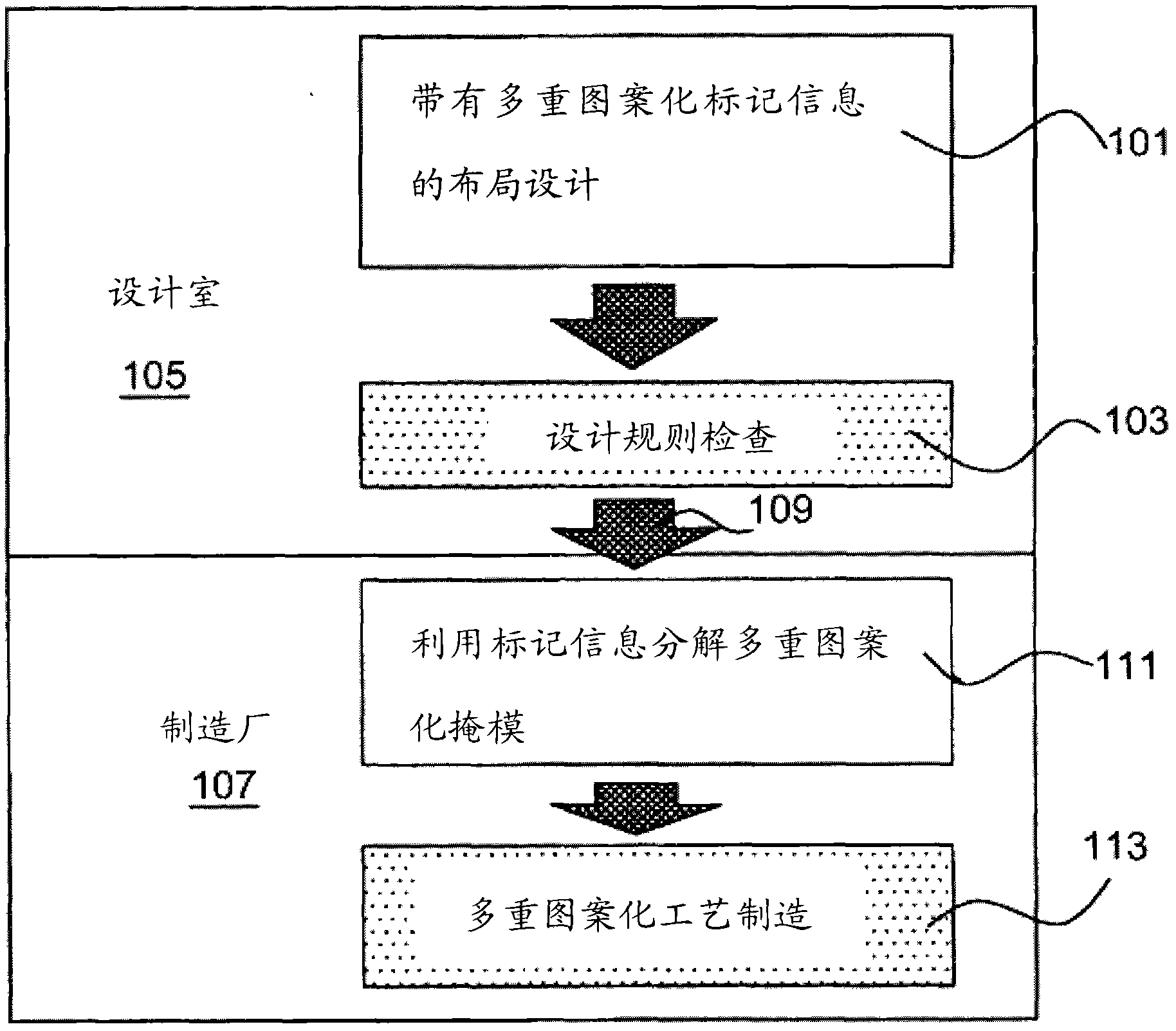

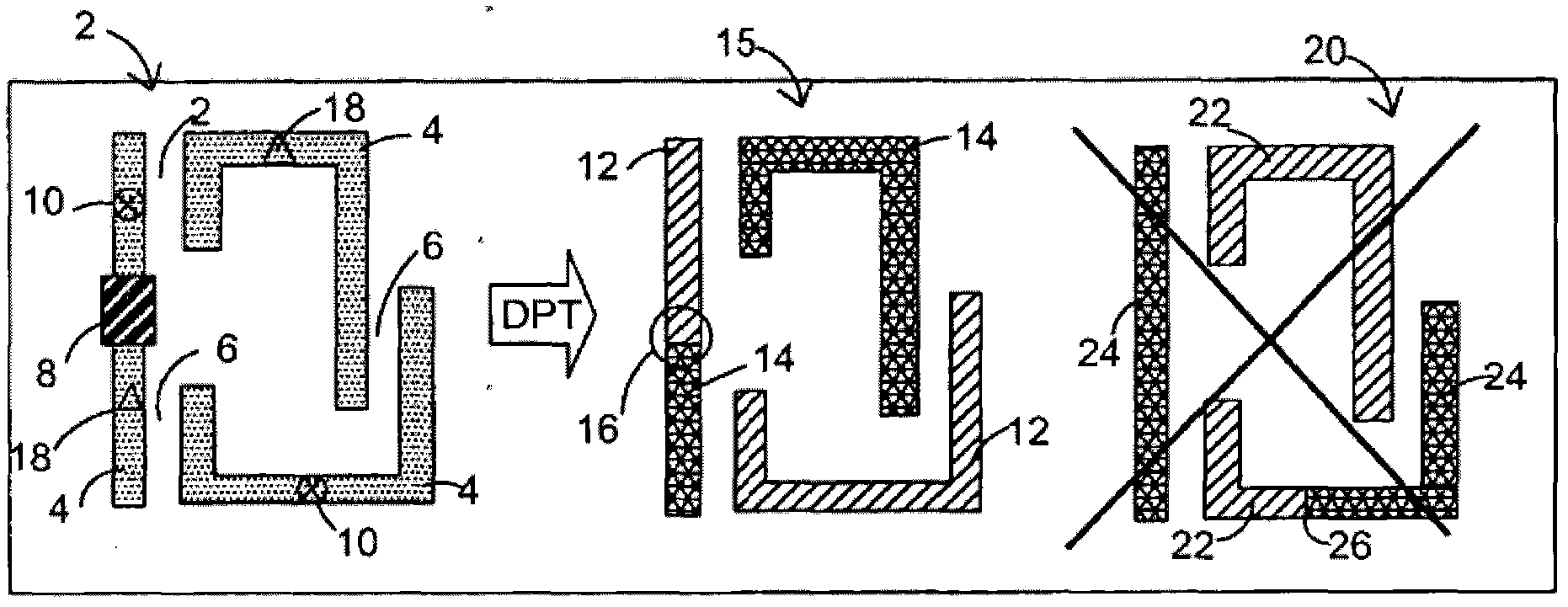

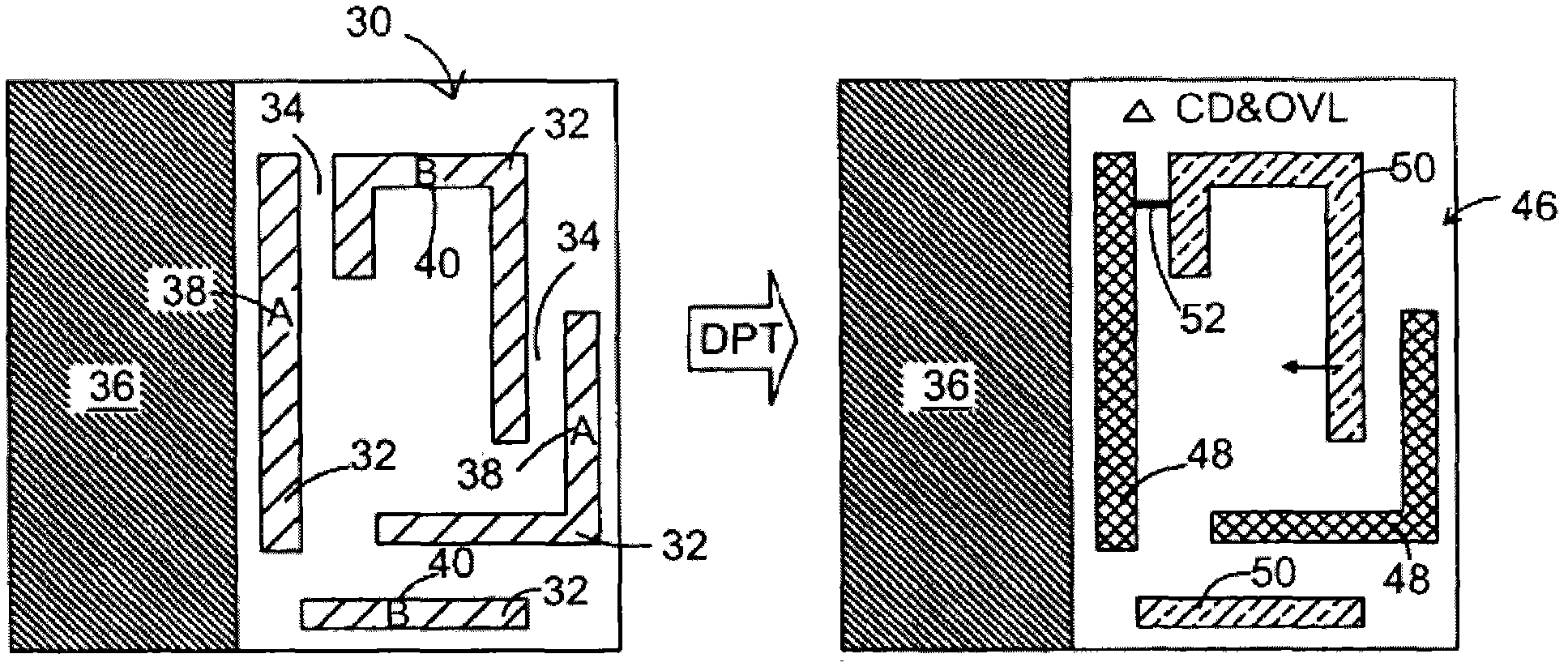

[0032] A design layout represents the exposed pattern to be formed on the semiconductor device. The design layout may be provided to the mask foundry by being stored on a computer readable electronic storage medium or other electronic file or in other suitable ways. Decompose the device components of the designed layout into two separate photomasks that are used to form specific exposure patterns. On a design level (ie, a design layout provided to a mask foundry), device components to be decomposed onto the first mask and device components to be decomposed onto the second mask are indicated. The stitching locations are also indicated on the design level (ie, the design layout provided to the mask foundry). At a stitching location, features from two different decomposed masks are stitched together to form a continuous feature. The design layout provided to the mask foundry contains markings associating components with either the first photomask or the second photomask and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More