Drive circuit structure of spatial light modulator

A technology of spatial light modulator and driving circuit, applied in instruments, static indicators, etc., can solve the problems of multi-chip area, limitation, occupation, etc., and achieve the effect of reducing chip area, increasing transmission bandwidth, and increasing data transmission rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

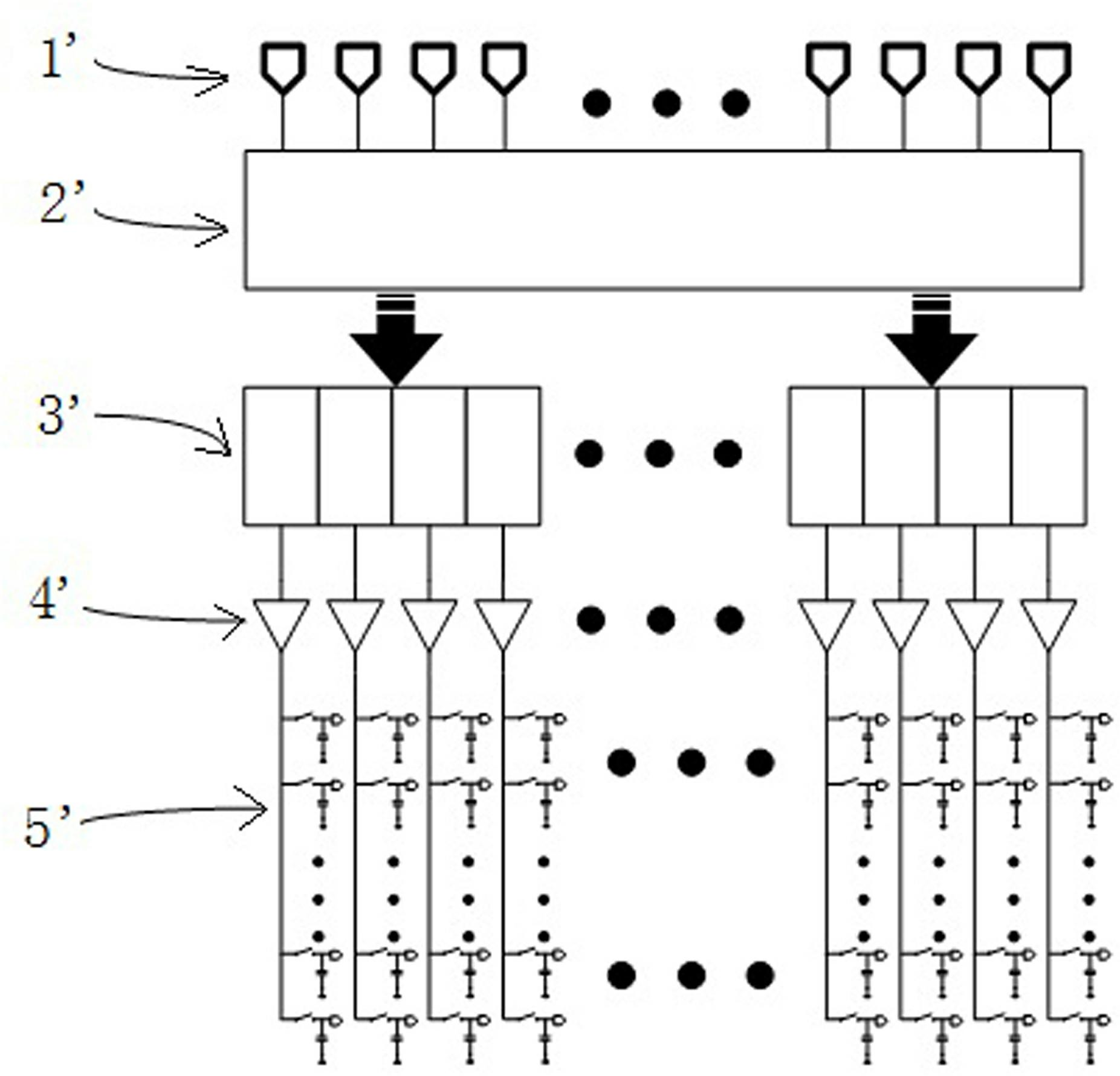

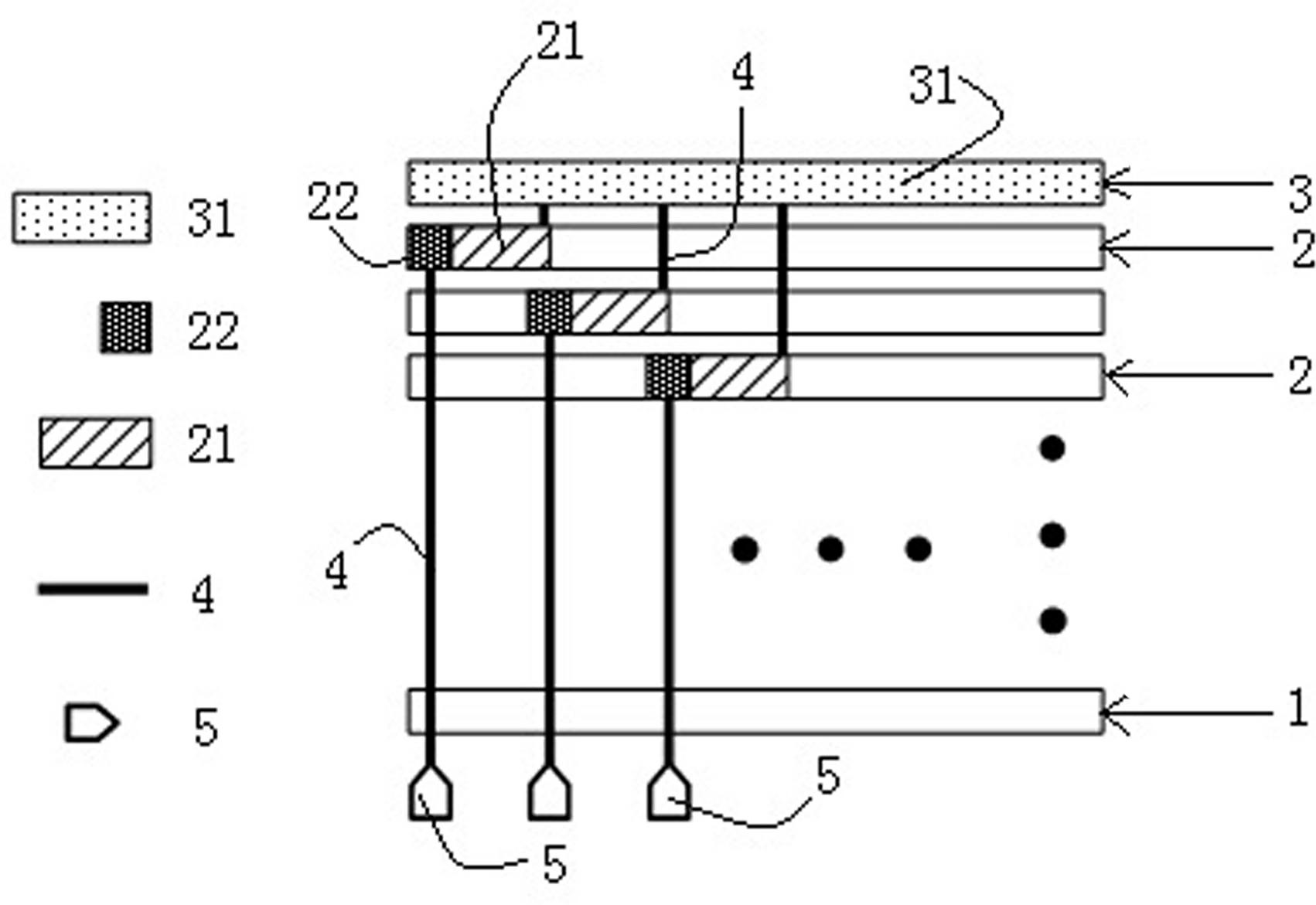

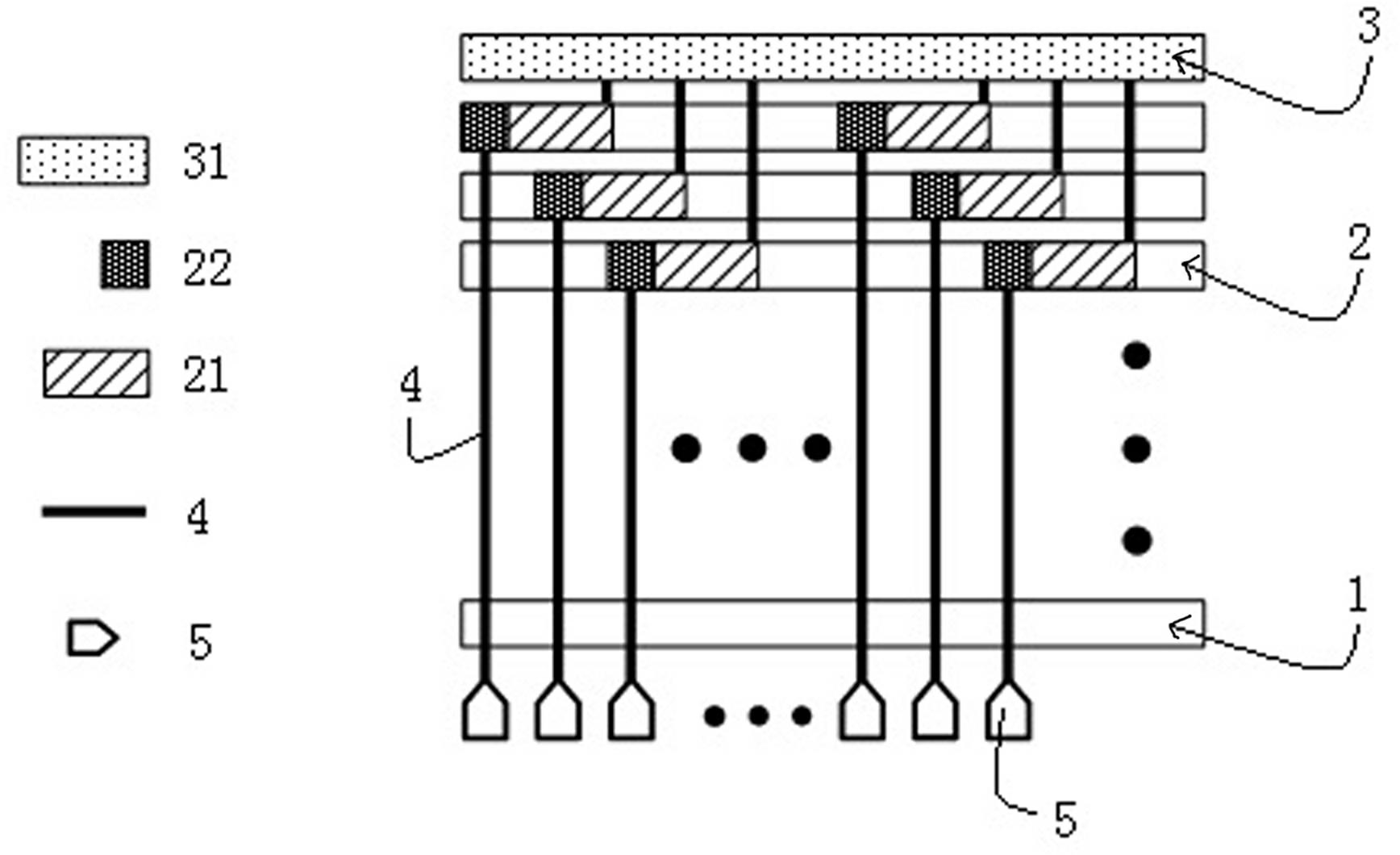

[0019] like figure 2 As shown in the figure, the drive circuit structure of the spatial light modulator in this embodiment includes a chip selection chip 1, a plurality of data register and digital-to-analog conversion chips 2 and a drive chip 3, which are arranged in sequence from bottom to top. The vertical direction is stacked layer by layer.

[0020] A pixel unit array 31 is integrated in the driving chip 3 . A plurality of digital-to-analog converters 21 distributed at intervals are integrated in the data storage and digital-to-analog replacement chip 2 (these digital-to-analog converters distributed at intervals constitute a digital-to-analog converter array), and each digital-to-analog converter 21 is adjacent to the Each is arranged with a data storage unit 22 immediately adjacent thereto. Each digital-to-analog converter 21 and the driver chip 3 are electrically connected through through silicon vias 4; and each data storage unit 22 and the chip selection chip 1 ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More