Semiconductor memory system

A memory system and semiconductor technology, applied in the direction of semiconductor devices, static memory, read-only memory, etc., to achieve the effect of suppressing bending

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Hereinafter, the semiconductor memory system according to the embodiment will be described in detail with reference to the drawings. In addition, this invention is not limited to these embodiment.

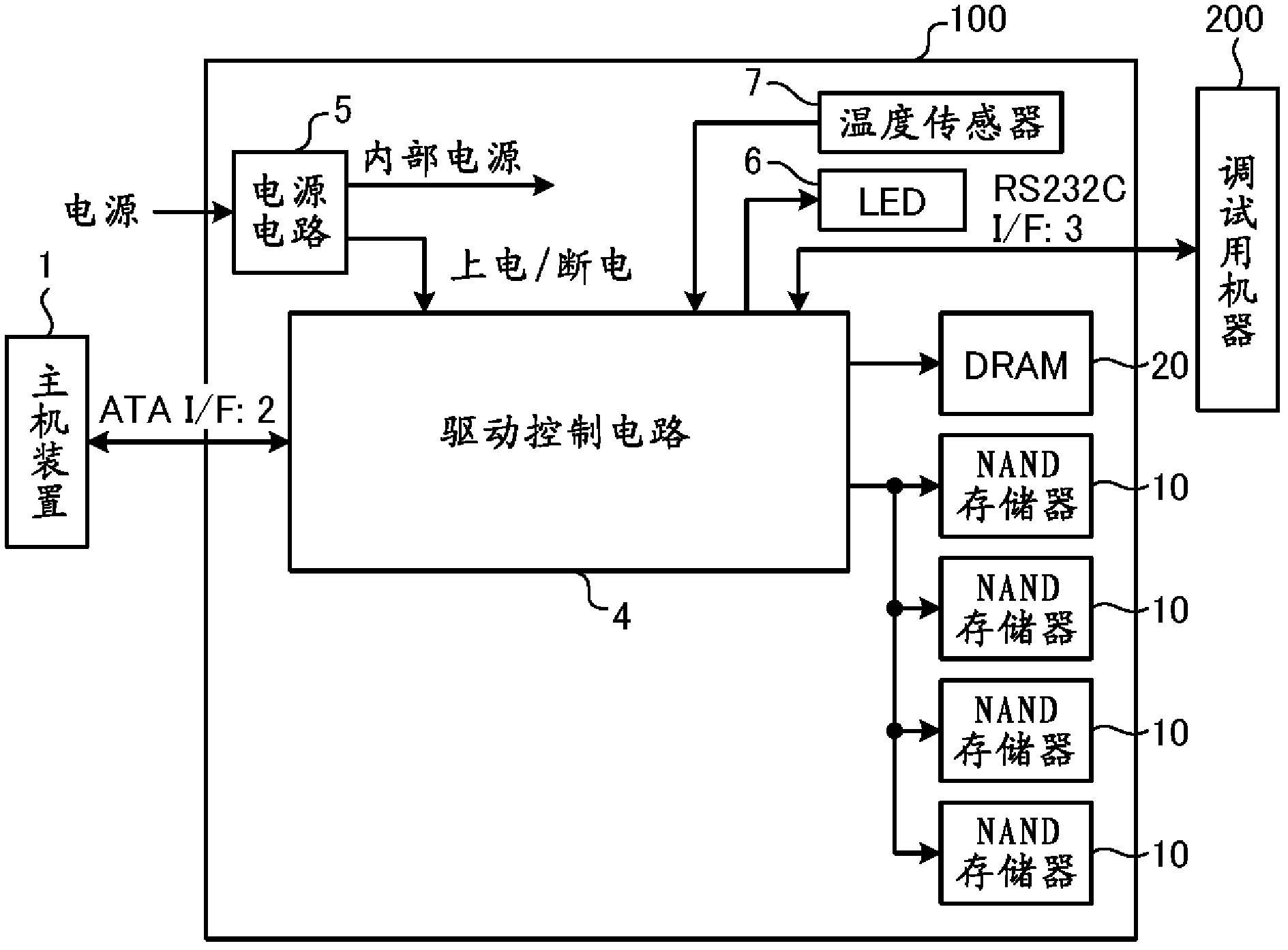

[0028] figure 1 It is a block diagram showing a configuration example of the semiconductor memory system according to the first embodiment. The semiconductor memory system 100 is connected to a host device (hereinafter, simply referred to as a host) 1 such as a personal computer or a CPU core via a memory connection interface such as a SATA interface (ATA I / F) 2 , and is used as an external memory of the host 1 . As the host 1, a CPU of a personal computer, a CPU of an imaging device such as a still camera or a video camera, and the like can be cited. Furthermore, the semiconductor memory system 100 can transmit and receive data between the debugging devices 200 via a communication interface 3 such as an RS232C interface (RS232C I / F).

[0029] The semiconductor memory sys...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com