Double-drain type CMOS magnetic field induction transistor and fabricating method thereof

A magnetic field sensing and transistor technology, which is applied in the field of CMOS magnetic field sensor transistors, can solve the problems of complex Hall plate structure, high power consumption, and unfavorable realization of large-scale magnetic field sensing array systems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

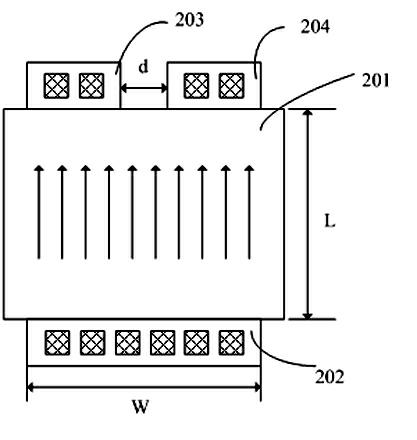

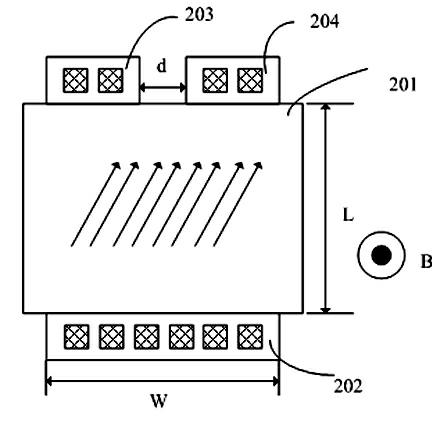

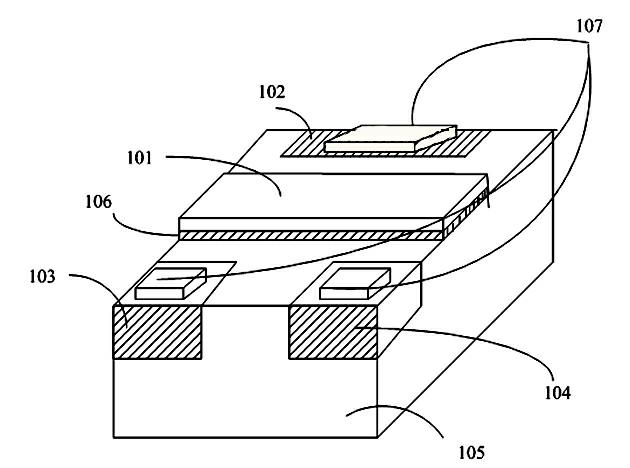

[0018] Such as figure 1 , 2 As shown, the CMOS double-drain magnetic field induction transistor of the present invention includes a P-type substrate 105, two n+ drain doped regions 103, 104, an n+ source doped region 102, a polysilicon gate 101, and silicon dioxide oxide layer 106, metal contact hole 107. First, a silicon dioxide oxide layer and a polysilicon gate are formed on a P-type substrate, and then a source n+ heavily doped region and a drain n+ heavily doped region are respectively formed on both sides of the polysilicon gate, wherein the drain n+ is heavily doped Divide into two identical areas separated by a certain distance.

[0019] The specific manufacturing process of the CMOS double-drain magnetic field induction transistor is described as follows:

[0020] (1) growing a silicon dioxide layer 106 on the P-type substrate 105;

[0021] (2) Removing the silicon dioxide on the diffusion windows of the source n+ doped region 102 and the drain n+ doped regions 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More