Virtual memory system, virtual memory controlling method, and program

A technology of virtual storage and storage, which is applied to storage systems, instruments, and memory architecture access/allocation, etc. It can solve problems such as system performance deterioration and achieve the effect of avoiding write restrictions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

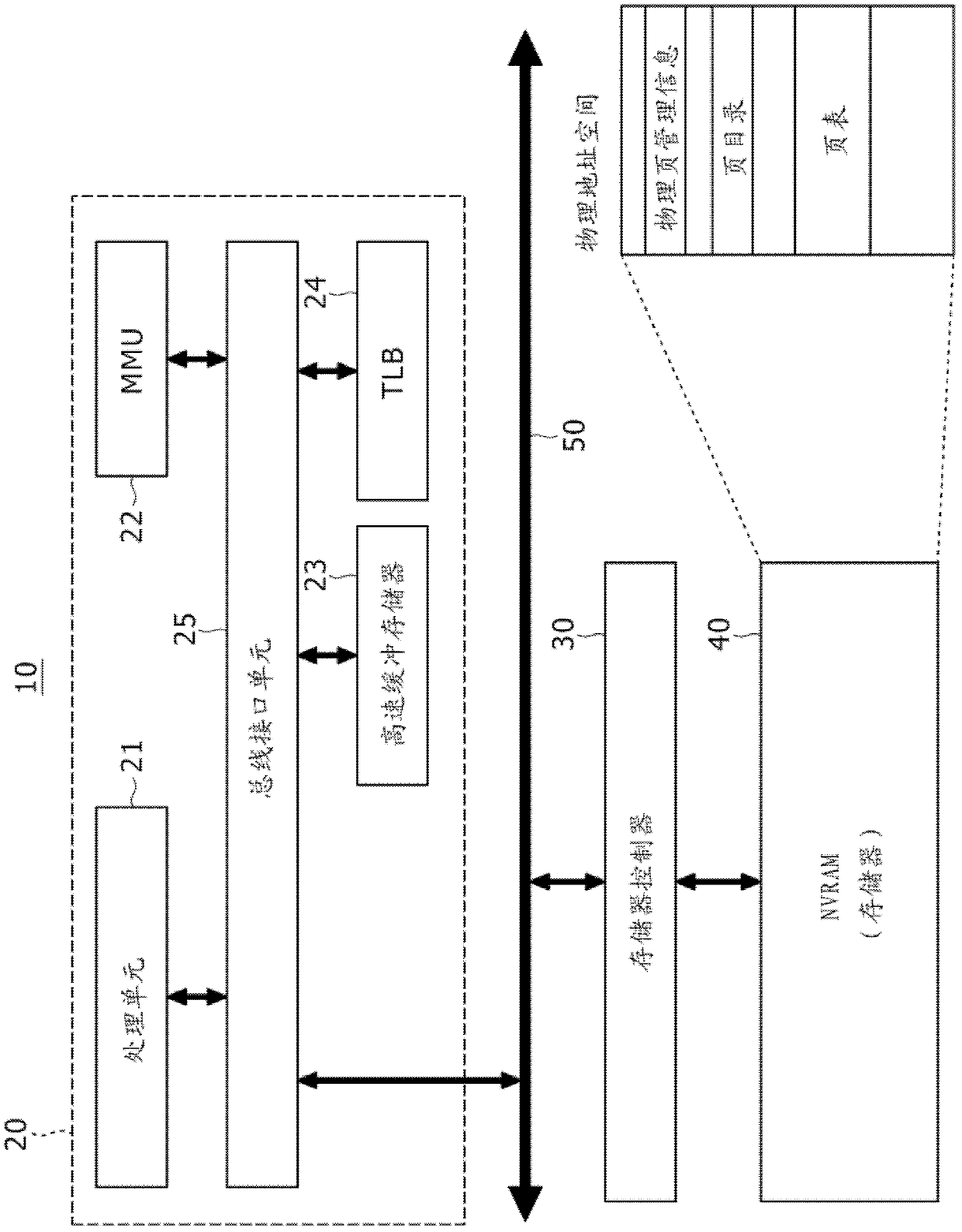

[0052] figure 1 is a schematic diagram showing the configuration of a virtual memory system to which a nonvolatile random access memory (NVRAM) according to the first embodiment of the present disclosure is applied.

[0053] The present virtual memory system 10 includes a CPU 20 as a virtual memory control section, a memory controller 30 , a nonvolatile random access memory (NVRAM) 40 and a system bus 50 .

[0054] The nonvolatile random access memory 40 is randomly accessible, and has an upper limit to the number of times of rewriting. Under the control of the CPU 20, the physical address space of the nonvolatile RAM 40 is accessed through the virtual address space.

[0055] The CPU 20 includes a processor unit 21 , a memory management unit (MMU) 22 and a cache memory 23 .

[0056] The CPU 20 also includes a translation look-aside buffer (TLB) 24 and a bus interface unit 25 .

[0057] The virtual memory system 10 according to the present embodiment is formed as a virtual m...

no. 2 example

[0191] Figure 14 is a schematic diagram showing the configuration of a virtual memory system to which a nonvolatile random access memory (NVRAM) according to a second embodiment of the present disclosure is applied.

[0192] The virtual memory system 10A according to the second embodiment of the present disclosure is different from the virtual memory system 10 according to the first embodiment in the following respects.

[0193] In the virtual memory system 10A, in addition to the nonvolatile random access memory 40, a volatile random access memory 40A such as DRAM is also connected to the memory controller 30A.

[0194] as above reference Figure 9 as well as Figure 10A with Figure 10B As described, in this embodiment, an NVM bit is added to each entry of the page directory table PDT11 and the page table PT11.

[0195] The virtual memory systems 10 and 10A according to the first and second embodiments of the present disclosure are compatible with both the nonvolatile r...

no. 3 example

[0214] Figure 18 is a schematic diagram showing the configuration of a virtual memory system to which a nonvolatile random access memory (NVRAM) according to a third embodiment of the present disclosure is applied.

[0215] The virtual memory system 10B according to the third embodiment of the present disclosure is different from the virtual memory system 10 according to the first embodiment in that the ECC circuit 26 is provided in the CPU 20A as a virtual memory control section.

[0216] Data read from the nonvolatile random access memory 40 is transferred to the cache memory 23 . In the case of data having ECC added thereto, the data after error detection and error correction by the ECC circuit 26 is transferred to the cache memory 23 .

[0217] Also, at the time of writing, the data in the cache memory 23 is transferred to the nonvolatile random access memory 40 through the memory controller 30 . This data is written with an ECC code attached thereto.

[0218] Incident...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More