Dual-feedback power supply clamp used for on-chip electrostatic discharge protection

An electrostatic discharge, dual feedback technology, applied in emergency protection circuit devices, emergency protection circuit devices, electrical components, etc. for limiting overcurrent/overvoltage, which can solve the problem of wasting chip area, large power consumption, and not easy to fully guarantee The problem of complete power and fault of electrostatic discharge pulse is achieved to suppress false triggering, prolong conduction time, reduce occupied area and leakage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

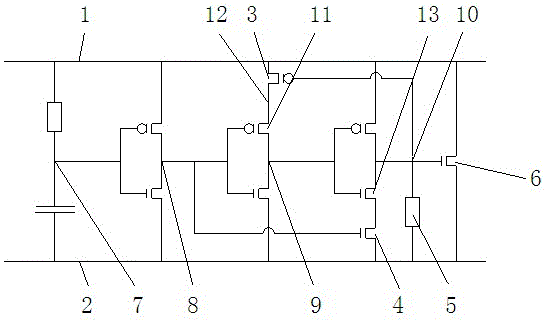

[0017] In the first embodiment of the present invention, please continue to refer to figure 1 shown. When the electrostatic discharge (ESD) pulse occurs in the initial stage, since the RC time constant is smaller than the pulse voltage rise rate, the voltage of Filter7 remains low, and the voltage of INV1OUT8 is high. At the same time, both the P-type cascode transistor 3 and the N-type cascode transistor 4 are in the conducting state, the voltage of INV2OUT9 is at a low potential, and the voltage of the gate 10 is at a high potential, so that the voltage of the large-size transistor 6 is in a fully conducting state, providing static electricity Release the current channel.

[0018] In the second embodiment of the present invention, when the RC time constant is reached, the voltage of Filter7 rises to a high potential, the voltage of INV1OUT8 is a low potential, the P-type cascode transistor 3 and the N-type cascade transistor 4 are in the cut-off state, and MP2 11 conducts ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More