Power on delay circuit and method

A delay circuit and resistor technology, applied in electrical components, electronic switches, pulse technology, etc., can solve the problem of whitening of the edge of the display panel when it is turned on, and achieve the goal of reducing the off time, prolonging the on time and prolonging the service life Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

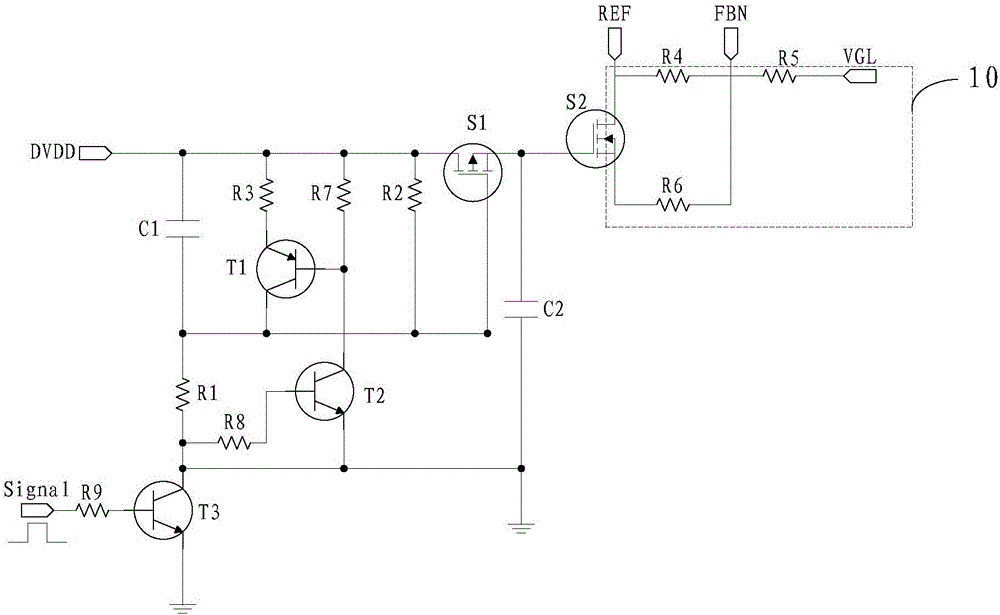

[0054] refer to figure 1 , shows a power-on delay circuit according to an embodiment of the present invention. The delay circuit includes a first switch tube S1, a second switch tube S2, a first capacitor C1 and a first resistor R1;

[0055] The source of the first switching tube S1 is connected to the power supply DVDD;

[0056] The first capacitor C1 is connected between the gate and the source of the first switching transistor S1;

[0057] The gate of the second switching tube S2 is connected to the drain of the first switching tube S1, and the drain and source of the second switching tube S2 are connected to the conversion circuit 10 for output voltage of the pixel off signal;

[0058] The first resistor R1 is connected between the ground terminal and the gate of the first switch S1, and the first resistor R1 is connected in series with the first capacitor C1;

[0059] The power supply DVDD charges the first capacitor C1 through the first resistor R1, the first switch t...

Embodiment 2

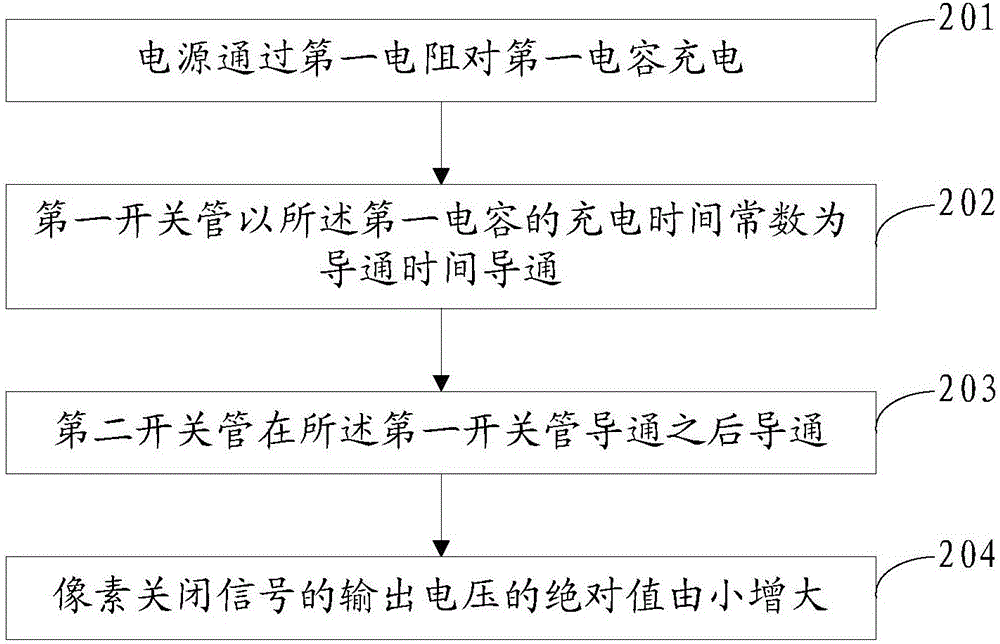

[0094] refer to figure 2 , shows a flowchart of steps of a method for delaying power-on according to an embodiment of the present invention. The method is applied to the power-on delay circuit described in Embodiment 1, including:

[0095] Step 201, the power supply charges the first capacitor through the first resistor.

[0096] In this embodiment, the power supply DVDD, the first capacitor C1, the first resistor R1 and the ground terminal are connected in series to form a charging path, and the power supply DVDD charges the first capacitor C1 through the first resistor R1.

[0097] Step 202, the first switch tube is turned on with the charging time constant of the first capacitor as the conduction time.

[0098]In this embodiment, the first capacitor C1 is connected between the gate and the source of the first switching tube S1, the power supply DVDD charges the first capacitor C1 through the first resistor R1, and the power of the first capacitor C1 gradually increases, ...

Embodiment 3

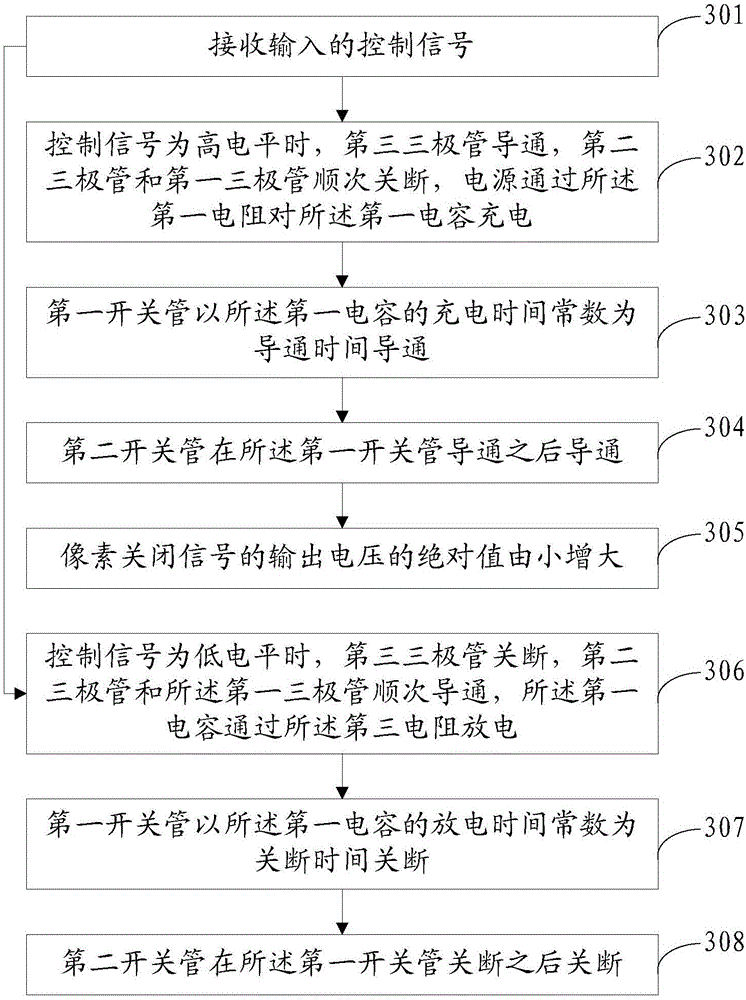

[0105] refer to image 3 , shows a flowchart of steps of a method for delaying power-on according to an embodiment of the present invention. The method is applied to the power-on delay circuit described in Embodiment 1, including:

[0106] Step 301, receiving an input control signal.

[0107] In this embodiment, the first triode T1 , the second triode T2 and the third triode T3 form a turn-off branch, so that the first capacitor C1 can be quickly discharged when the first switch S1 is turned off. The first transistor T1 can be a PNP transistor, and the turn-on threshold voltage of the PNP transistor is negative. The second transistor T2 and the third transistor T3 can be NPN transistors, and the turn-on threshold voltage of the NPN transistor is positive.

[0108] The base of the third transistor T3 is connected to the control signal terminal to receive the input control signal.

[0109] Step 302, when the control signal is at a high level, the third triode is turned on, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More