Process for forming an epitaxial layer

An epitaxial layer and process technology, applied in the field of microelectronics, can solve the problems of difficult realization and expensive hard mask, and achieve the effect of simplifying control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

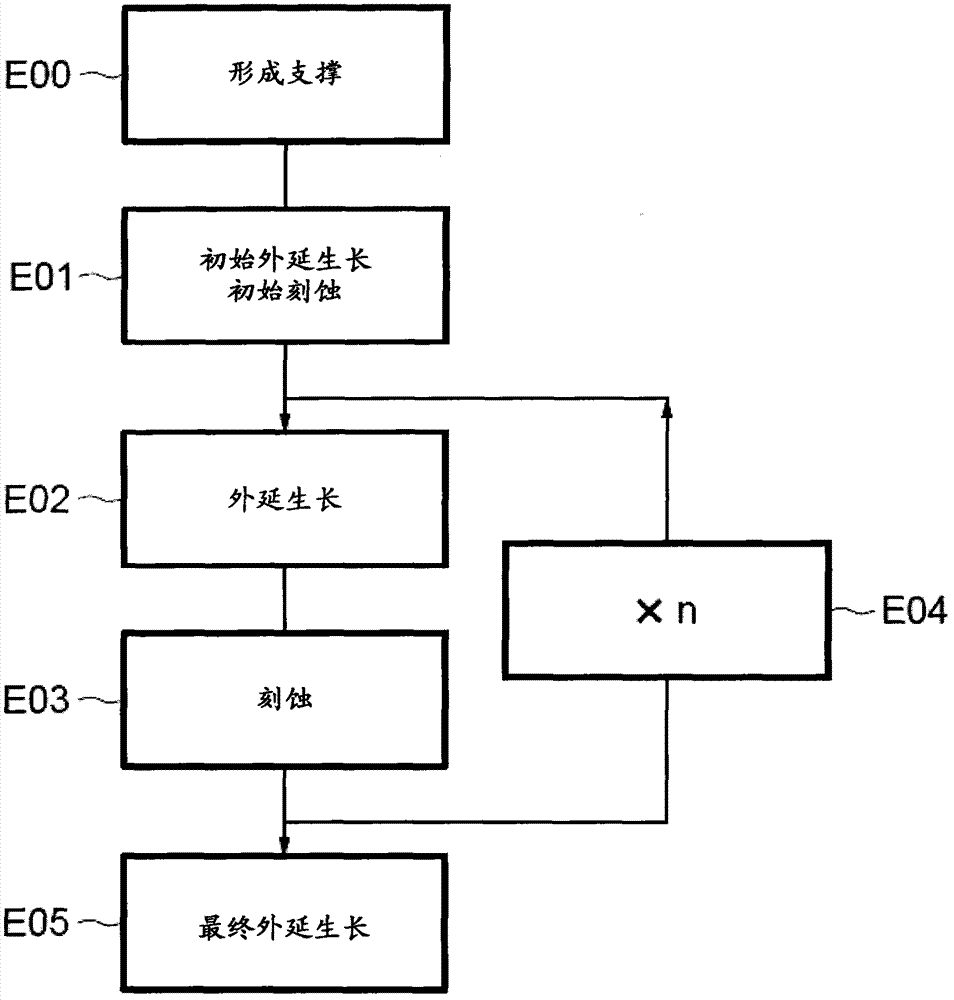

[0037] figure 1 The steps of the process according to one aspect of the present invention are schematically described.

[0038] In the first step E00, a support is formed, and it is desirable to form an epitaxial layer on the support. This step E00 may include forming a semiconductor substrate or a silicon-on-insulator (SOI) substrate, and forming at least an initial single crystal structure and an initial polycrystalline structure. The single crystal structure may be contained in a support, such as an SOI substrate. The polycrystalline structure may be an insulated gate region fabricated on the substrate or part of the initial single crystal structure.

[0039] Of course, the formation of the support may include forming other components in semiconductor materials other than silicon.

[0040] Then, step E01 of initial epitaxial growth of the initial material and initial etching is optionally performed.

[0041] Step E01 is particularly applicable to the thinnest (for example, thickn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com