Insulated gate semiconductor device

An insulated gate, semiconductor technology, used in semiconductor devices, electrical components, circuits, etc., can solve problems such as on-resistance deviation, threshold voltage deviation, forward voltage deviation, etc., to reduce characteristic deviation, reduce on-resistance, The effect of expanding the chip size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

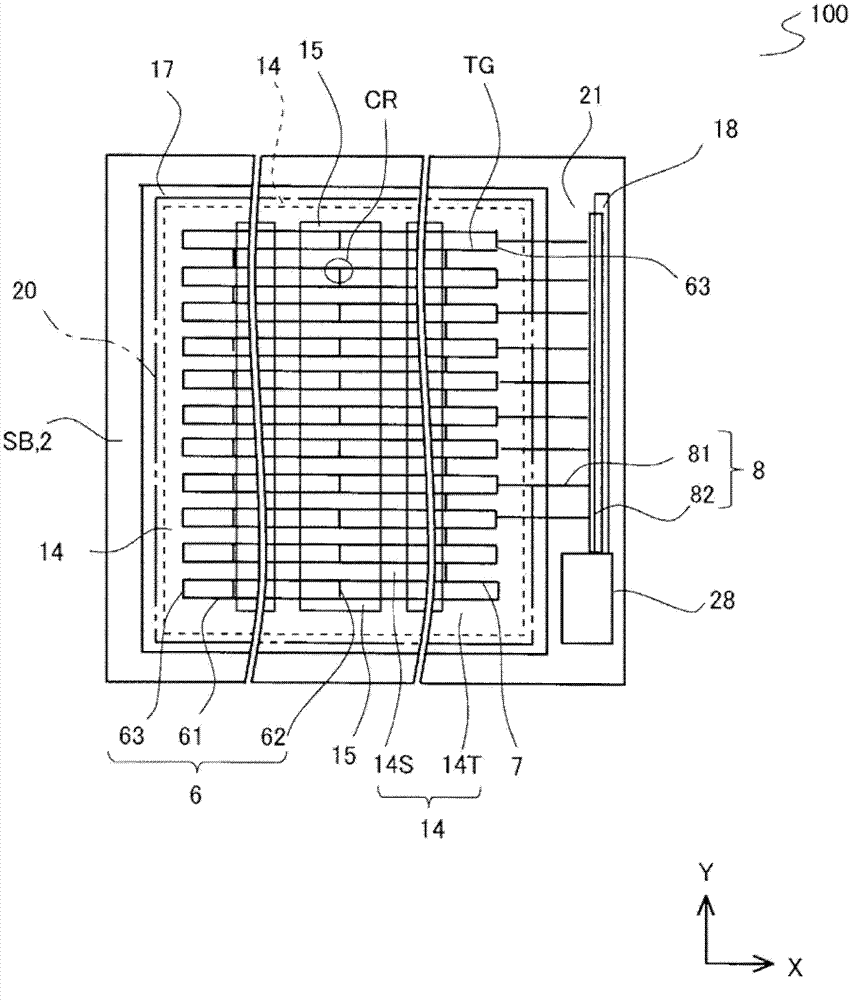

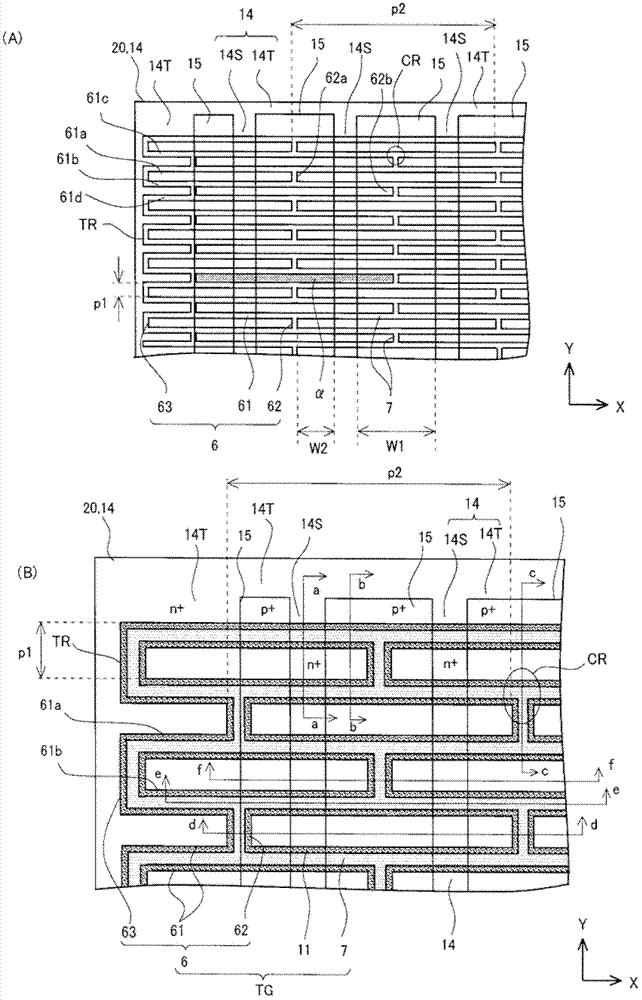

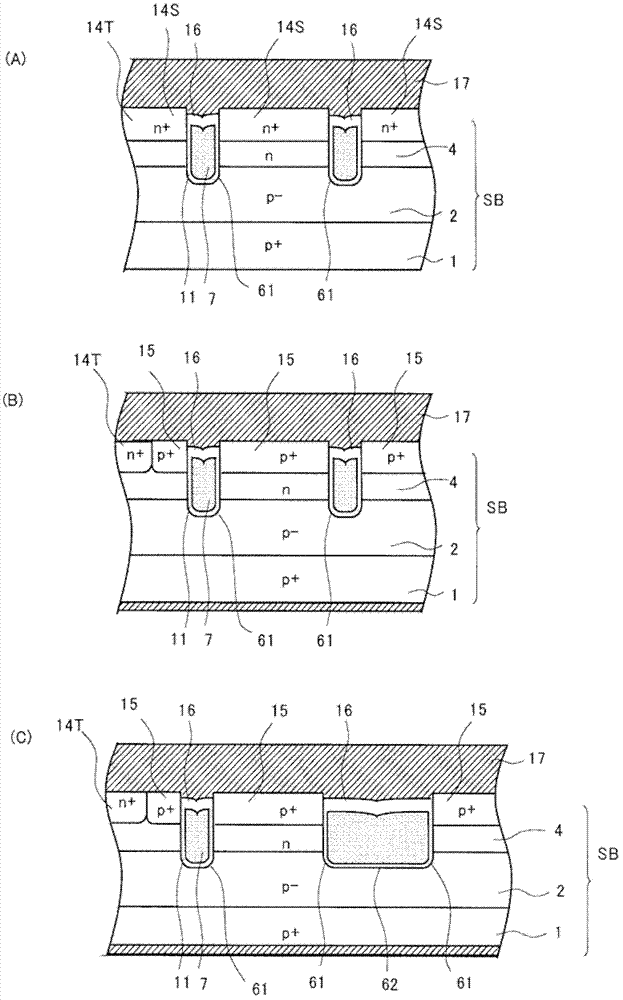

[0032] Taking the p-channel MOSFET as an example, refer to Figure 1 to Figure 4 Embodiments of the present invention will be described.

[0033] figure 1 It is a plan view of MOSFET 100 of this embodiment.

[0034] The substrate SB constituting the MOSFET 100 chip is formed by laminating a p − -type semiconductor layer 2 on a p + -type silicon semiconductor substrate (not shown). The p − -type semiconductor layer 2 is, for example, a silicon semiconductor layer formed on a p + -type silicon semiconductor substrate by, for example, epitaxial growth. The element region 20 (one-dot chain line) is provided on the surface of the p-type semiconductor layer 2 .

[0035] The element region 20 is covered with a source electrode 17 connected to a source region (not shown) of the MOSFET 100 .

[0036] The groove 6 has a first groove 61 , a second groove 62 and a third groove 63 . A plurality of first grooves 61 are provided parallel to each other in a strip shape extending along th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More