Encapsulation substrate with embedded passive components and manufacturing method thereof

A technology of passive components and packaging substrates, applied in semiconductor/solid-state device manufacturing, printed circuits assembled with electrical components, printed circuits connected with non-printed electrical components, etc., can solve problems affecting wiring, long signal transmission paths, and electrical problems. Loss and other issues, to achieve the effect of not affecting the wiring, shortening the signal transmission path, and reducing the height

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

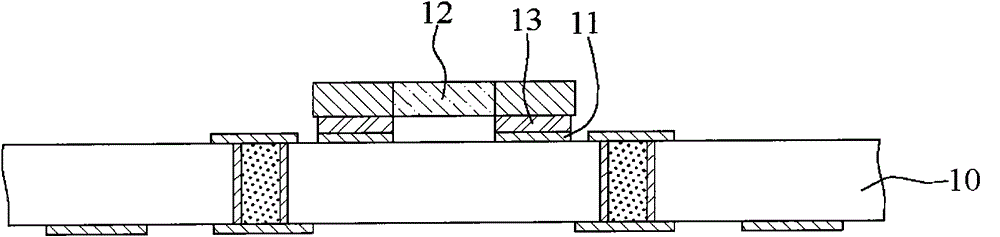

[0062] see Figure 2A to Figure 2G , is a schematic cross-sectional view of the manufacturing method of the package substrate embedded with passive components of the present invention.

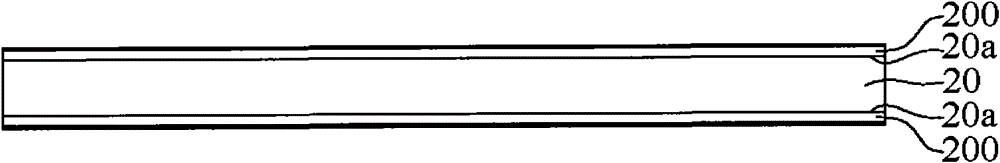

[0063] Such as Figure 2A As shown, firstly, a carrier board 20 is provided, and the two surfaces 20a of the carrier board 20 have a release film 200 and a metal layer 201 in sequence.

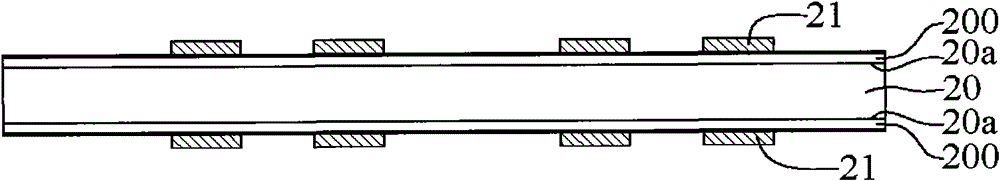

[0064] Such as Figure 2B As shown, next, a positioning pad 21 is formed on the metal layer 201 .

[0065] Such as Figure 2C As shown, the metal layer 201 on the two surfaces 20a of the carrier board 20 is covered with a first hot-melt dielectric layer 230; The pad 21 is used as a location, and then the passive component 22 is placed on the first heat-melt dielectric layer 230 . Wherein, the electrode pad 220 on the lower surface of the passive component 22 corresponds to the positioning pad 21 .

[0066] Such as Figure 2C' As shown, positioning pads 21' or 21" in different arrangements can also be fo...

no. 2 example

[0074] see Figure 3A to Figure 3G The main difference between this embodiment and the first embodiment is that the positioning pads are replaced by solder bumps, and the manufacturing steps for forming the dielectric layer unit and the second circuit layer are also different.

[0075] Such as Figure 3A As shown, provide as Figure 2A The carrier board 20 is used, and solder bumps 31 are formed on the metal layer 201 .

[0076] Such as Figure 3B As shown, provide as Figure 2C The passive component 22 , and the electrode pad 220 on the lower surface of the passive component 22 is connected to the solder bump 31 .

[0077] Such as Figure 3C As shown, a first heat-fusible dielectric layer 330 having an opening area 330a is provided on the metal layer 201 on the two surfaces 20a of the carrier board 20, so that the passive component 22 and the solder bump 31 are exposed on the metal layer 201. Opening area 330a.

[0078] Such as Figure 3D As shown, a core board 27 wit...

no. 3 example

[0084] see Figure 4A to Figure 4D The main difference between this embodiment and the first embodiment lies in the manufacturing steps of forming the first circuit layer and the build-up circuit structure.

[0085] Such as Figure 4A shown, continue Figure 2D manufacturing step, after forming the dielectric layer unit 23 by heating and pressing, the first circuit layer 44a is formed on the upper surface 23a of the dielectric layer unit 23, and the first circuit layer 44a and the upper surface of the passive component 22 There is a first conductive blind hole 440a electrically connected between the electrode pads 220; and a build-up circuit structure 45 is formed on the upper surface 23a of the dielectric layer unit 23 and the first circuit layer 44a. The build-up circuit structure 45 includes at least one dielectric layer 450 , a circuit layer 451 disposed on the dielectric layer 450 , and conductive blind vias 452 disposed in the dielectric layer 450 and electrically conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More