Testing chip and chip testing system thereof

A technology for testing chips and chips to be tested, which is applied in the direction of electronic circuit testing, etc., can solve the problems of increasing measurement cost and time-consuming measurement process, and achieve the effect of reducing mass production cost and improving measurement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

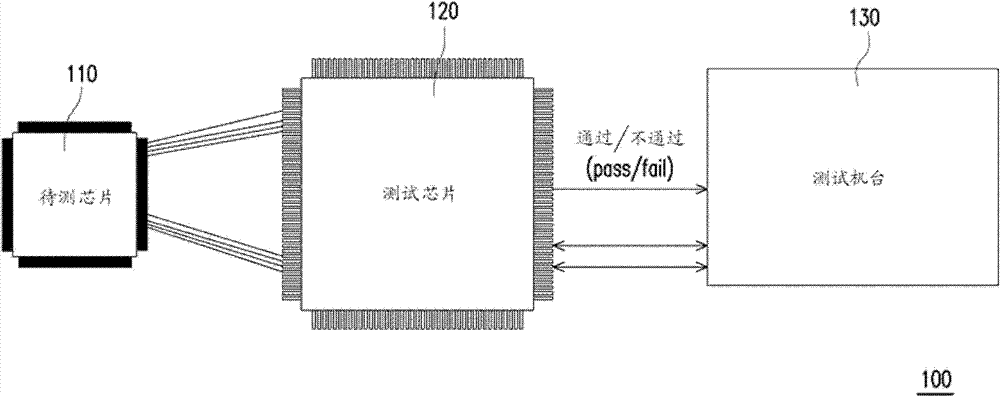

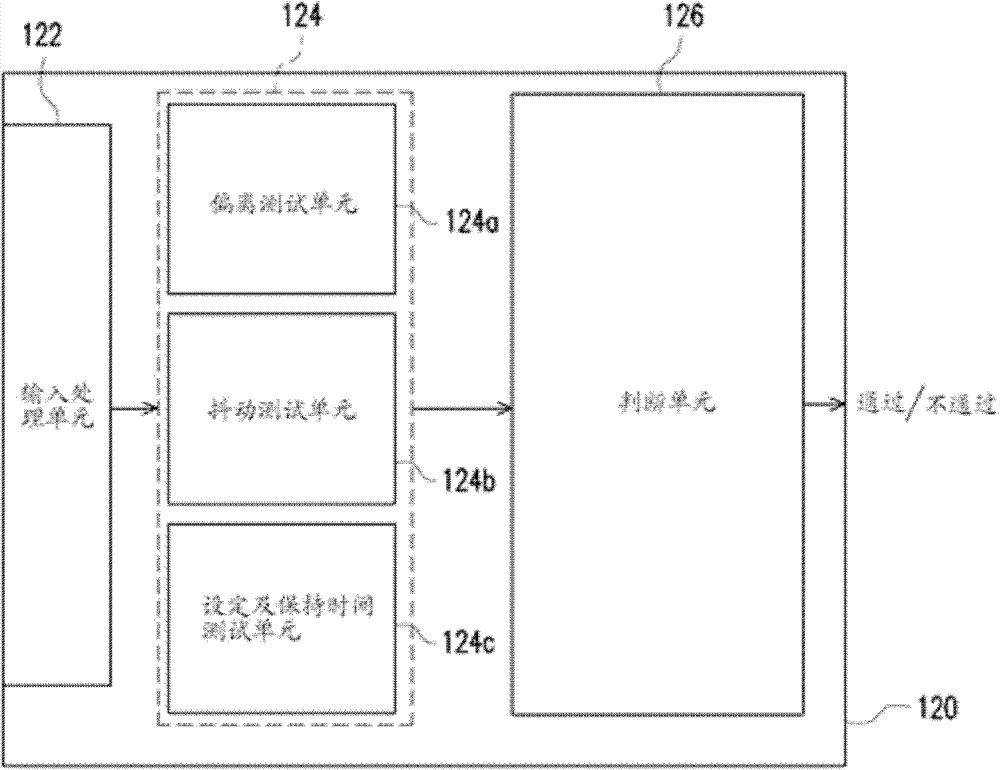

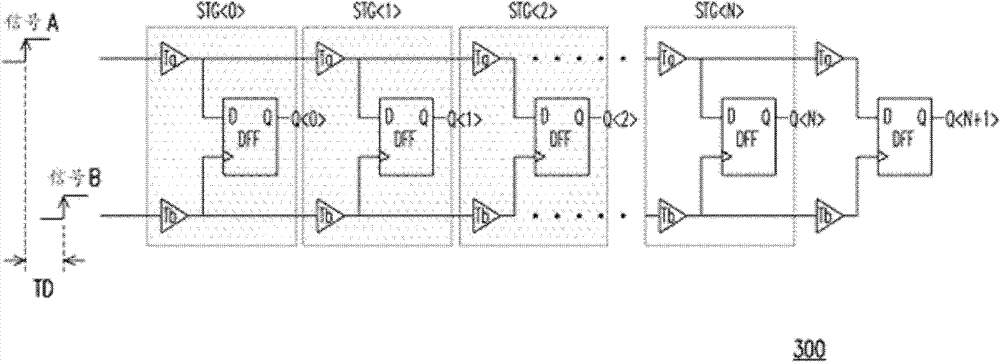

[0072] figure 1 It is a schematic diagram of the implementation of a chip testing system according to an embodiment of the present invention. Please refer to figure 1 The chip testing system 100 of this embodiment includes a chip to be tested 110, a testing chip 120, and a testing machine 130. Here, the test machine 130 utilizes test input data such as test vectors or test patterns to perform various electrical measurements on the chip 110 under test. Among them, at least for skew test, jitter test, and setup / hold time test, the chip test system 100 can use the test chip 120 to measure the chip under test 110. , In order to reduce the cost of mass production and improve the accuracy of measurement.

[0073] Therefore, in this embodiment, the testing machine 130 provides test input data to the chip under test 110 to send the signal under test to the test chip 120, and at the same time, the test machine 130 sets the test chip 120. Then, after receiving the test input data, the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com