Fast fourier transformation (FFT) parallel method based on multi-core digital signal processor (DSP) platform

A platform and multi-core technology, applied in the field of fast Fourier transform FFT processing, can solve problems such as algorithm complexity, waste of resources, and discussion of algorithm scalability solutions, and achieve the effect of improving computing efficiency and low communication distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

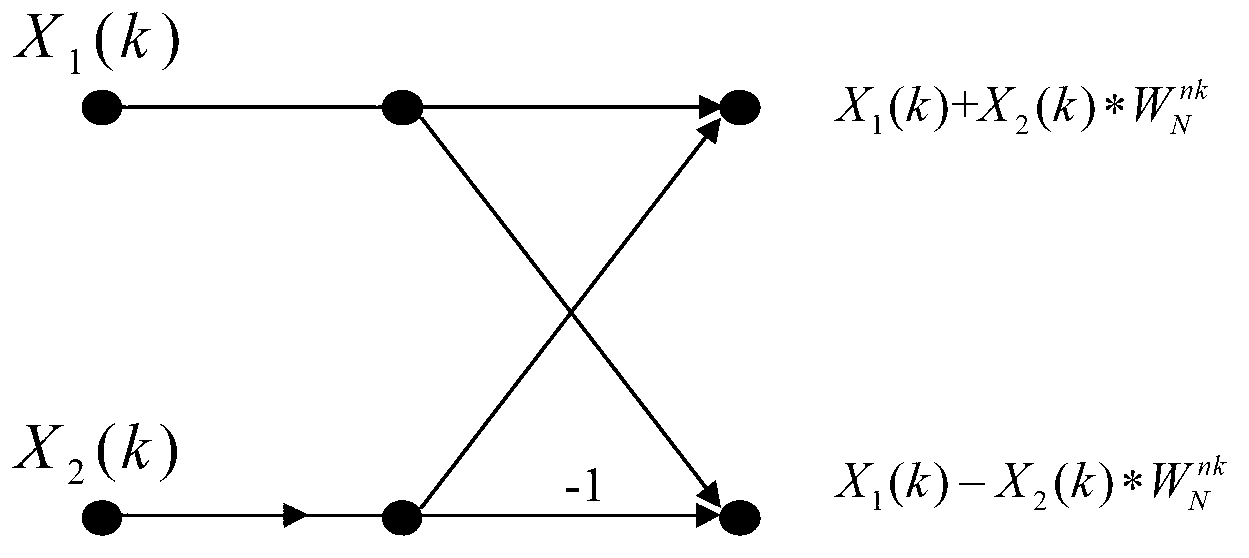

Method used

Image

Examples

Embodiment

[0064] Taking the number of processors P=4 as an example, set processor 0 as the main processor, and processors P0, P1, P2, and P3 are connected together to form a mesh network structure. The parallel FFT algorithm is implemented on the TMS320C6474EVM board, Figure 4 It is a data interaction diagram between 4 cores. SRIO (Serial Rapid I / O, fast serial input and output) interface is used for data communication between processor P0 and processor P1, between processor P2 and processor P3; between processor P0 and processor P2 1. The processor P1 and the processor P3 use an EDMA3 (Enhanced DMAversion3 Enhanced Direct Memory Access) interface for data communication.

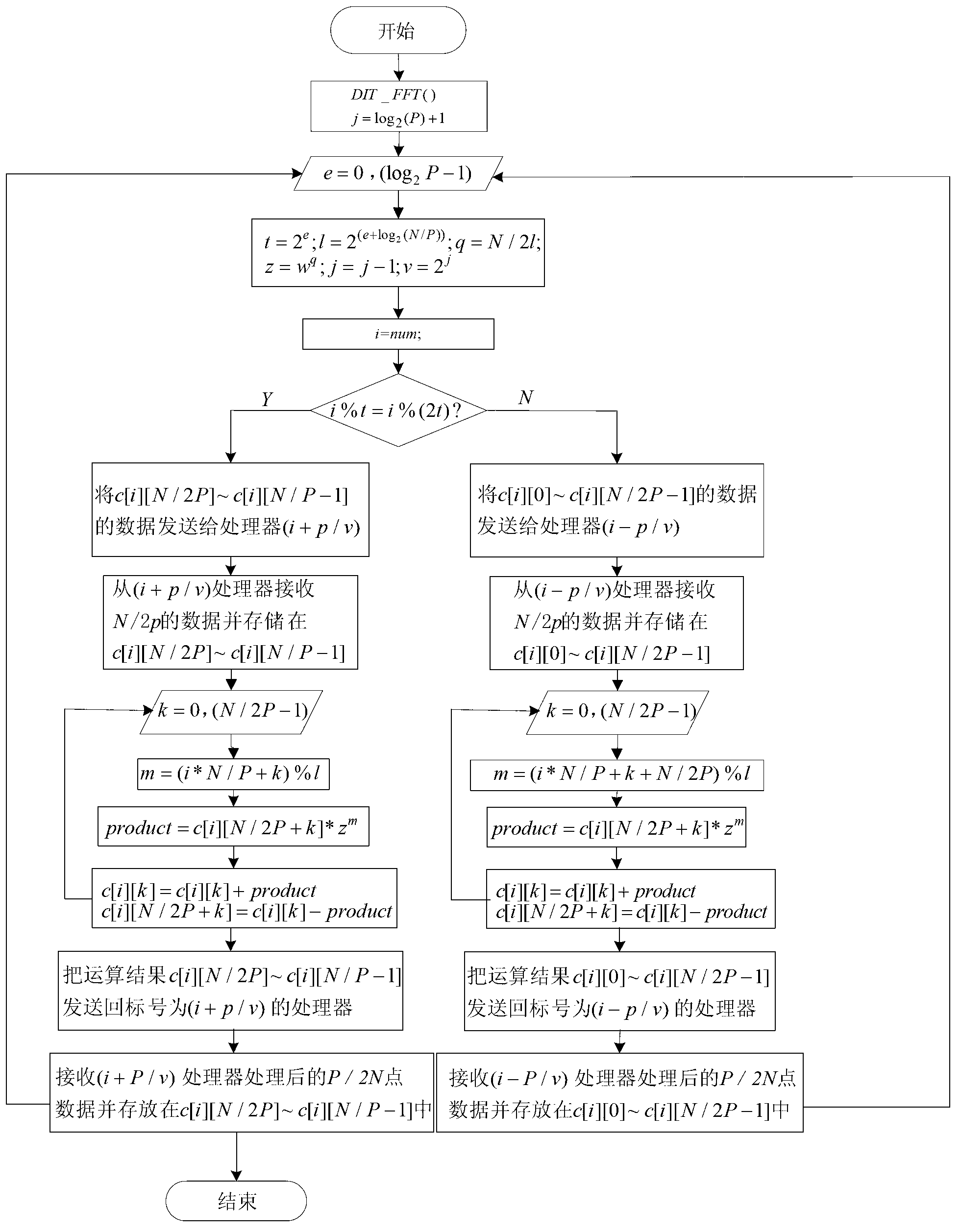

[0065] The specific implementation steps of 4 cores are as follows:

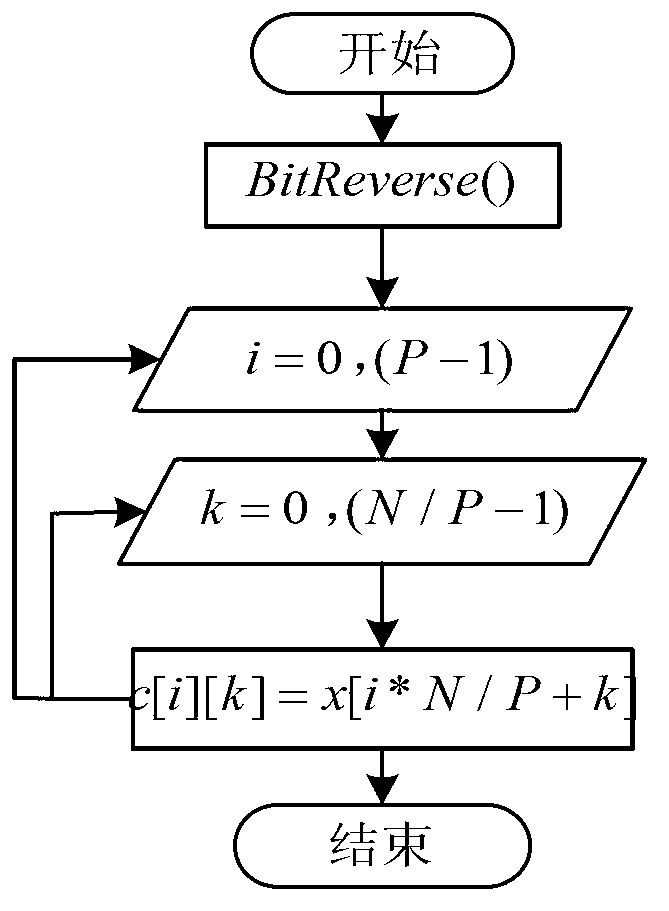

[0066] The first step: preprocessing. Processor P0 first performs bit inversion on the data, and then evenly distributes the inverted data to 4 processor units through the SRIO interface or EDMA3, and each processor unit obtains N / 4 data. See ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More