CMOS compatible MEMS microphone and method for manufacturing the same

A microphone and backplane technology, applied in the field of microphones, can solve problems such as affecting device function and manufacturing yield, and difficult to control the intrinsic stress of CMOS thin films

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example )

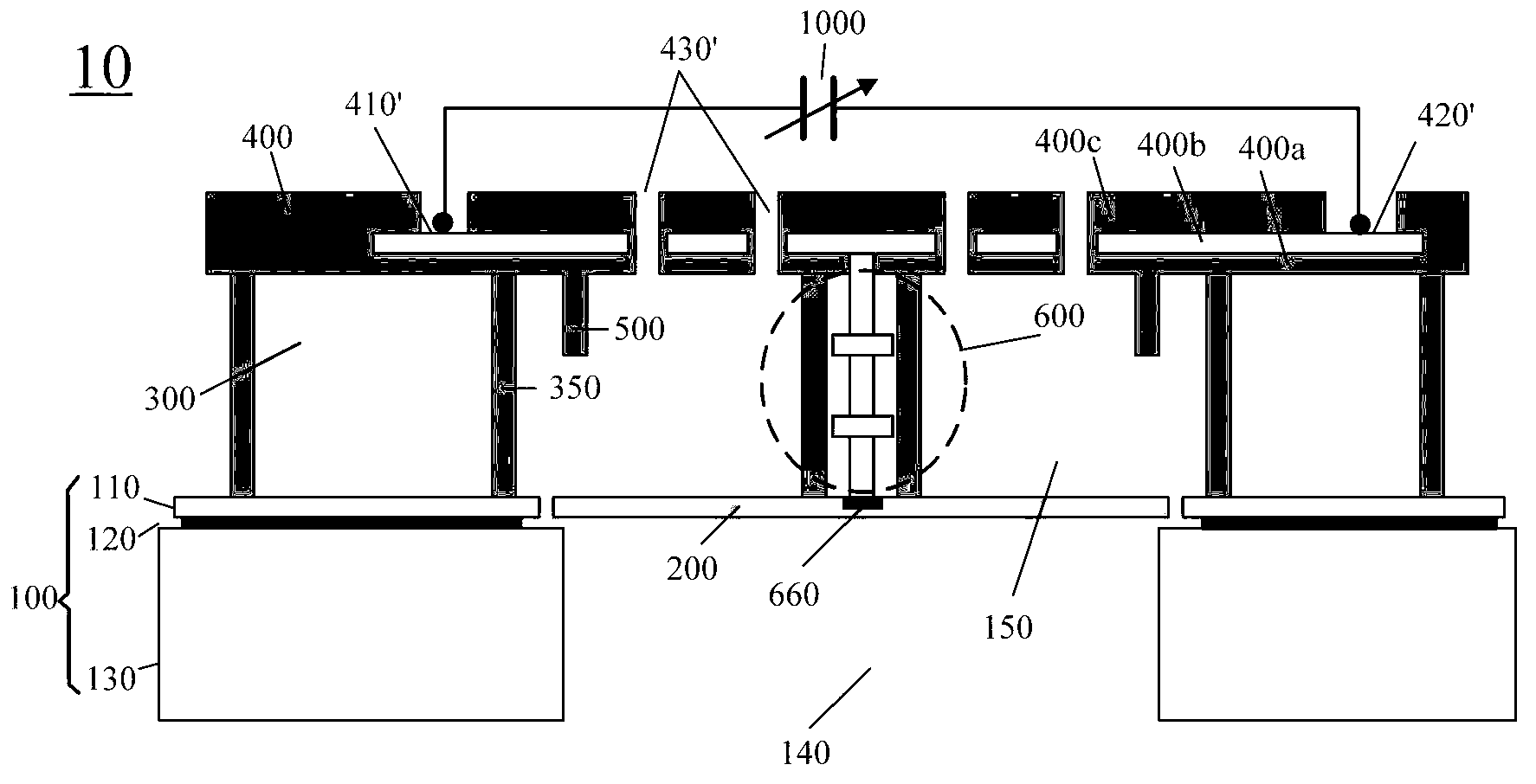

[0036] First, refer to figure 1 The specific structure of the CMOS-compatible MEMS microphone described in the first embodiment of the present invention will be described. figure 1 is a sectional view showing the structure of the CMOS-compatible MEMS microphone 10 according to the first embodiment of the present invention.

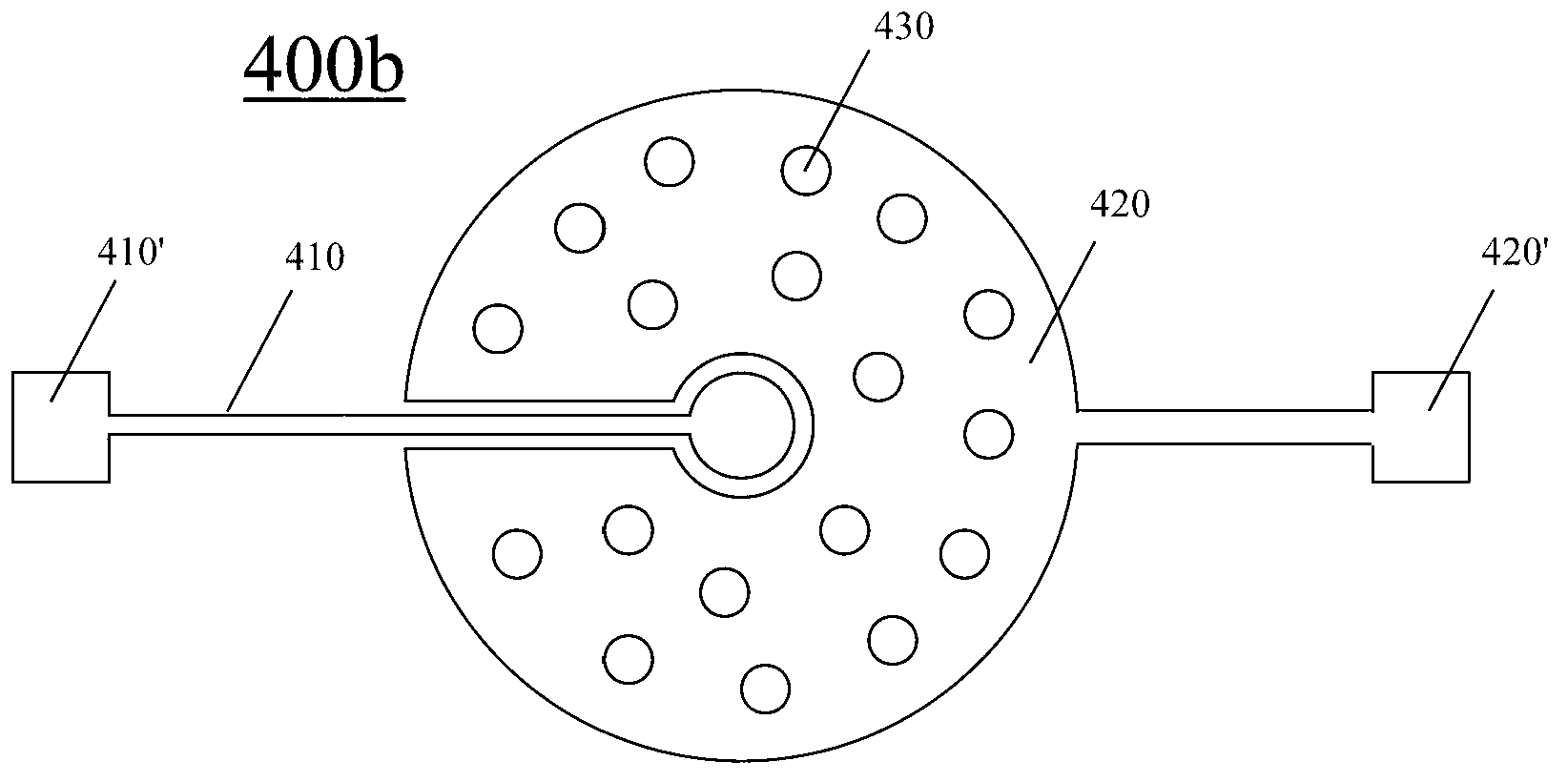

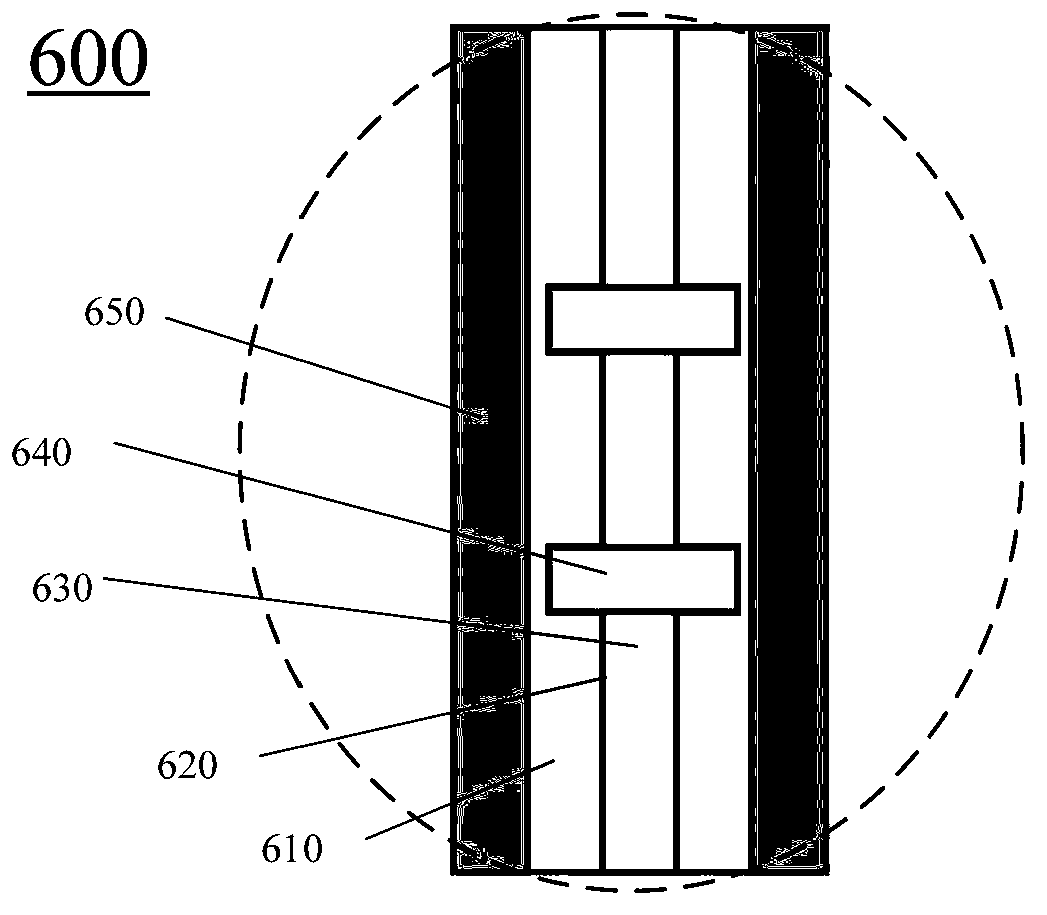

[0037] Such as figure 1 As shown, the CMOS-compatible MEMS microphone 10 includes: a silicon-on-insulator (SOI) substrate 100 , a microphone diaphragm 200 , an isolator 300 , a microphone backplate 400 , a plurality of dimples 500 and interconnection posts 600 .

[0038] The SOI substrate 100 includes a silicon device layer 110 , a buried oxide (BOX) layer 120 , and a silicon substrate 130 stacked from top to bottom in the following order. The SOI substrate 100 has openings in the silicon substrate 130 and the BOX layer 120 to expose the lower surface of the microphone diaphragm 200 , thus forming the back hole 140 .

[0039] Diaphragm 200 is formed fro...

no. 2 example )

[0059] The following will refer to Figure 5 The specific structure of the CMOS-compatible MEMS microphone described in the second embodiment of the present invention will be described. Figure 5 is a sectional view showing the structure of the CMOS-compatible MEMS microphone 10' according to the second embodiment of the present invention. Will Figure 5 and figure 1 In comparison, the difference between the second embodiment of the present invention and the first embodiment is that, in the second embodiment, the interconnection column 600' is designed to be arranged on the edge of the diaphragm 200.

[0060] Accordingly, in the second embodiment, the diaphragm 200 is not separated from the SOI substrate 100, that is, the edge portion of the diaphragm 200 is anchored. Therefore, preferably, the intrinsic stress of the prepared silicon device layer 110 of the SOI substrate 100 is small, so that the performance of the diaphragm 200 is less affected.

[0061] In addition, in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com