Field programmable gate array-based (FPGA-based) realization method for converting liquid crystal display (LCD) signal to video graphics array (VGA) signal

A signal and reset signal technology, applied in cathode ray tube indicators, static indicators, instruments, etc., can solve the problem of encryption cost and encryption level compromise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

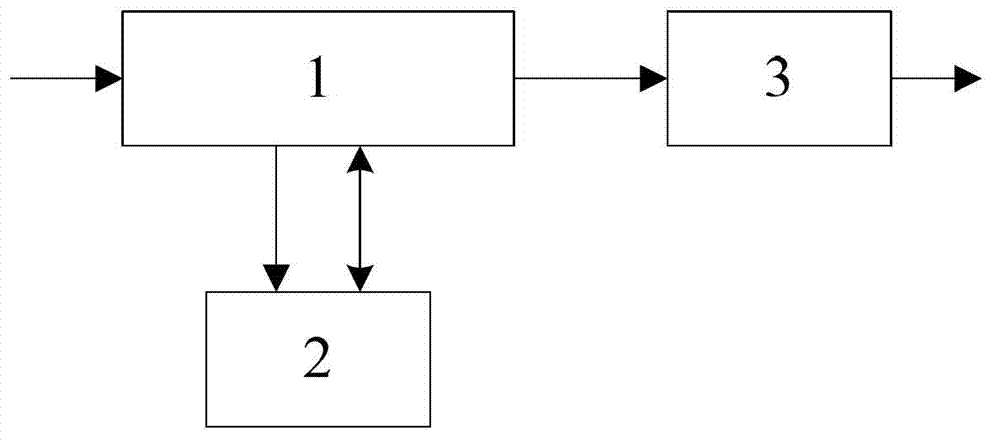

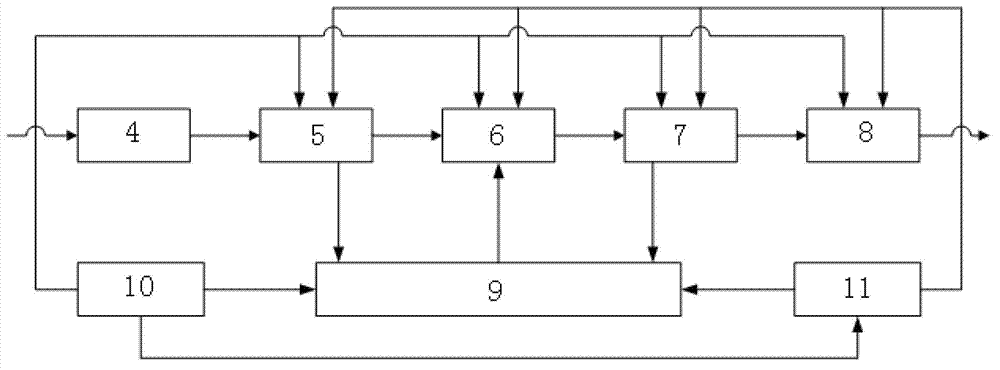

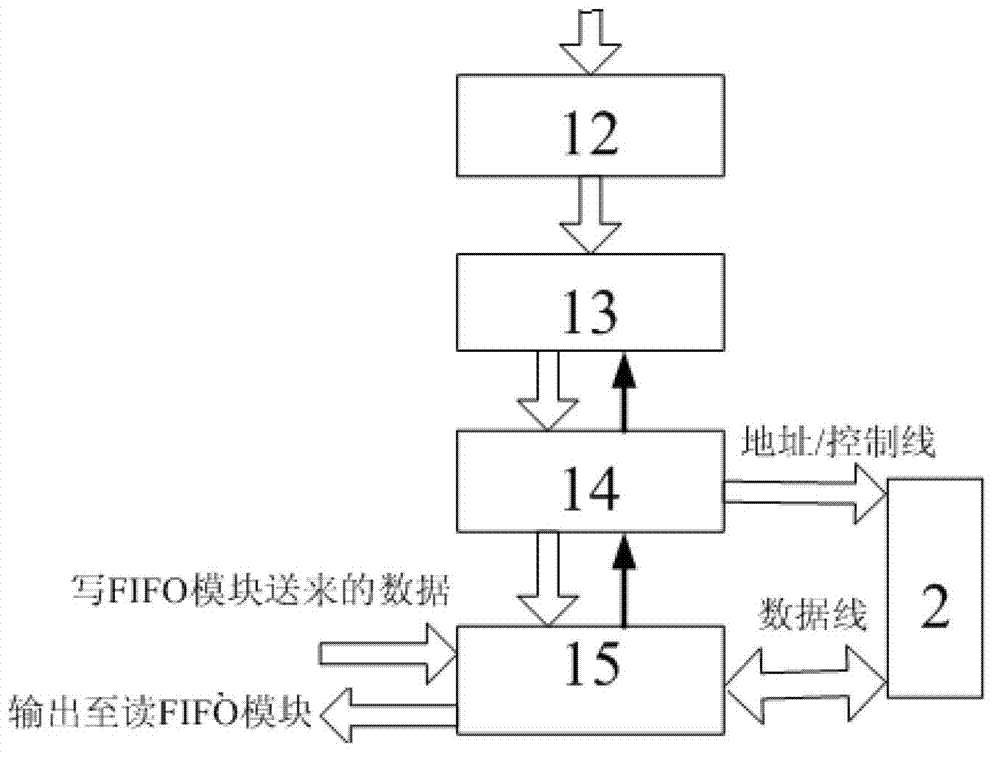

[0043] Examples of the invention figure 1 -5, an embedded system based on FPGA-based LCD signal to VGA signal is mainly constructed by FPGA module, SDRAM module and exclusion network module, which is characterized in that the FPGA module includes clock management module, reset module, LCD signal receiving Module, write FIFO module, SDRAM controller module, read FIFO module, FIFO controller module and VGA display module, LCD signal receiving module and write FIFO module are connected, write FIFO module and SDRAM controller module are connected, SDRAM controller module Connected to read FIFO module and SDRAM module respectively, FIFO controller module is connected to write FIFO module and read FIFO module respectively, read FIFO module is connected to VGA display module, clock management module is connected to reset module, write FIFO module, SDRAM respectively The controller module, read FIFO module, FIFO controller module, VGA display module and SDRAM module are connected, and ...

Embodiment 2

[0048] A method of using the above system to realize FPGA-based embedded LCD signal conversion to VGA signal. The input terminal of the FPGA module receives the LCD signal from the embedded system, including LCD field synchronization signal, LCD clock signal, LCD data valid signal and 24-bit LCD data signal, where the LCD field synchronization signal represents the end of the previous frame of image and the start of a new frame of image. The signal meets the LCD display timing; timing parameters (clock frequency, vertical blanking front shoulder, vertical blanking back shoulder, line The blanking front shoulder, line blanking back shoulder, etc.) have been defined in the embedded system kernel as a 1024x76820Hz signal. Since the received LCD signal resolution is 1024x768, the width is 24 bits, that is, a valid LCD signal has 768 lines, each line has 1024 pixels, a total of 1024x768 pixels. The FPGA module uses the LCD clock signal as the acquisition clock to collect 24-bit LCD d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More