Method and system for scheduling delay slot in very-long instruction word structure

A technology of super-long instruction word and scheduling method, applied in the direction of concurrent instruction execution, machine execution device, etc., can solve the problems of affecting the compilation speed of the compiler, affecting the actual efficiency of the program, and high cost, and achieve the effect of high execution efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The technical solutions of the present application will be described in further detail below with reference to the drawings and embodiments.

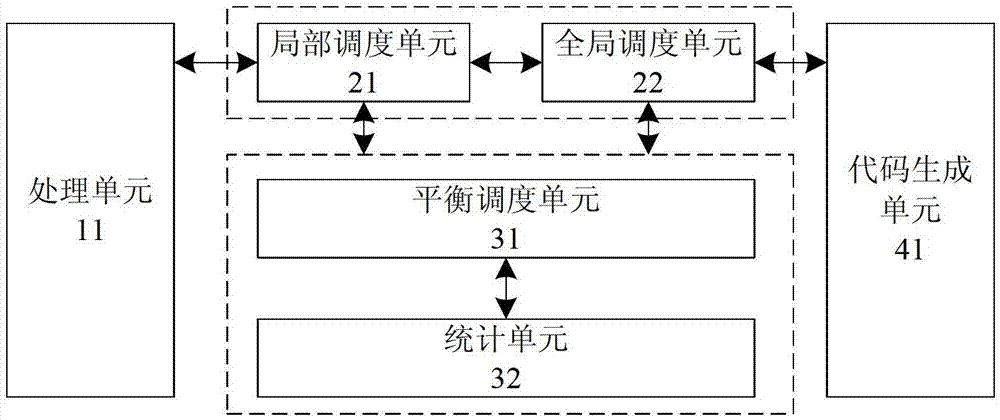

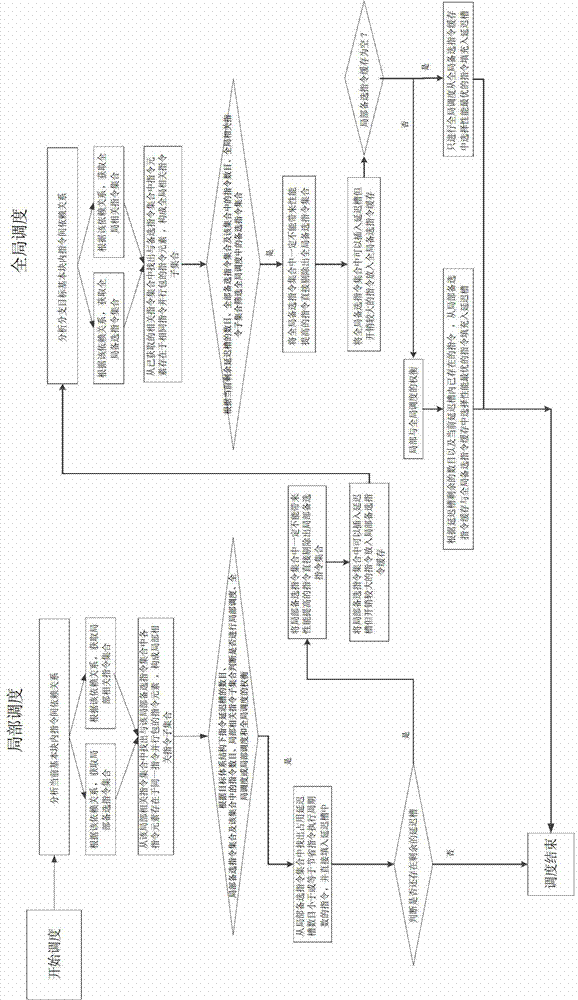

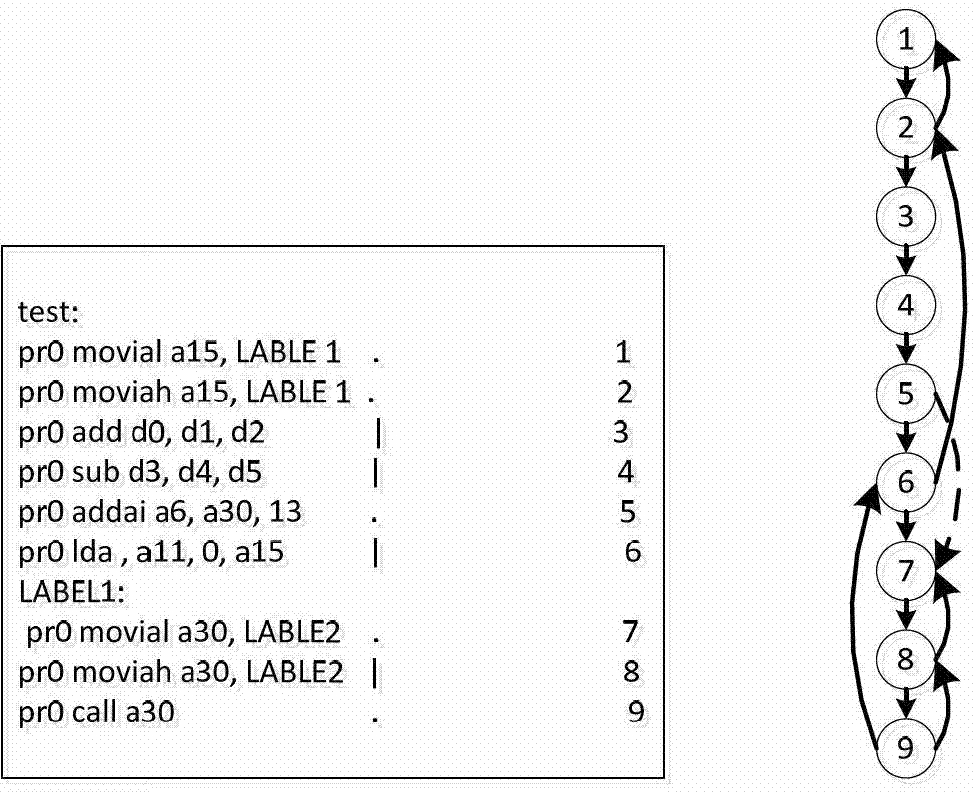

[0021] The embodiment of the present invention proposes a delay slot scheduling method under the VLIW structure, which is used to complete the instruction filling work of the delay slot from the assembly level. This method combines the local scheduling strategy and the global scheduling strategy in the proposed delay slot scheduling algorithm, and according to the requirements of the VLIW structure for instruction parallelism, a balanced scheduling strategy is designed to achieve a trade-off between instruction delay slot scheduling and program parallelism. A trade-off between local and global scheduling to achieve the highest possible instruction pipeline performance.

[0022] Combine below figure 1 and figure 2 The delay slot scheduling method and system thereof under the VLIW structure of the embodiment of the present inven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More