A synchrophasor calculation method based on fpga hardware dft recursion

A technology of synchrophasors and calculation methods, which is applied in computing, special data processing applications, instruments, etc., and can solve problems such as high CPU load, inability to send synchrophasor data packets evenly, and large errors in calculation results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

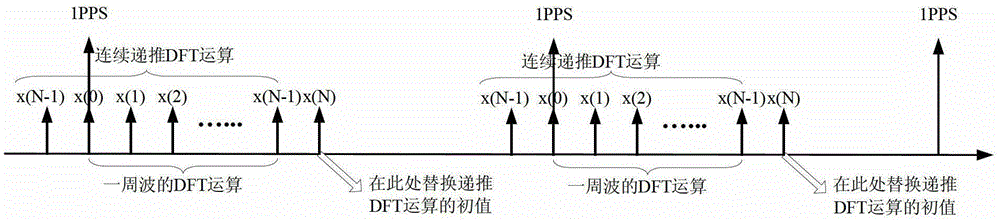

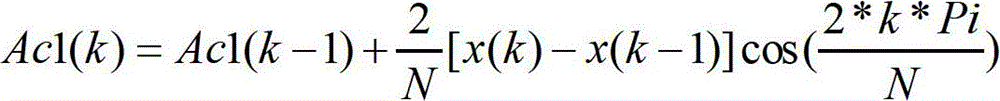

[0066] In order to make the technical means realized by the present invention, creative features, goals and effects reach a clear understanding, the following in conjunction with the appended figure 1 And attached figure 2 , to further illustrate the present invention.

[0067] see figure 1 and figure 2 , a kind of synchrophasor calculation method based on FPGA hardware DFT recursion of the present invention is characterized in that the method comprises the following steps:

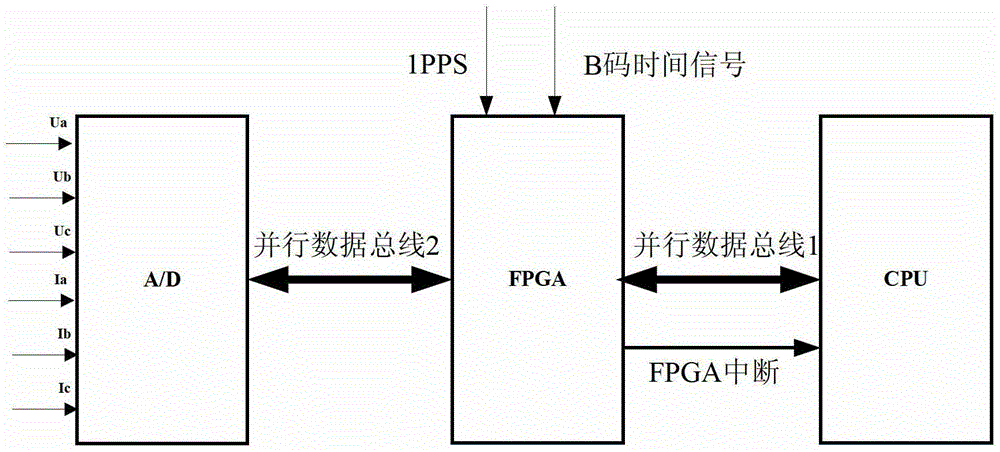

[0068] (1) FPGA and CPU are connected by 32-bit or 64-bit parallel bus 1 in hardware, FPGA has an interrupt signal connected to the external interrupt pin of CPU, FPGA is connected to 1PPS signal of standard clock and B code time signal, FPGA passes Parallel bus 2 controls the AD chip;

[0069] (2) Define the sampling configuration register (CONFIG_REG), sampling buffer register (DATA_REG), DFT coefficient original register (DFT_COEF), and DFT result buffer register (DFT_REG) on the FPGA side;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com