Pixel driving circuit and driving method thereof

A pixel driving circuit and driving method technology, applied in static indicators, instruments, etc., can solve problems such as inability to accurately eliminate display unevenness, improve the ability to suppress uneven voltage distribution, reduce data voltage, and improve aperture rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

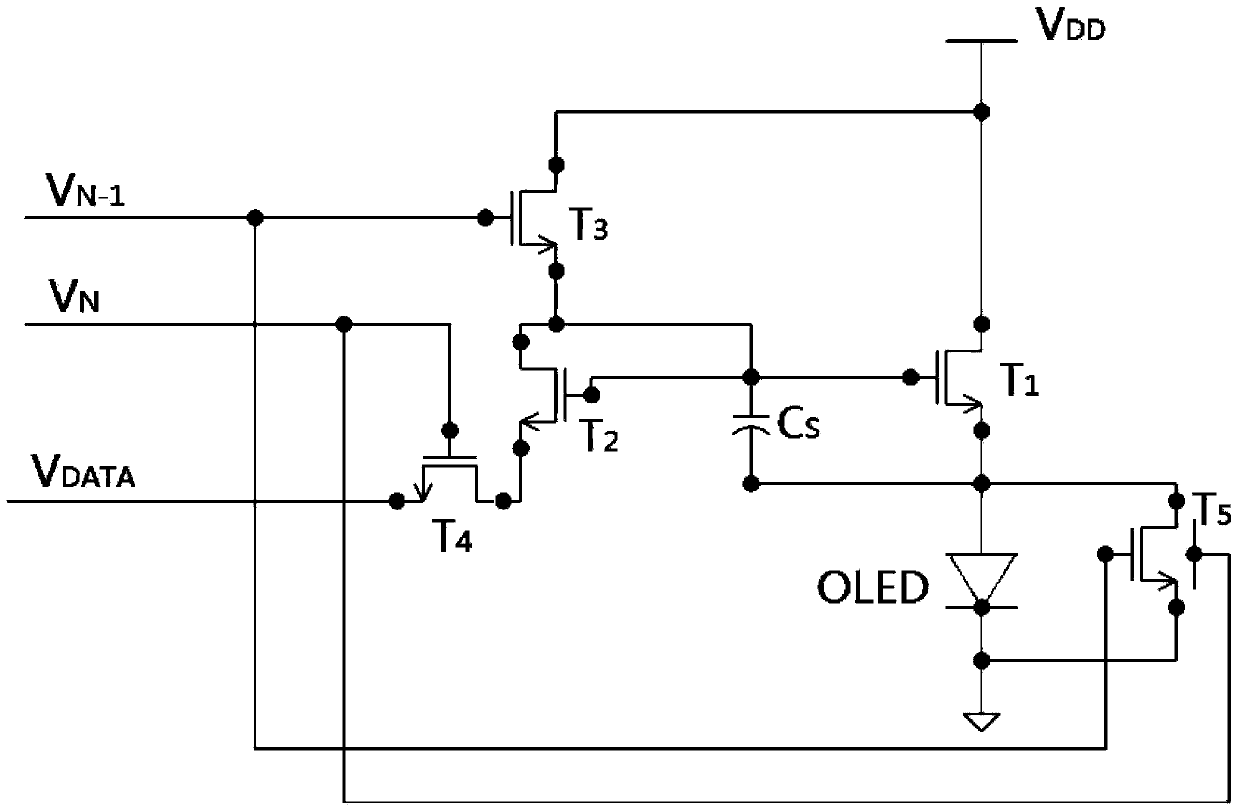

[0037] The pixel driving circuit of the present invention includes: a first transistor T1 to a fourth transistor T4, a storage capacitor C S , organic light-emitting diode OLED, bypass circuit, data line, N-1th scanning line V N-1 and the Nth scan line V N ;in,

[0038] The drain of the first transistor T1 is connected to the power supply voltage, and the gate is connected to the storage capacitor C S The first end of the source is connected to the storage capacitor C S The second terminal of the OLED and the anode of the OLED;

[0039] The drain and gate of the second transistor T2 are connected to the storage capacitor C S The first end of the first terminal, the source of the third transistor T3 and the gate of the first transistor T1, the source is connected to the drain of the fourth transistor T4;

[0040] The gate of the third transistor T3 is connected to the N-1th scanning line, the drain is connected to the power supply voltage, and the source is connected to th...

Embodiment 2

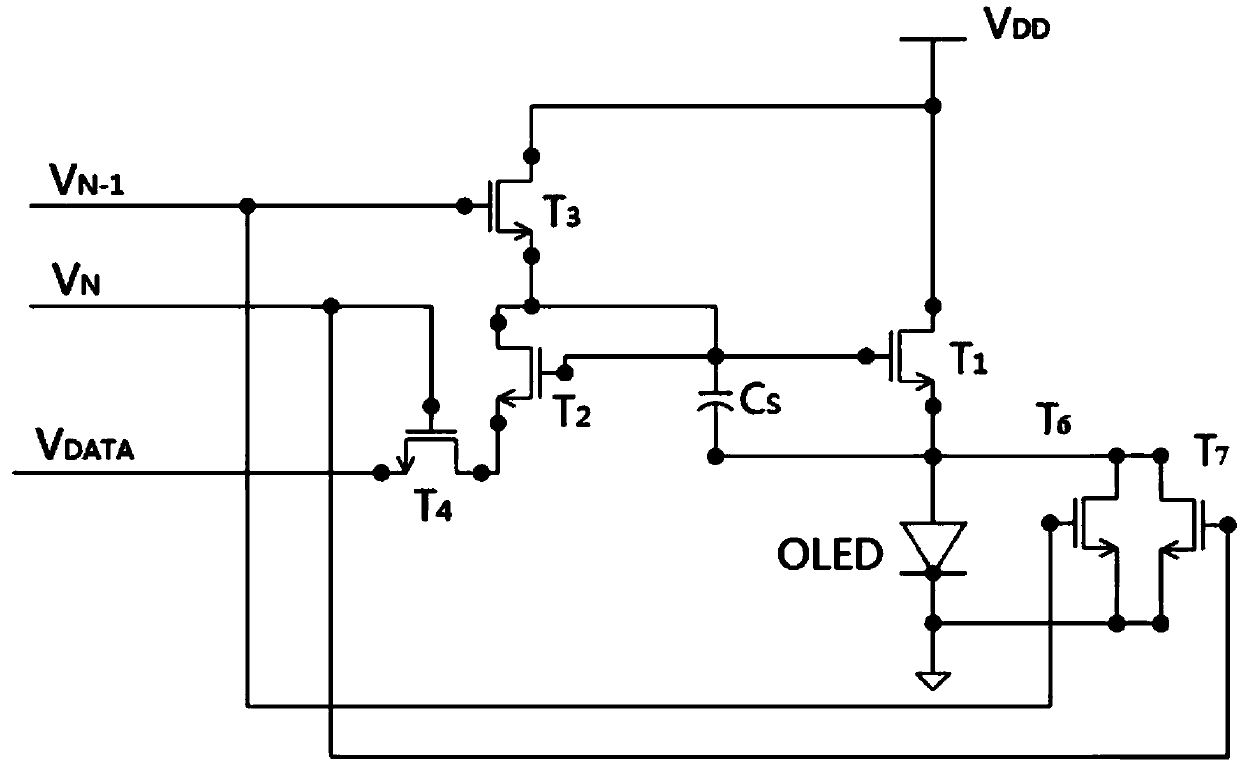

[0055] In this embodiment, the bypass circuit is the sixth transistor and the seventh transistor T6 and T7 connected in parallel with the OLED, the drains of T6 and T7 are respectively connected to the anode of the OLED, the sources of T6 and T7 are grounded, and the gate of T6 Pole connected to the N-1th scan line V N-1 , the gate of T7 is connected to the Nth scan line V N , other circuit connections are the same as those in Embodiment 1, such as figure 2 shown.

[0056] The driving scheme of the above-mentioned pixel driving circuit includes the following steps:

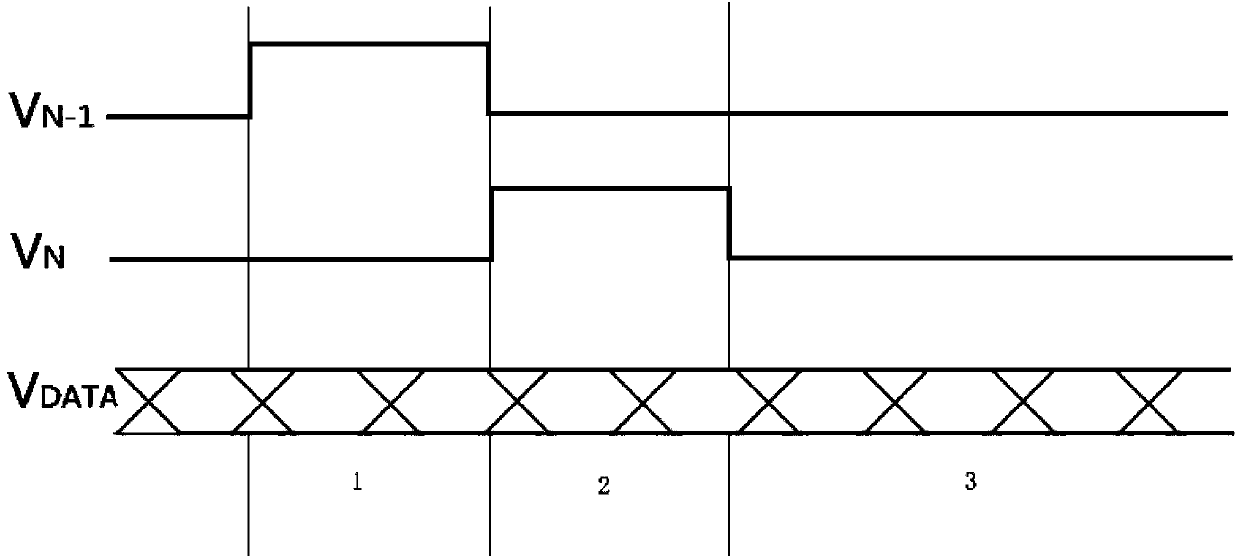

[0057] 1) Preset stage: N-1th scan line V N-1 is high and the Nth scan line V N is low level, at this stage, the second transistor T2, the third transistor T3 and the sixth and seventh transistors T6 and T7 are turned on, and the power supply voltage V DD on the storage capacitor C S precharged to supply voltage V DD ;

[0058] 2) Adjustment stage: N-1th scan line V N-1 is low and the Nth scan line V N ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More