48*30 bit multiplier based on Booth algorithm

A multiplier and algorithm technology, which is applied in the field of multiplier pipeline design, can solve the problems of high cost and multiple hardware, and achieve the effects of saving cost, reducing hardware resource consumption, and shortening the clock cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The specific embodiment of the present invention is described in detail below in conjunction with accompanying drawing:

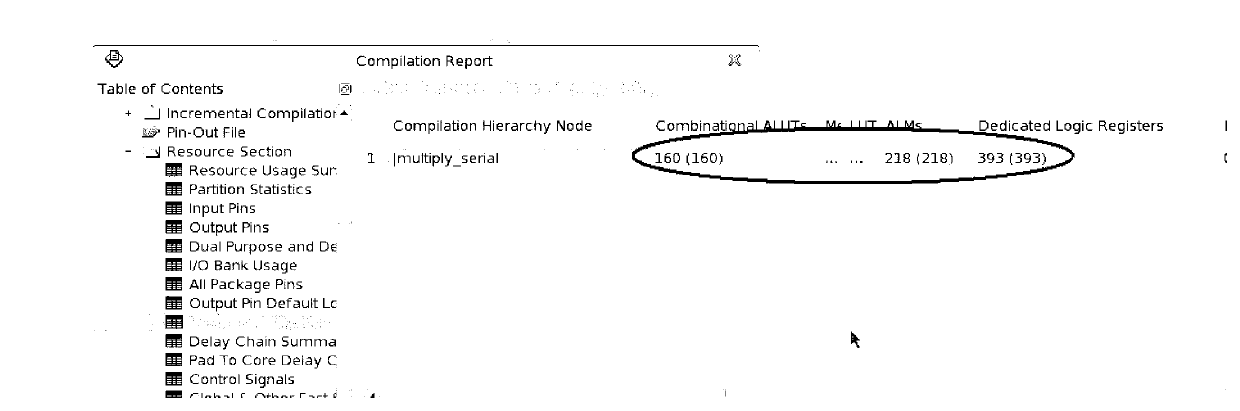

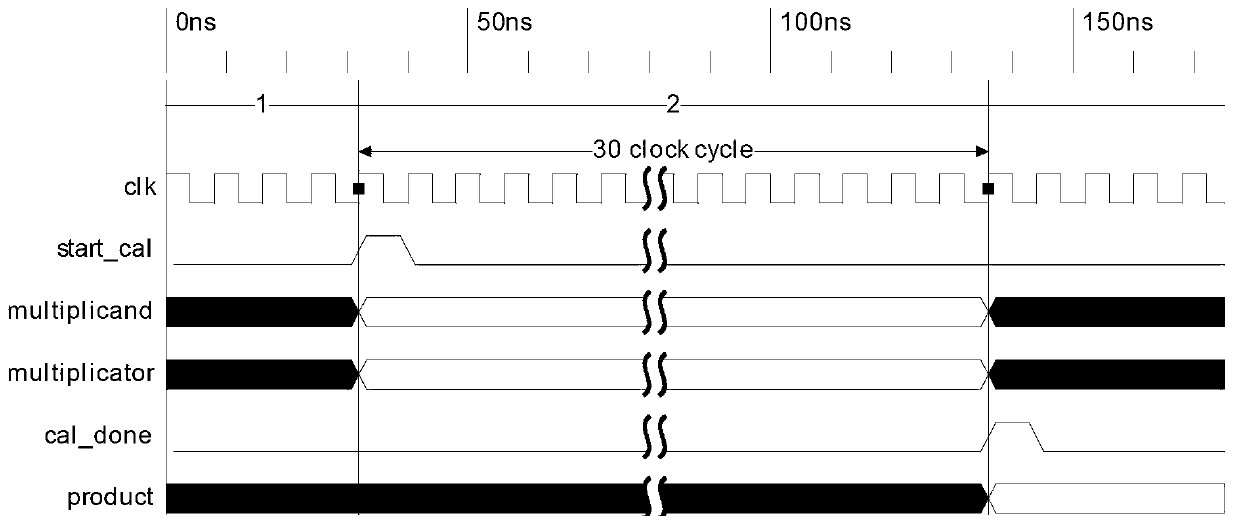

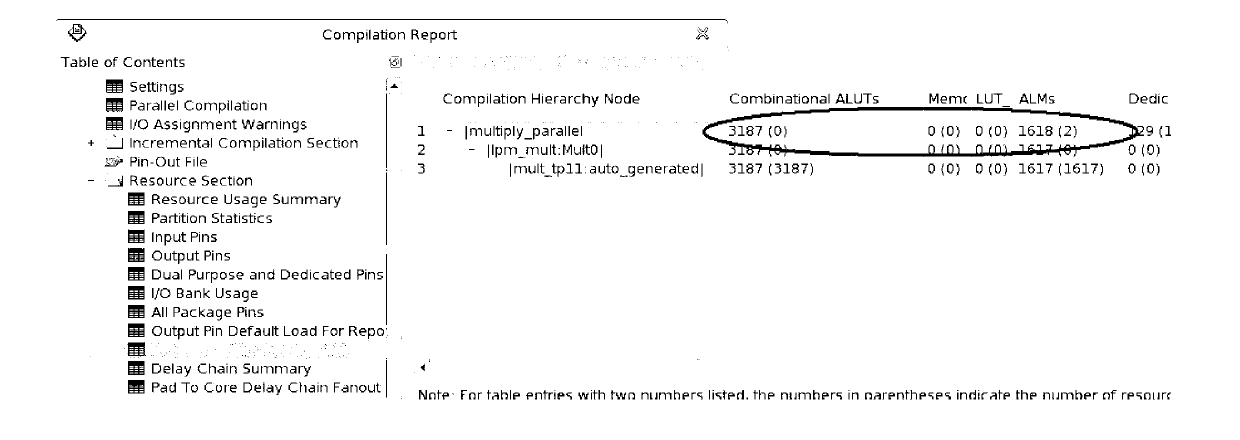

[0022] The main design idea of the 48x30-bit multiplier based on the Booth algorithm in this embodiment is to use the Radix-4Booth algorithm to generate partial products and perform pipeline addition operations on the partial products. The generation of partial products is only determined by the multiplier. According to the Booth algorithm, any Reasonably select the number of partial product generating circuits to improve the performance of the multiplier, at the cost of adding more partial product generating circuits and adder circuits.

[0023] refer to Figure 5 As shown, the 48x30-bit multiplier based on the Booth algorithm in this embodiment includes a Bit shift control module, a partial product generator, a pipeline accumulation controller and a partial product pipeline accumulator. in:

[0024] The bit shift control module is used to recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More