VLSI system structure of bit plane encoder

An encoder and bit plane technology, applied in image coding, instruments, television, etc., to reduce access and reduce clock cycles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0039] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

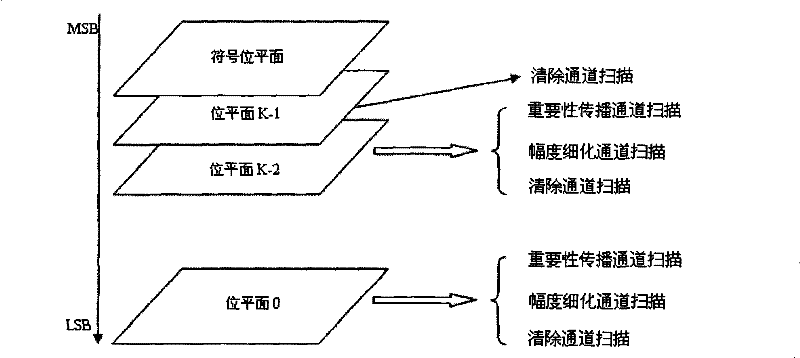

[0040] combine first figure 1 The algorithm of this embodiment is briefly described. The idea of bit-plane coding is to encode the most important information first, that is, to encode the amplitude information with a larger weight first, so that with the subsequent code stream organization, the final code stream can obtain the characteristics of progressive transmission. After wavelet transformation and quantization, the slice component matrix becomes a subband matrix of integer coefficients. Each subband is divided into rectangular code blocks of the same size (except for the code blocks on the border). Each code block can be decomposed into bit planes, that is, bit layers one by one. The encoding is encoded plane by plane from the most significant bit-plane to the lowest bit-plane of the code block. The bit-plane encoder performs an independent ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More