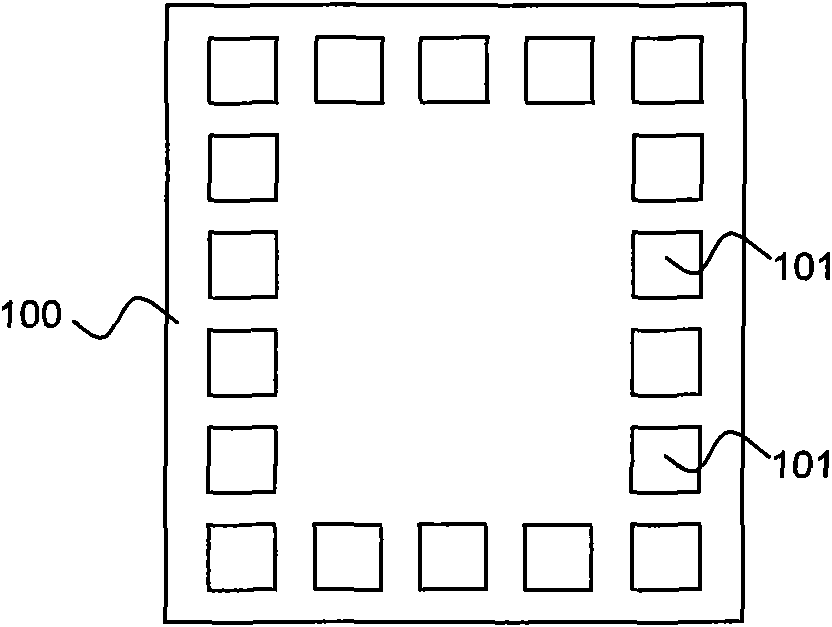

Wafer-level package structure and production method thereof

A technology of wafer-level packaging and packaging structure, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc., and can solve problems such as sealing protection and unresolved chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

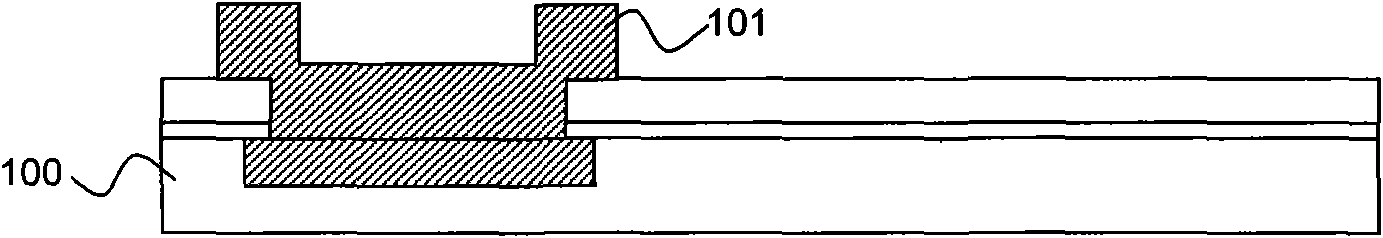

[0048] due to Figure 2J-2M In the shown manufacturing process, the substrate 200A included in the wafer 200 is cut into substrate units 200'A included in the chip 200', so for Figure 2MIn terms of the wafer-level packaging structure 200″A shown, in the silicon substrate unit 200′A included in the chip 200′, the metal material 208′ filled in the through hole 208 contacting the first type of arrangement pad 204a The first type of arrangement pad 204a in contact with the through hole 208 is electrically connected to the bottom electrode metal layer 209'. In an optional embodiment, the chip 200' is a MOSFET of vertical structure, that is, Its main current flows from the top of the device to the bottom, or vice versa. The drain region of the chip 200' is usually formed on the side near the bottom surface of the chip 200' in the substrate unit 200'A, in order to strengthen the contact between the bottom electrode metal layer 209' and the chip. 200' Ohmic contact of the drain regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More