Method making back of wafer flat

A planarization method and technology on the back, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of difficult control, particle pollution, scratches, etc., and achieve the effect of easy control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The principles and features of the present invention will be described below with reference to the accompanying drawings. The examples cited are only used to explain the present invention, and are not used to limit the scope of the present invention.

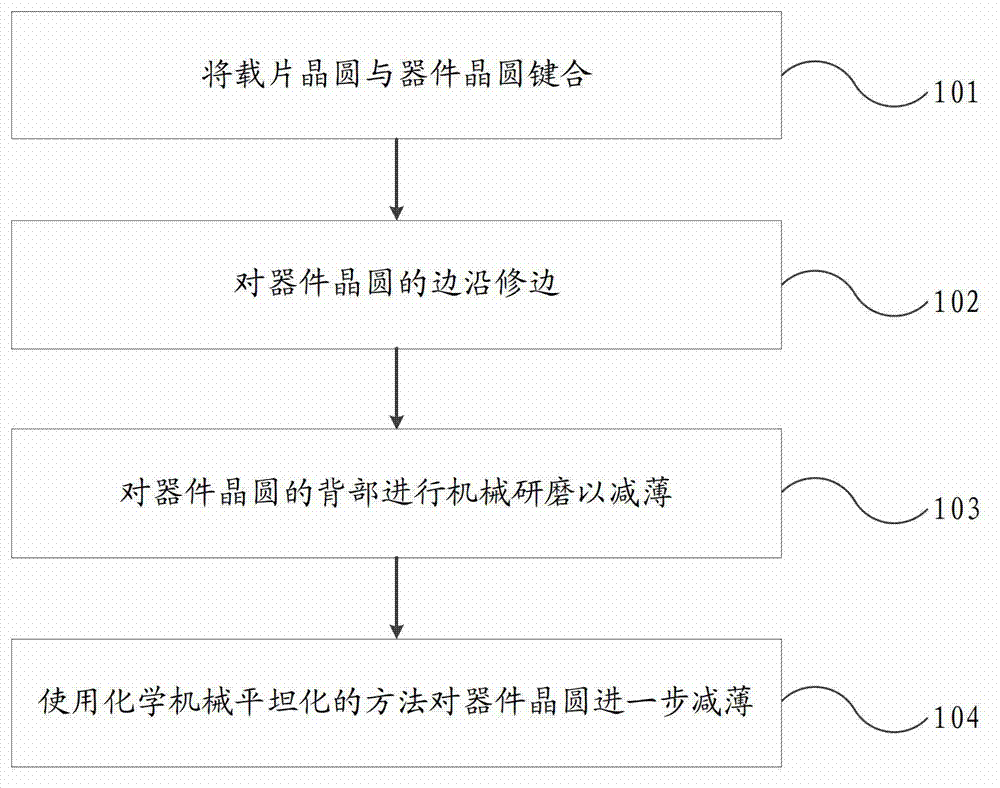

[0023] Such as figure 1 As shown, a method for flattening the back of a wafer includes the following steps:

[0024] Step 101: bonding the carrier wafer 1 and the device wafer 2 through a bonding oxide, such as silicon dioxide;

[0025] Step 102: Trimming the device wafer 2 to make the edges of the device wafer 2 smooth;

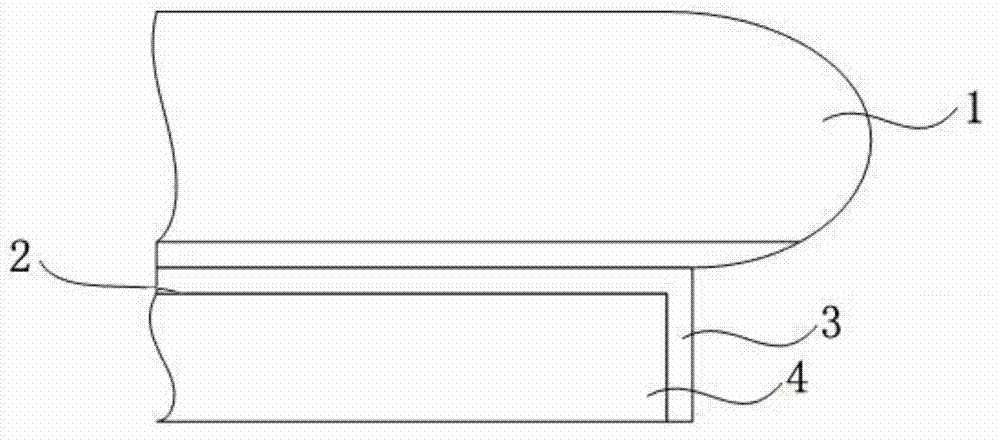

[0026] Step 103: Perform mechanical grinding on the back of the device wafer 2, which is the side opposite to the side bonded to the device wafer 2, and grind the device wafer 2 to the device wafer 2 The thickness is 25um~50um, the structure diagram of the finished product after grinding is as follows figure 2 Shown

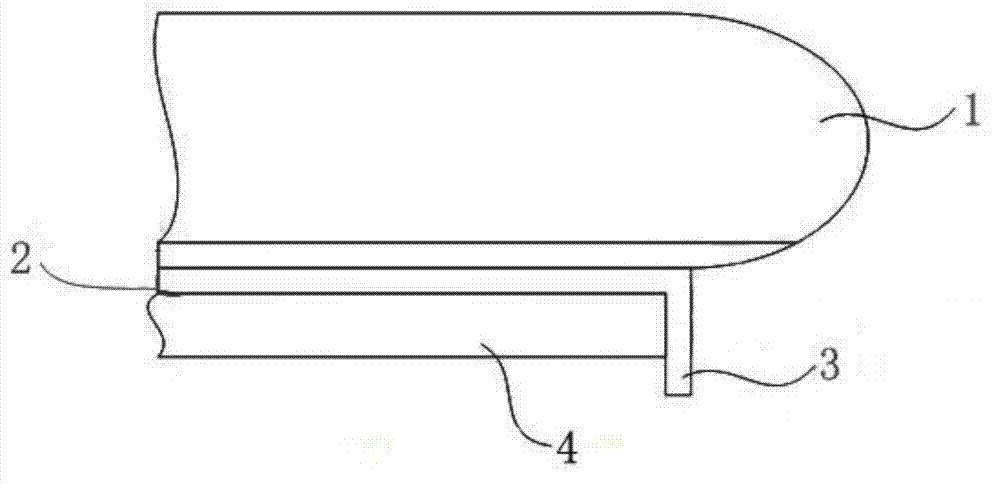

[0027] Step 104: Process the back of the device wafer 2 by a chemical-mechanical planarization...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More