Bit-plane coding hardware structure and method in compliance with ccsds standard

A bit-plane coding and standard technology, applied in the field of communications, can solve the problems of allocating hardware resources, high hardware resource overhead, low coding efficiency, etc., and achieve the effect of overcoming high computational complexity, low hardware resource overhead, and low-resource compression coding.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

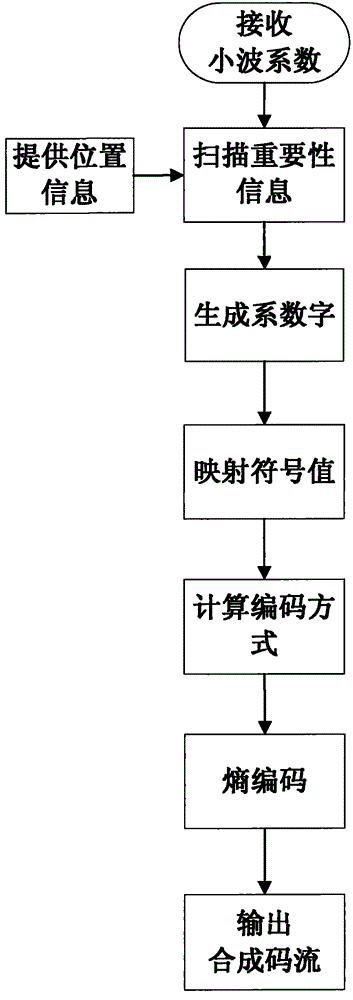

[0042] The present invention will be further described below in conjunction with the accompanying drawings.

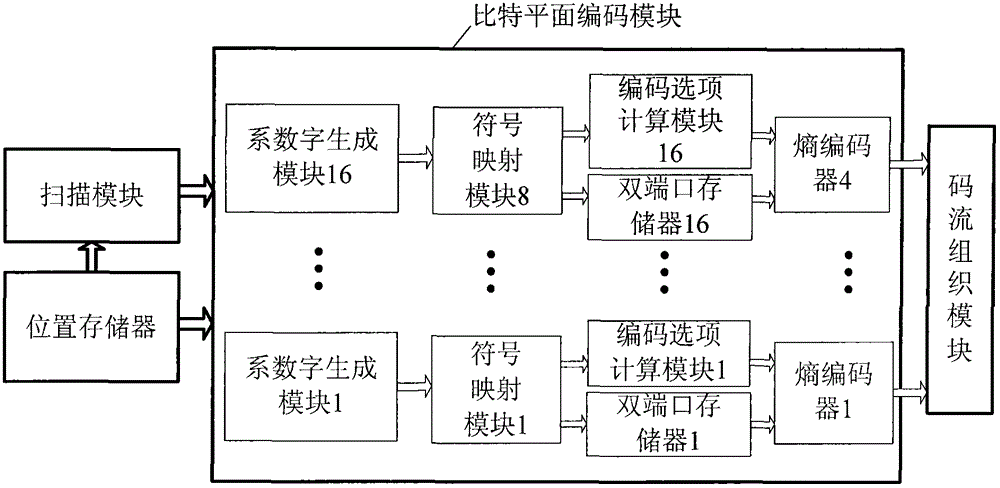

[0043] refer to figure 1 , the hardware structure of the present invention is as follows:

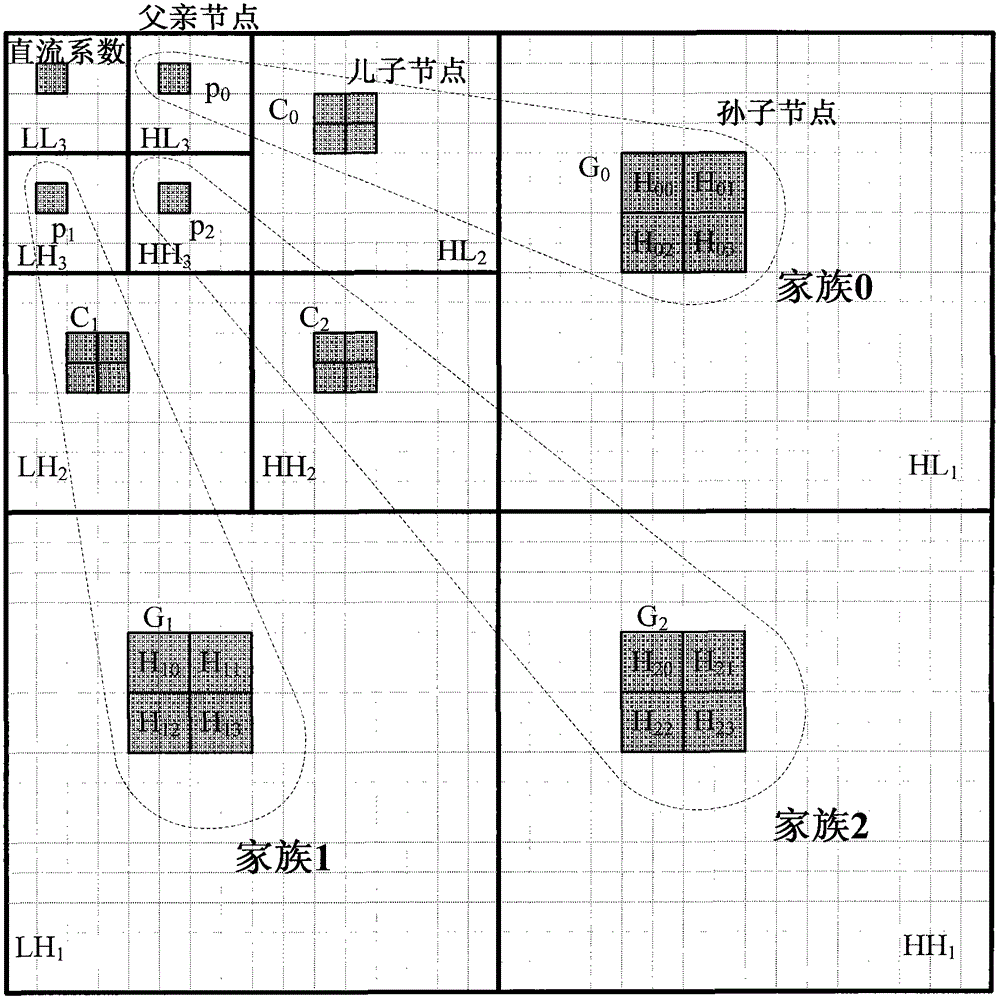

[0044] The hardware structure of the present invention comprises a scanning module, a position memory, a bit-plane encoding module and a code stream organization module; the output ends of the position memory are connected to the scanning module and the input ends of the bit-plane encoding module respectively, and the output ends of the scanning module are connected to the input ends of the bit-plane encoding module. The input end of the bit-plane encoding module is connected, and the output end of the bit-plane encoding module is connected with the input end of the code stream organization module.

[0045] The scanning module performs "OR" operation on the 16 bit planes of the wavelet coefficients in each subset to obtain the importance information; the location memory provide...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More