Manufacture method of semiconductor device provided with metal grid lamination

A manufacturing method and a metal gate technology, which are applied in the direction of semiconductor devices, etc., can solve problems such as poor filling effect and difficult filling of interlayer dielectric layer 17, and achieve the effect of small aspect ratio and simplified manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

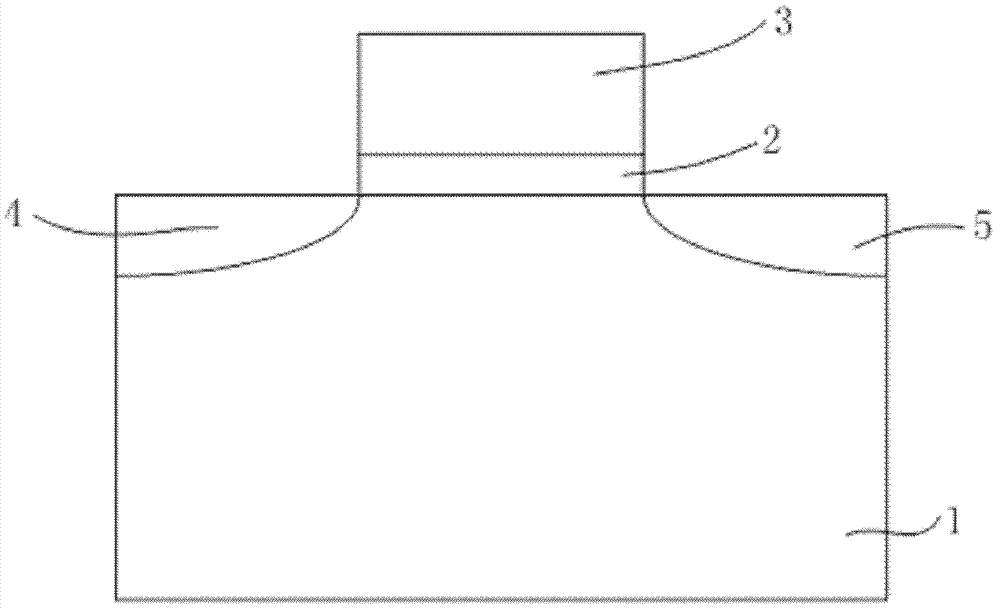

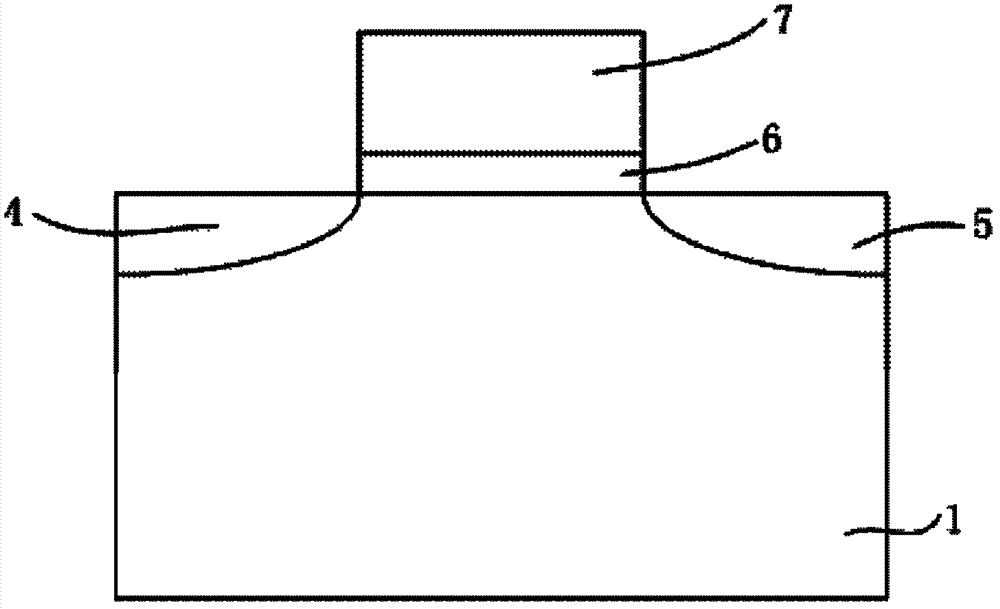

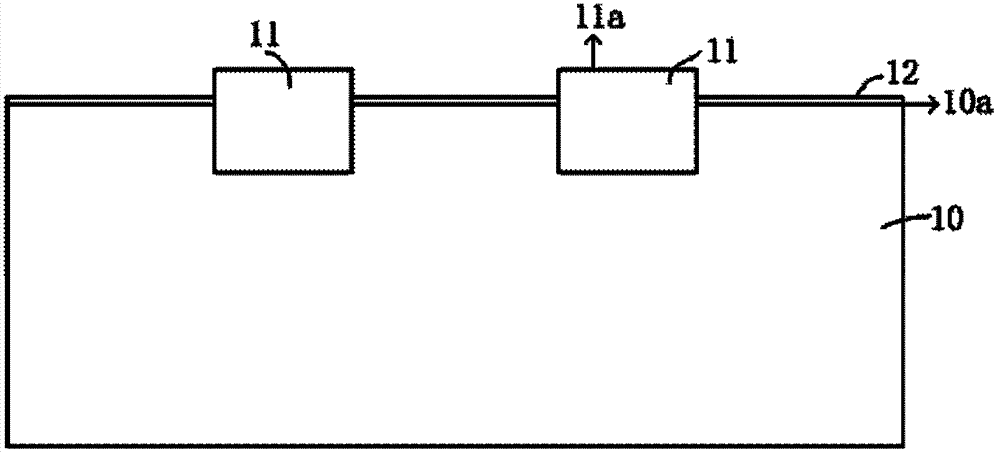

[0056] As mentioned above, the problem to be solved by the present invention is to provide a method for manufacturing a semiconductor device with metal gate stacks, so that the method can form polysilicon dummy gates with the tops at the same height, and then obtain the top at the same height. The high metal gate stack avoids a series of problems caused by the fact that the tops of the polysilicon dummy gates are not at the same height in the process of manufacturing the semiconductor device.

[0057] In the present invention, after the shallow trench isolation structure whose top is higher than the surface of the semiconductor substrate is formed on the semiconductor substrate, a filling layer is deposited on the semiconductor substrate formed with the shallow trench isolation structure, and the structure beyond the shallow trench isolation structure is removed. The filling layer on the top, by controlling the process accuracy when removing the filling layer, the surface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More