Standard logic process-compatible difference framework NVM (Non-Volatile Memory) unit

A memory cell and logic technology, applied in the field of differential architecture NVM memory cells, to achieve the effects of improving stability, reducing the influence of offset, and improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

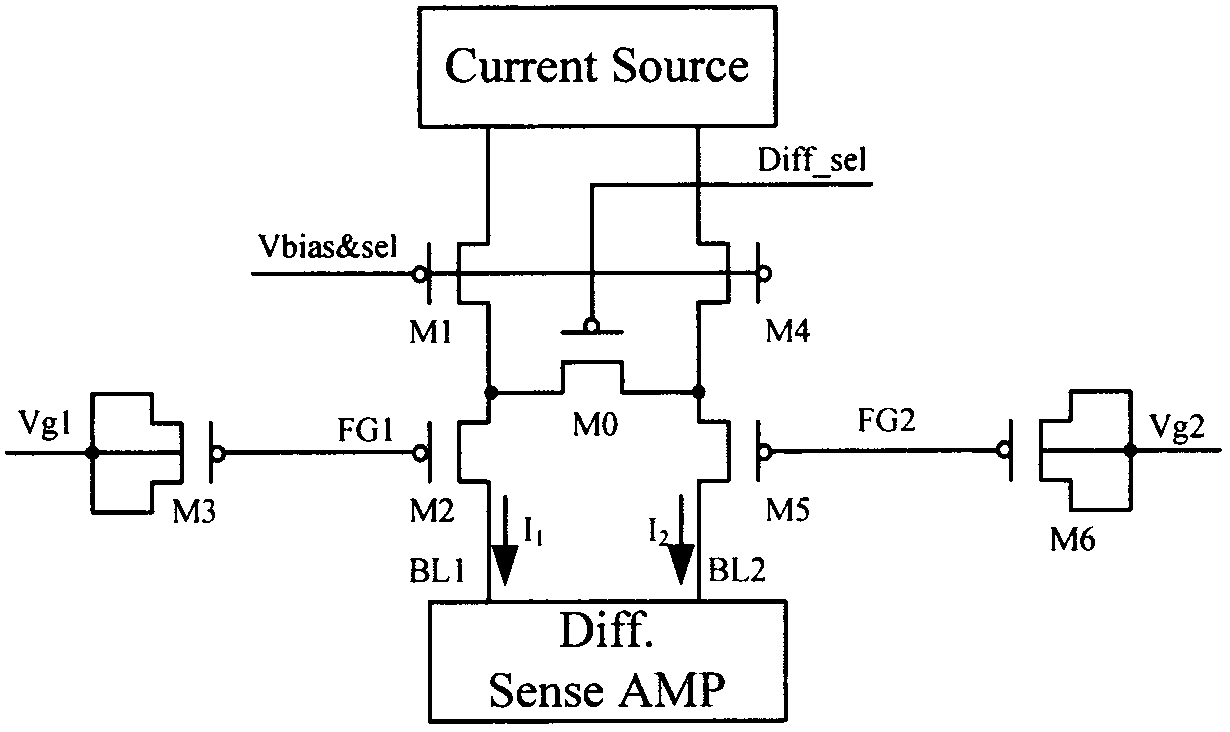

[0030] see figure 1 As shown, the uppermost module is a constant current source, which is usually implemented by a MOS current source operating in the saturation region. Its advantage is that it is compatible with standard processes and the current is stable. MOS transistor M1 and MOS transistor M4 are selection transistors, the gate of which is connected to the gate voltage Vbias&sel of the word line, the source is connected to the above-mentioned constant current source module, the drain is respectively connected to MOS transistor M2 and MOS transistor M5, and the substrate is directly connected to the source Usually, the gating voltage is high voltage, so there are special requirements for the size of the tube and the thickness of the gate oxide, and the two gating tubes also bear a certain bias effect.

[0031] MOS transistor M2 and MOS transistor M5 are programming transistors, their gates are respectively connected to the gates of MOS transistor M3 and MOS transistor M6 ...

Embodiment 2

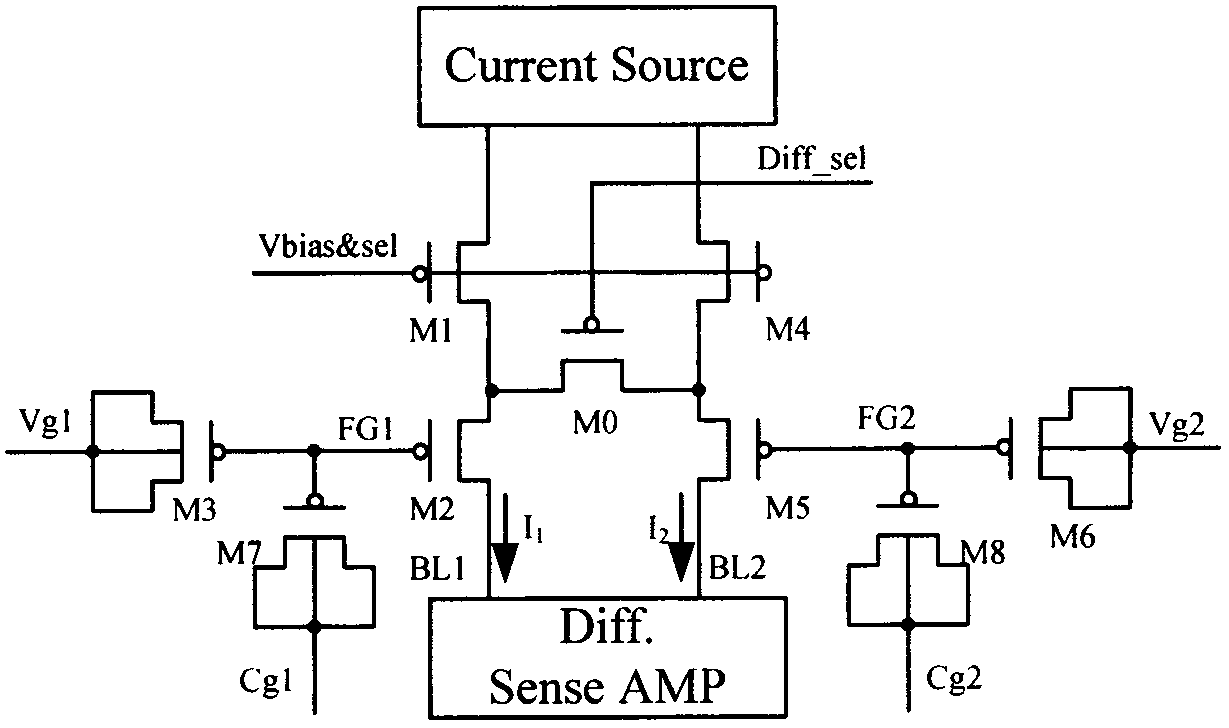

[0034] see figure 2 shown in figure 1 on the basis of figure 2 Two more identical small capacitance MOS transistors M7 and MOS transistor M8 are added to the floating gate, and the nodes Vg1 and Cg2 are connected, and Vg2 and Cg1 are connected, so that cross-coupling is realized, which can improve the reading stability more effectively sex. The change of its connection method is that there are two more MOS transistors M7 and MOS transistor M8, and the connection method of MOS transistor M7 and MOS transistor M3 is exactly the same, and the gate is shared with the MOS transistor M2, and then the source and drain substrates are all connected. Its role is relative to capacitance. The connection method of MOS tube M8 is exactly the same as that of MOS tube M7.

Embodiment 3

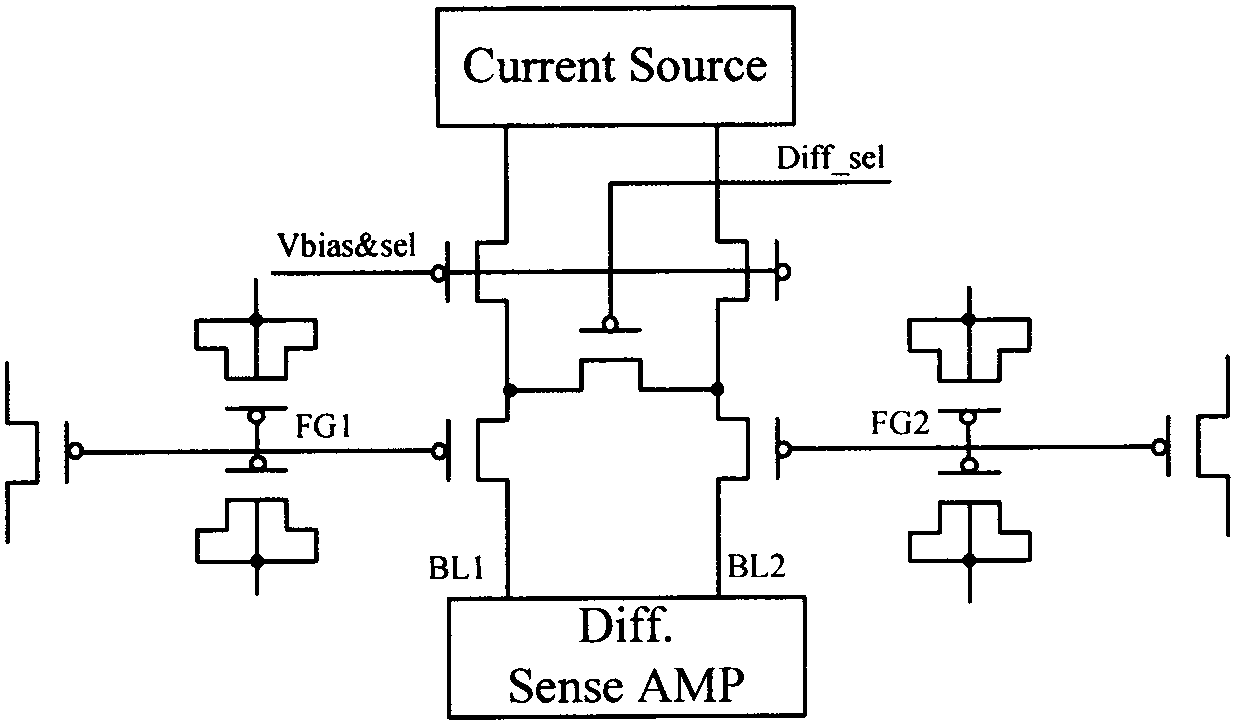

[0036] see image 3 shown in figure 2 on the basis of image 3 Two more identical MOS transistors are added on the floating gate. The connection and function of these two transistors are the same as those of MOS transistor M2 and MOS transistor M5, but they are only responsible for writing operations, that is, separate read and write methods are used here. The advantage of this is that it can not only retain various advantages of the read circuit of the differential structure, but also maintain the fast and effective writing effect.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More