Method for identifying short-circuit path in integrated circuit layout verification process

A technology of integrated circuits and identification methods, which is applied in the fields of electrical digital data processing, special data processing applications, instruments, etc., and can solve problems such as complex connection relationships, increased time spent, and difficulty in finding short-circuit paths.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

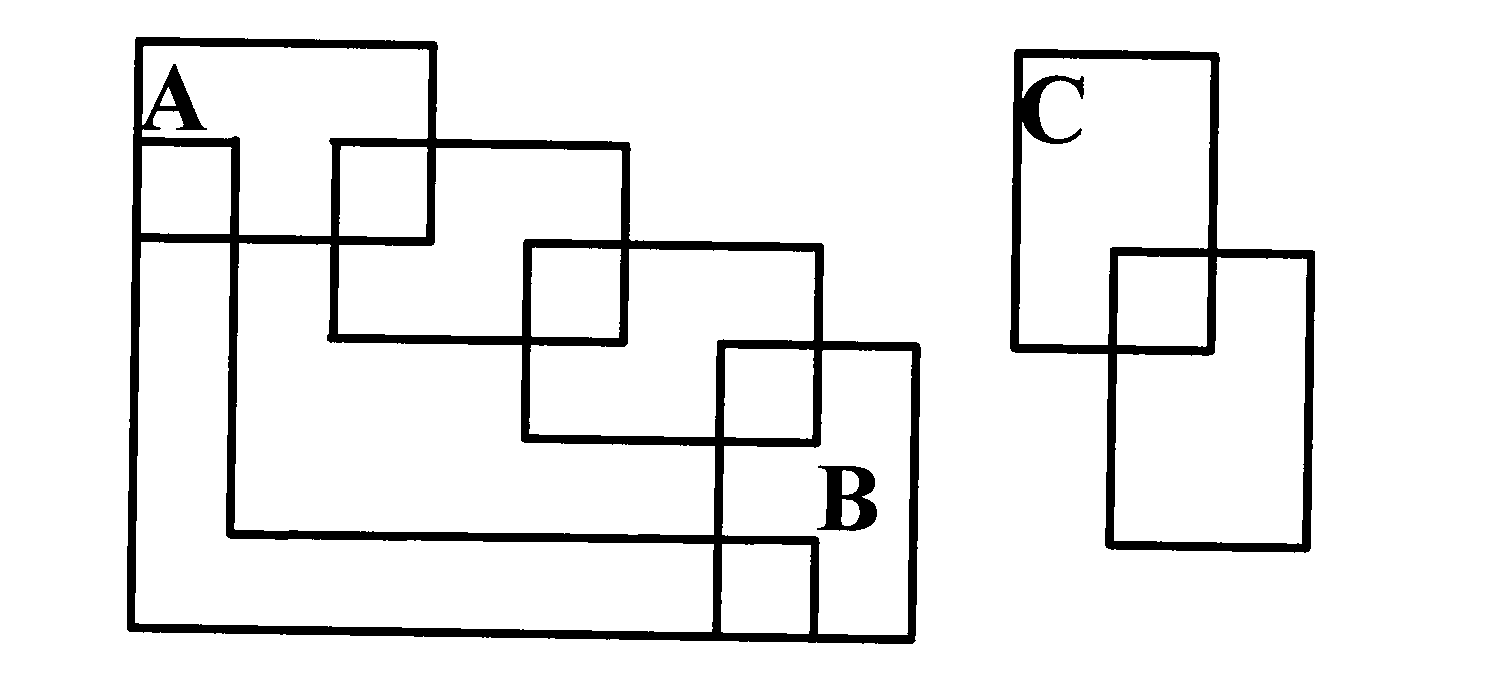

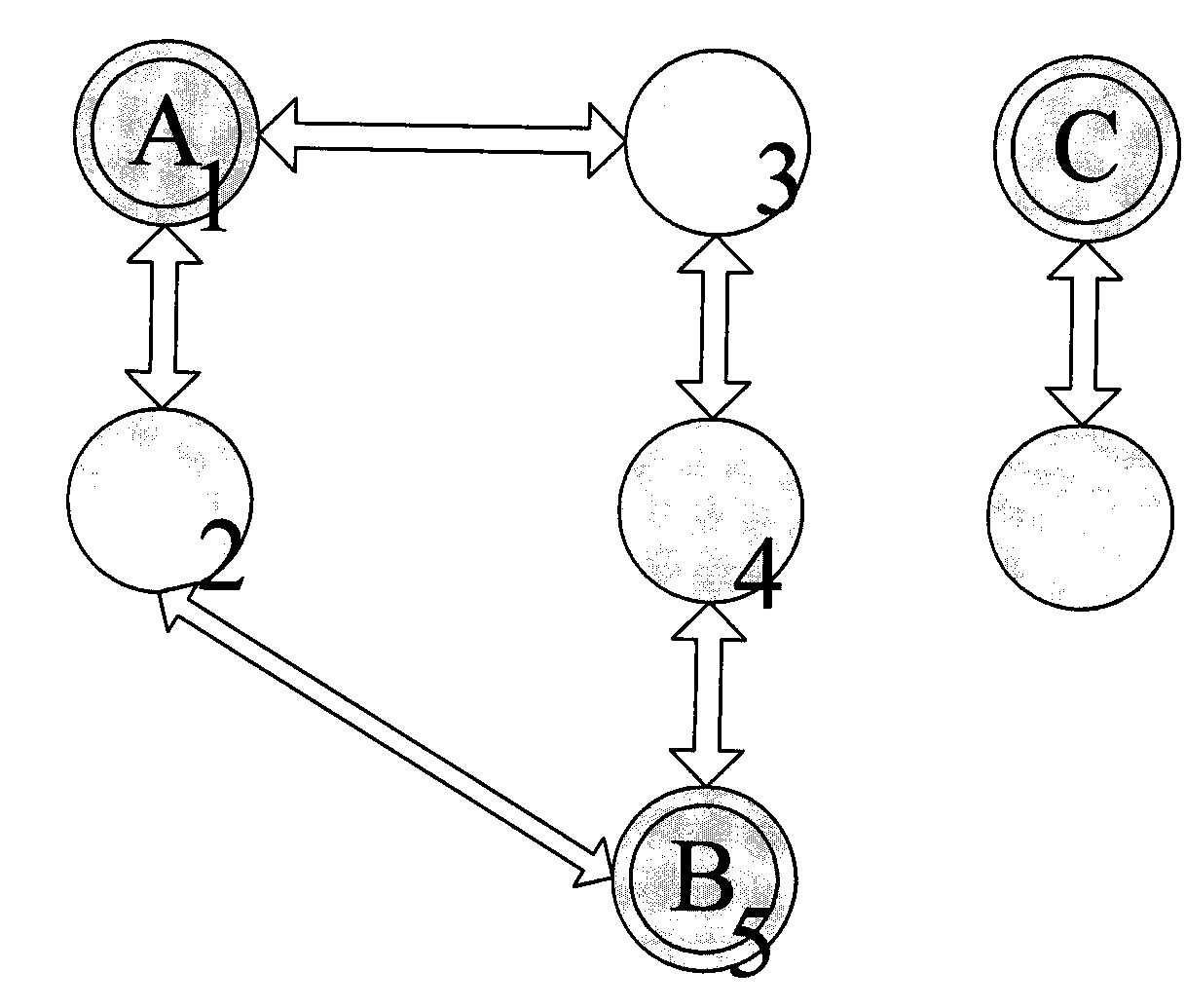

[0011] Step (1) Initialize, read in the connection relationship between graphs, and build an undirected graph; figure 1 As shown, sequentially read in the graphic connection relationship in the layout, and construct the following figure 2 The undirected graph shown. For the storage of undirected graphs, adjacency matrix or adjacency list can be selected according to its sparseness.

[0012] Step (2) identifies the vertex corresponding to the graph where each label is located as the target point; figure 2 As shown, vertices identified as A, B, C.

[0013] Step (3) decomposes the undirected graph into independent subgraphs of a plurality of connected relations; in this method, a subgraph division algorithm based on equivalence class merging is adopted, and the following steps are performed in turn:

[0014] a) Traversing the undirected graph, numbering each vertex from small to large

[0015] b) Set the two vertices connected by each edge in the graph as an equivalence rel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More