Implementation method of qc-ldpc decoder for improving node processing parallelism

A technology for node processing and implementation methods, which is applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc., to achieve less hardware resources and strong practicability , the effect of reducing critical path delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0080] Using the design method of the QC-LDPC decoder proposed by this patent to improve the parallelism of node processing, the present invention will be described in detail below taking LDPC (8176, 7154) as an example.

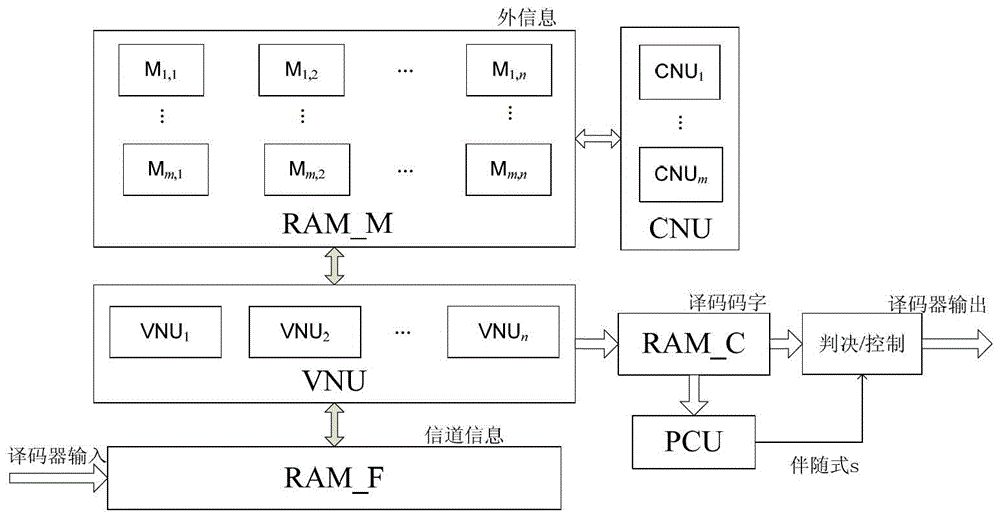

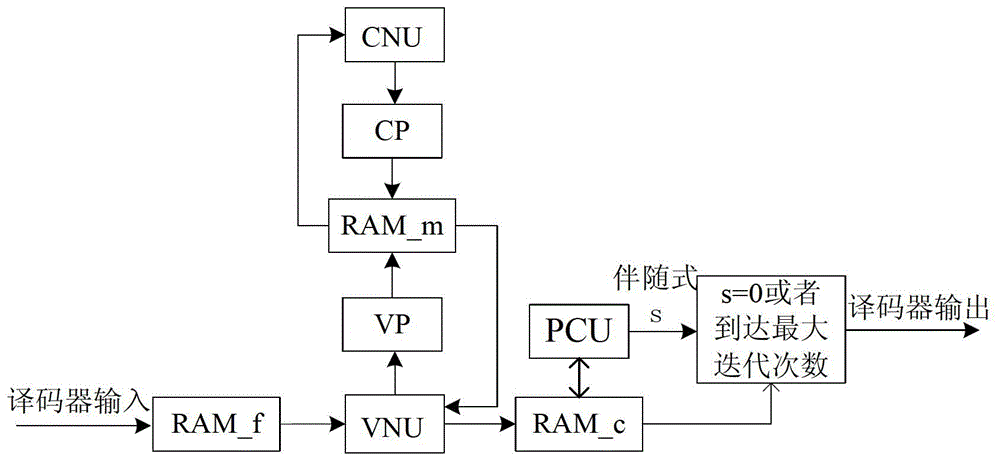

[0081] Such as figure 2 As shown, LDPC(8176,7154) is a QC-LDPC code (that is, a quasi-cyclic shift LDPC code), and its parity check matrix is composed of 2×16 L×L (L=511) circulant matrices. The check matrix size is M×N=1022×8176, A i,j is a 511×511 circular matrix, A i,j There are two non-zero elements in each row and column of , that is, A i,j The row weight of is 2, so the row weight of the check matrix is 2×16=32, and the column weight is 2×2=4. The check matrix structure is as follows:

[0082] A 1,1 A 1,2 . . . ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More