Method for forming fin transistors

A fin transistor and fin technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of low yield and poor electrical performance uniformity of fin transistors, and achieves good thickness uniformity and thickness. Controllable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] It can be seen from the background technology that the fin transistors formed in the prior art have poor electrical performance uniformity and low yield rate. Therefore, the inventors of the present invention researched the fin transistor formation methods in the prior art and found that the fin transistors in the prior art The method for forming a transistor includes the following steps:

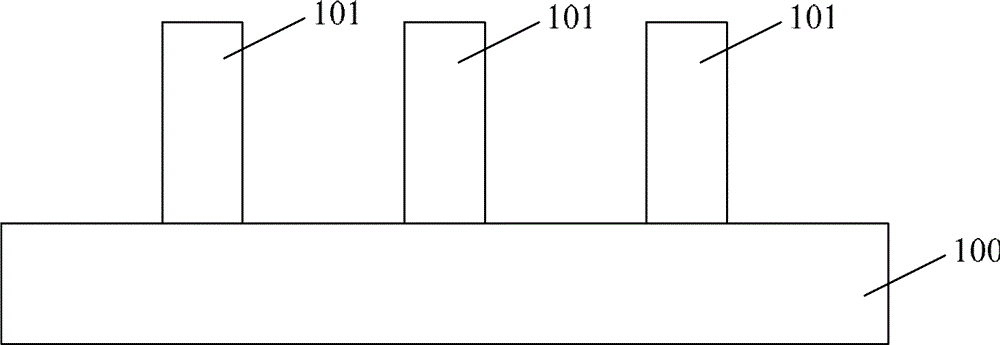

[0015] Please refer to figure 2 , providing a substrate 100, the surface of the substrate 100 is formed with a plurality of fins 101;

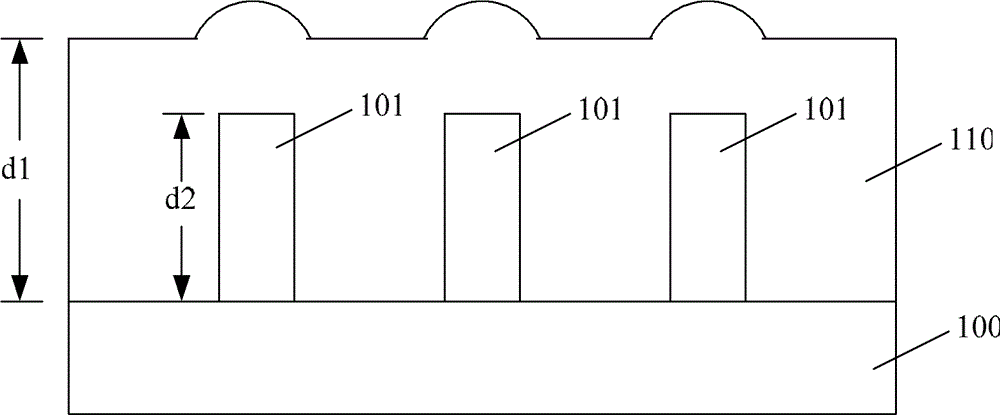

[0016] Please refer to image 3 , forming a polysilicon layer 110 across the fin portion 101 on the surface of the substrate 100; the polysilicon layer 110 is used as a dummy gate of the fin transistor, the polysilicon layer 110 covers part of the sidewall of the fin portion 101, and the polysilicon layer The thickness (d1) of 110 is greater than the thickness (d2) of the fin portion 101;

[0017] The formation process of the polysilicon layer 11...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More