Multi-FPGA interconnection structure and logic partitioning method oriented to high-performance computing

A high-performance computing and logical division technology, applied in the field of high-performance computing, can solve problems such as no effective solutions have been found, and achieve the effects of low power consumption, accelerated design implementation, and efficient mapping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the object, technical solution and advantages of the present invention clearer, the specific implementation method of the present invention will be further described below with reference to the accompanying drawings.

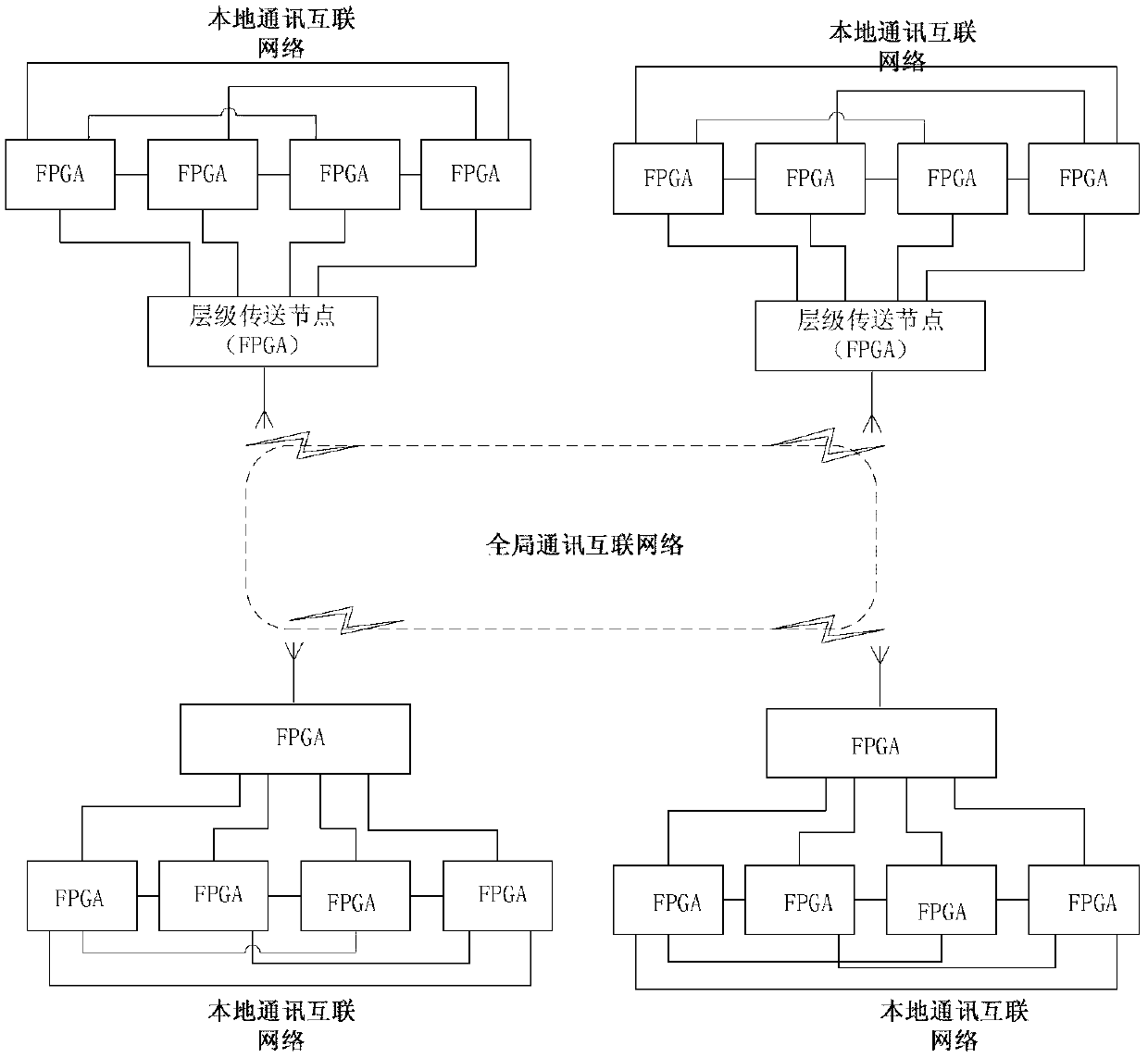

[0029] figure 1It is a topology structure according to an embodiment of the present invention. As shown in the figure, the topology structure includes two two-level communication interconnection networks: a local communication interconnection network and a global communication interconnection network. Among them, each node in the local communication network is fully interconnected with wired communication, and any two nodes in the same local communication network can directly communicate with one-hop; the global communication network in the example uses high-speed wireless radio frequency interconnection RF-I, any Communication between two nodes not in the same local communication network needs to pass through the global communication net...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More