Patents

Literature

77results about How to "Quick map" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

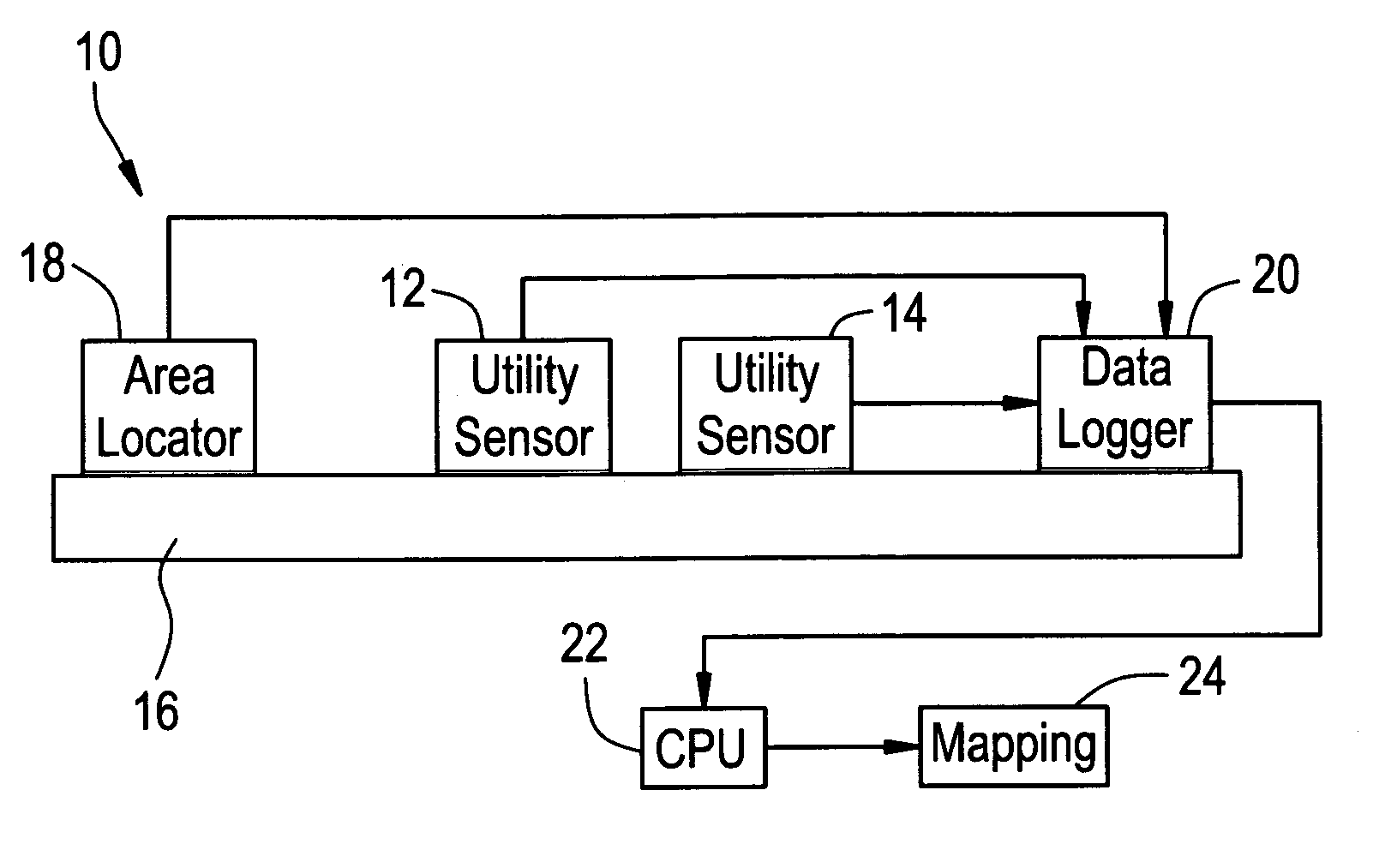

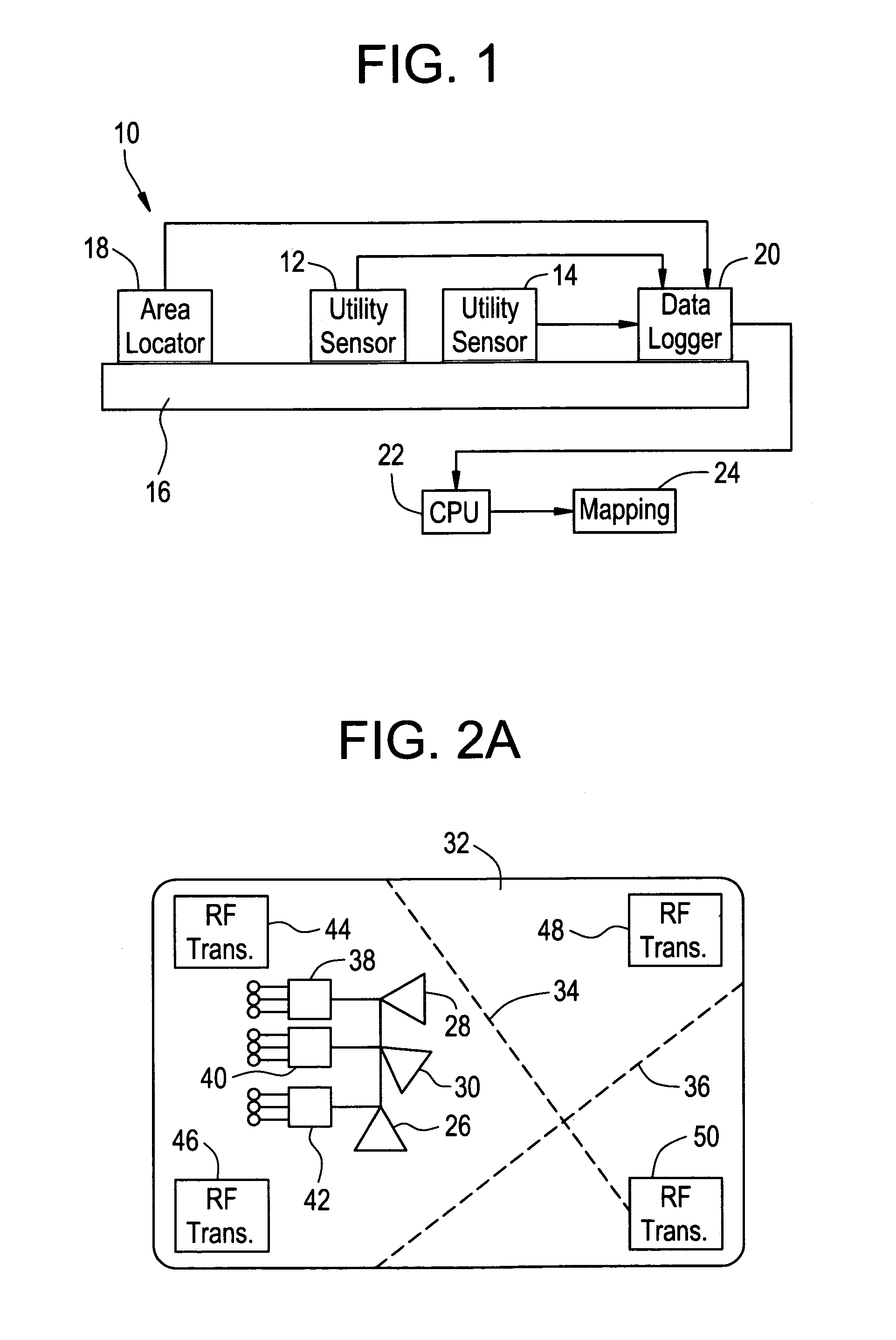

Method and apparatus for detecting, mapping and locating underground utilities

InactiveUS6999021B2Quick checkQuick mapDetection using electromagnetic wavesRadio wave reradiation/reflectionLocation dataCartography

The method and device for locating underground utilities within an area includes traversing the area with a plurality of underground utility sensors and obtaining area location data to locate the area traversed. The sensor data and area location data are used to map the location of one or more utilities within the area traversed.

Owner:ENSCO INC

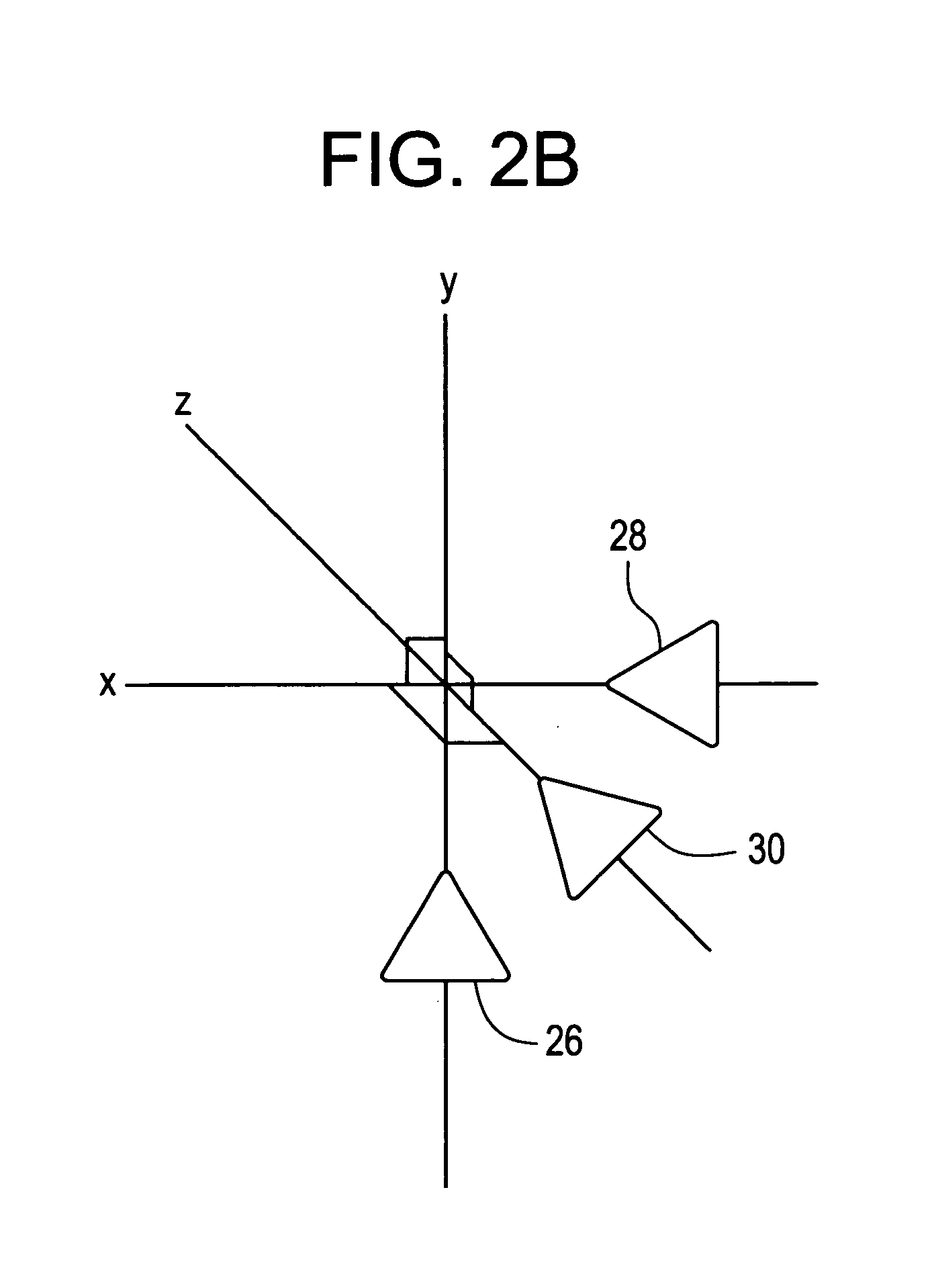

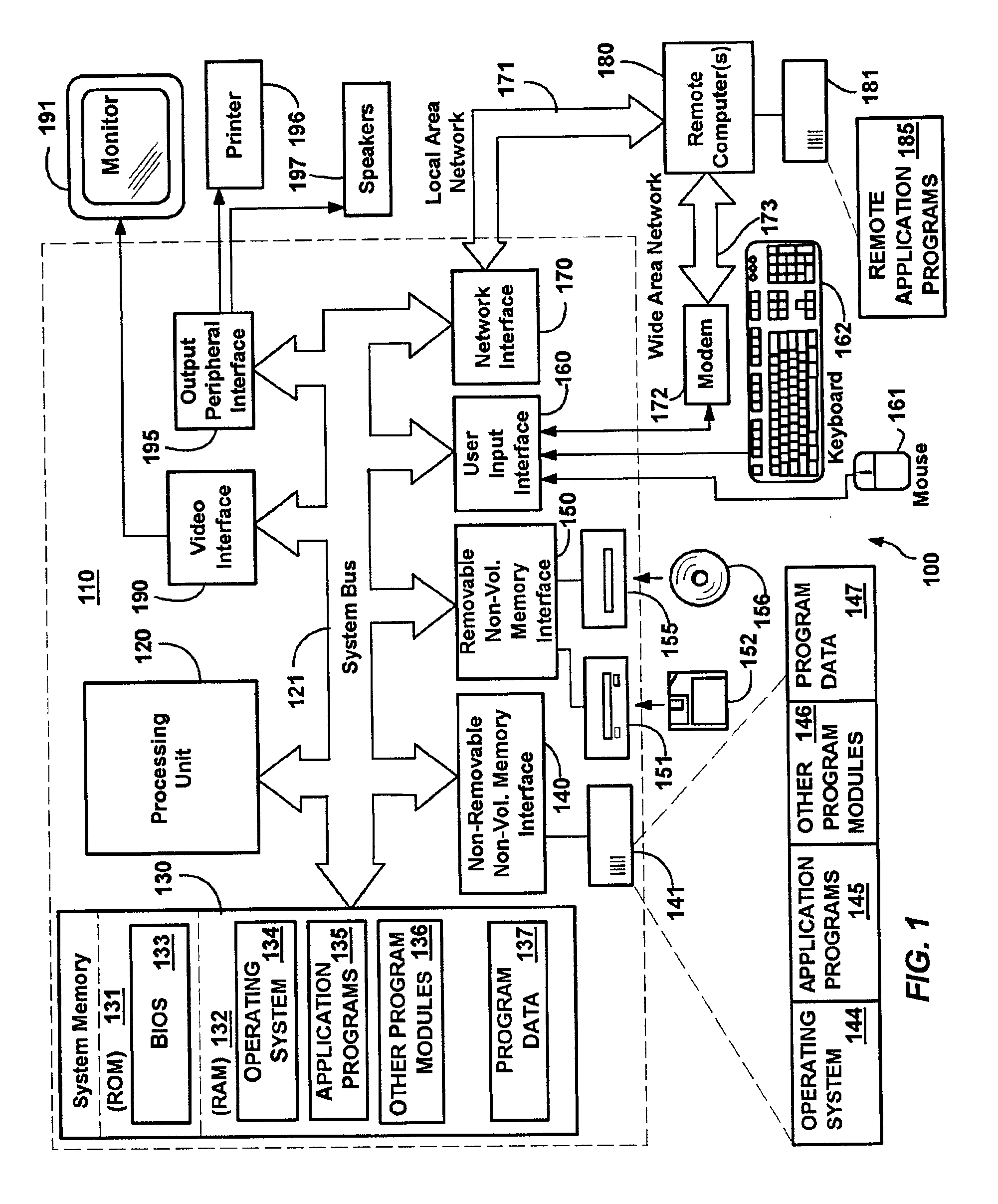

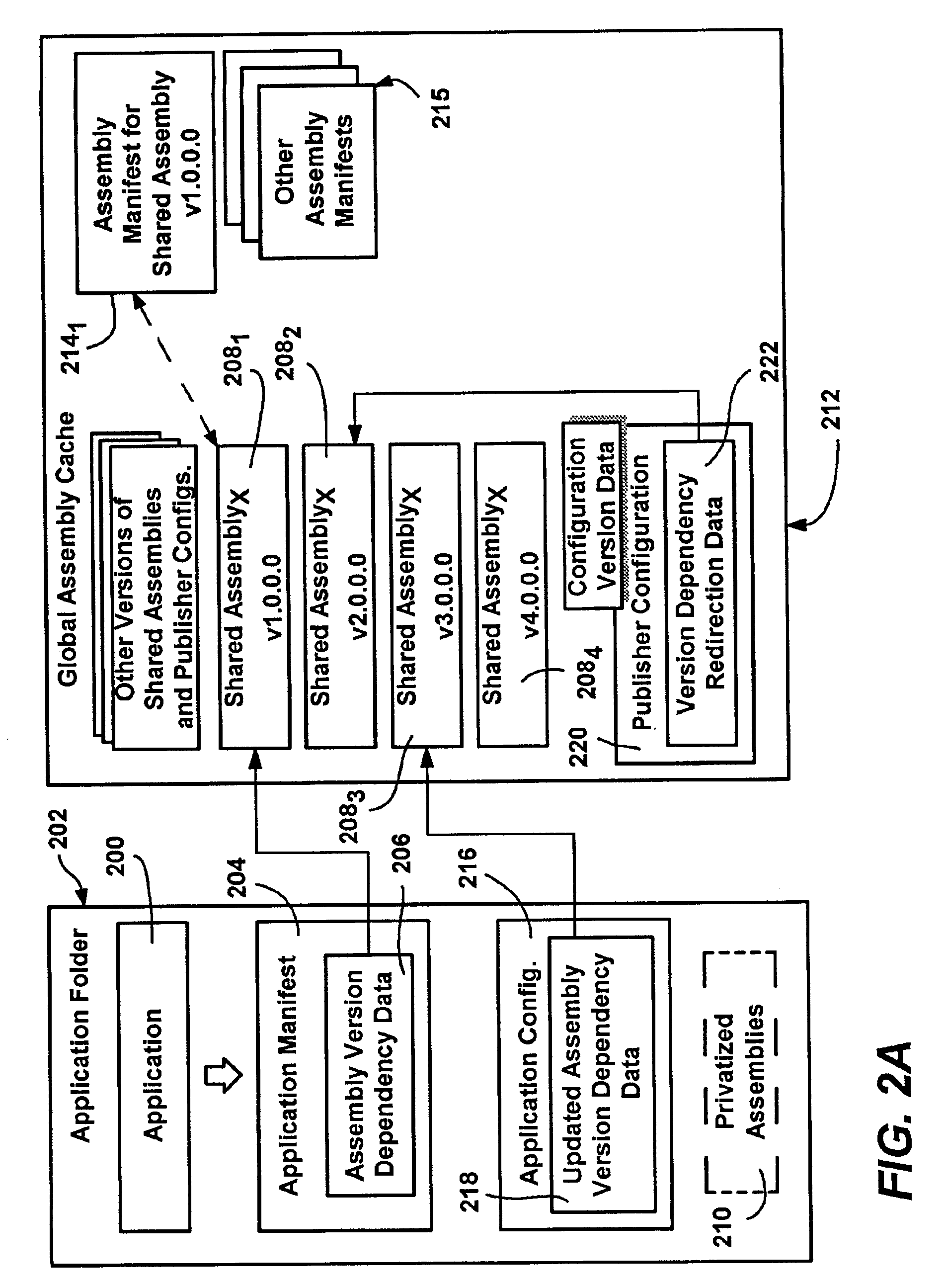

Configurations for binding software assemblies to application programs

A method, system and infrastructure that allow an application to run with specified versions of assemblies bound thereto, while allowing the application author, assembly publisher and / or an administrator to change the originally-specified version as desired. Each assembly may exist and run side-by-side on the system with other versions of the same assembly being used by other applications. An application manifest specifies any desired assembly versions, which may be redirected to another version (overridden) by an application configuration. A publisher configuration provided by an assembly publisher can similarly override the specified version. Lastly, an administrator configuration is capable of overriding other configuration versioning information. A table built from the manifest and any configuration redirection may be accessed during execution to quickly locate the appropriate version. The various configuration data structures themselves may be wrapped as assemblies, thereby enabling versioning of configurations.

Owner:MICROSOFT TECH LICENSING LLC

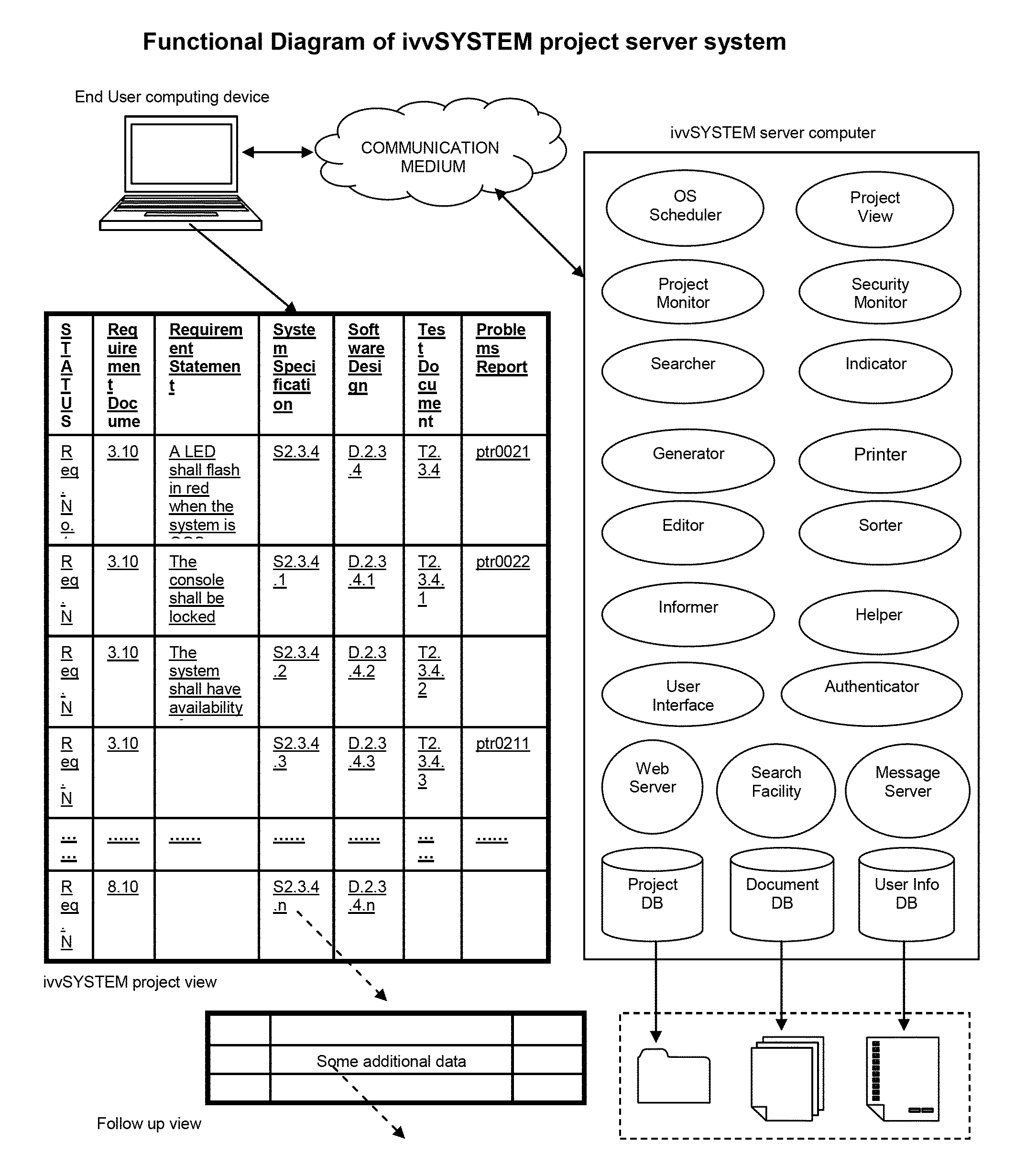

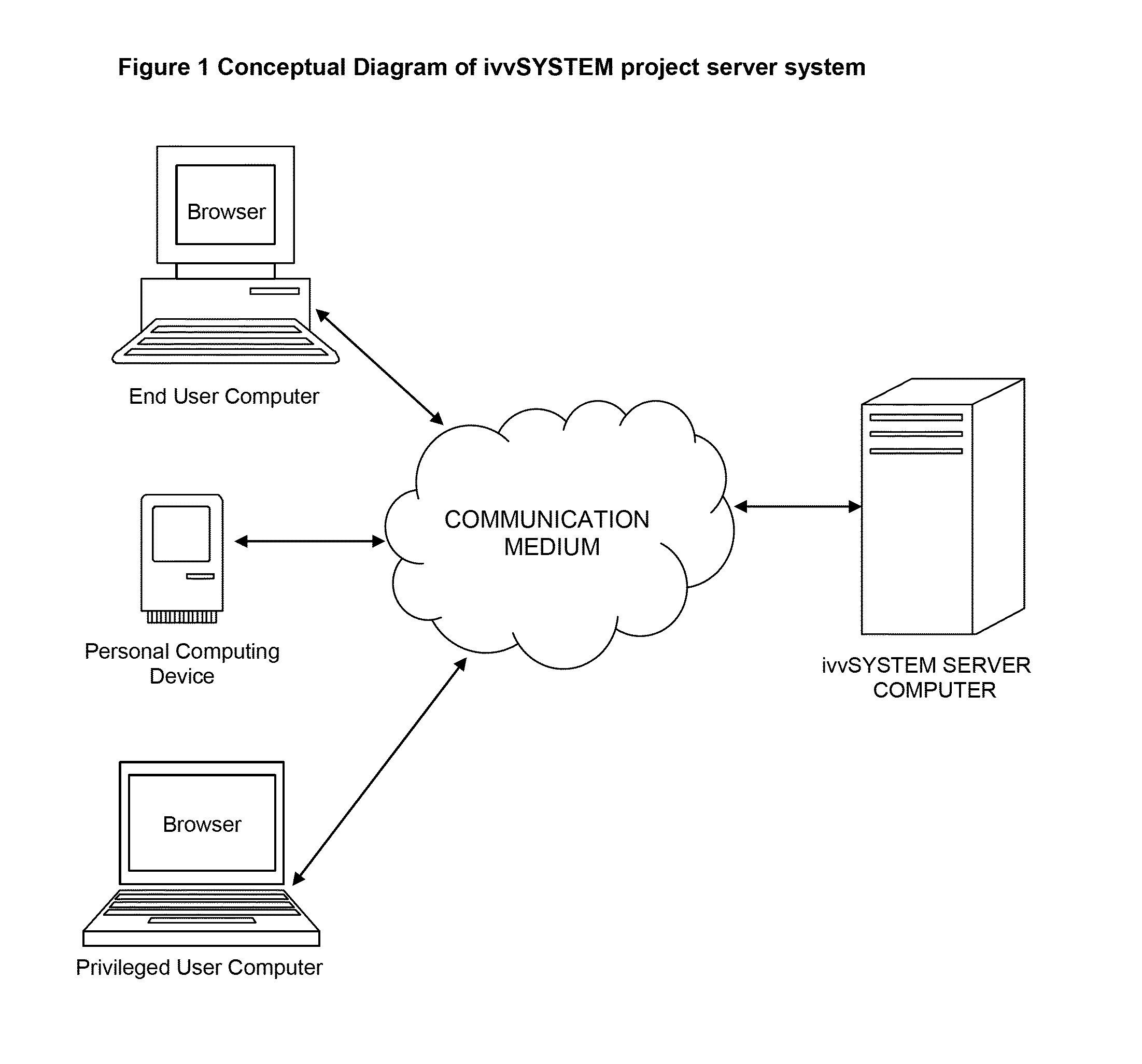

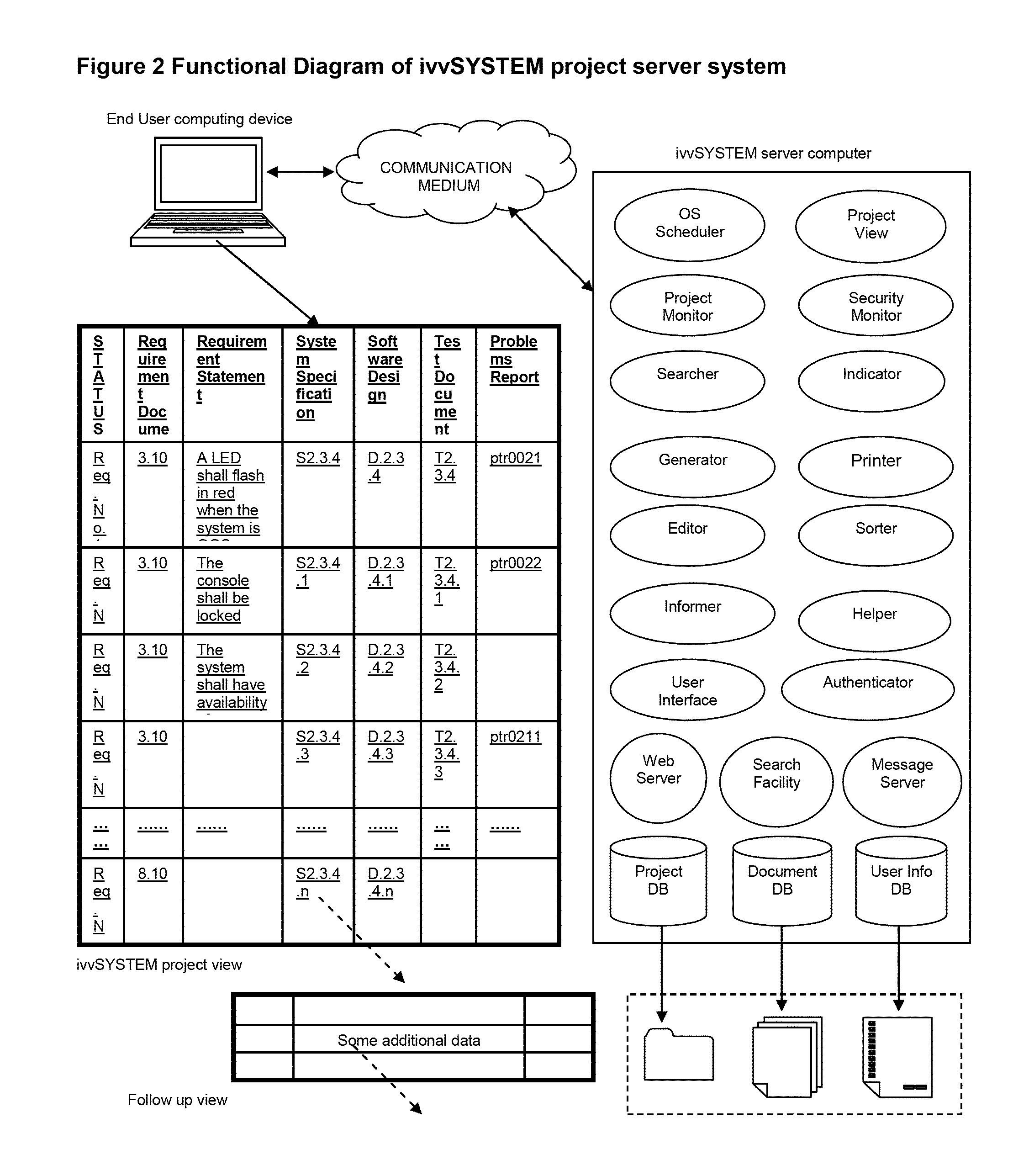

System and method for independent verification and validation

ActiveUS8543620B2Simplifies complex logisticsQuick mapDigital data processing detailsResourcesOperational systemNetwork service

This invention is to solve the high cost of IV&V by simplifying the complex logistics of project management. This is an intelligent project management system comprising a project server computer remotely accessible by a user computing device. The project server computer includes several databases: A database of electronic library which stores documents that are required by the project, a database which stores project data that reflect the state of the project, and a database which stores the user information of privileged users. Several modules are executing in the project server computer to generate the view of the project, to automatically monitor the state of the project, to verify and validate the mapping between multiple documents for requirement traceability, to automatically indicate the state of the project, to automatically provide assistance to the user, to automatically inform the stakeholder on matters related to the project, and to authenticate the privileged user. This intelligent project management system assumes that the server computer contains a standard computer operating system that includes at least a web server, an email server and a search engine facility.

Owner:APLIX RES

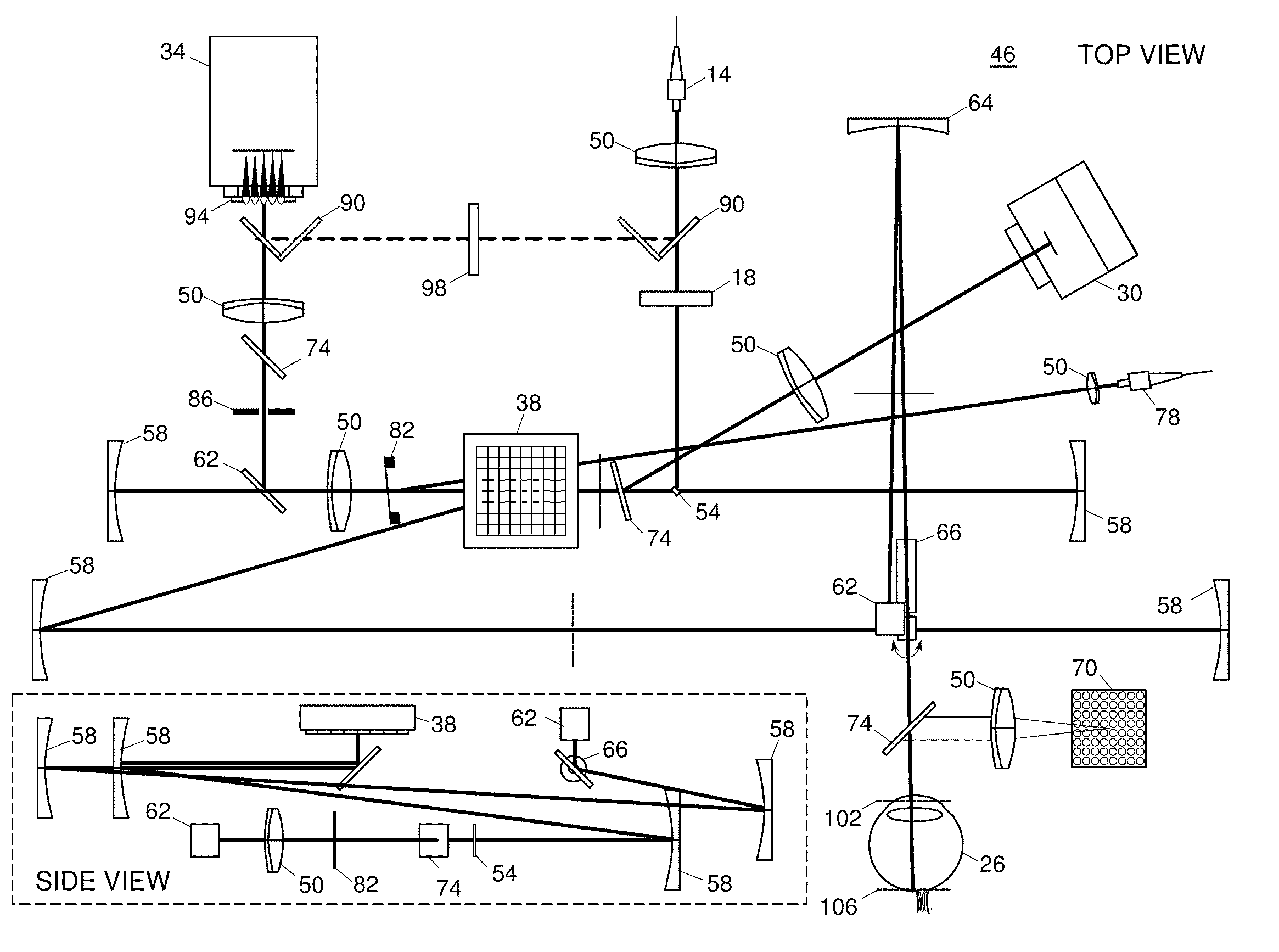

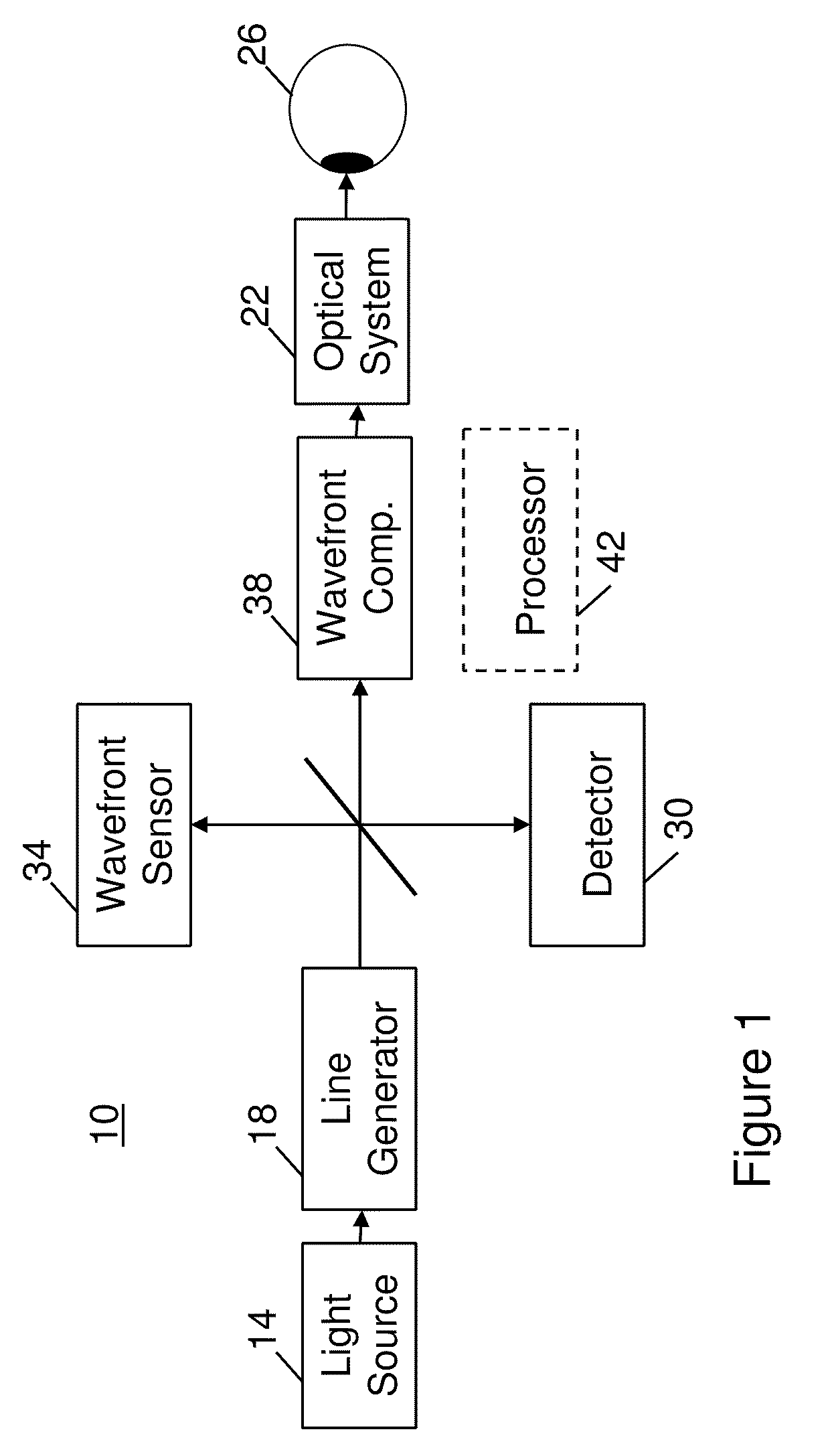

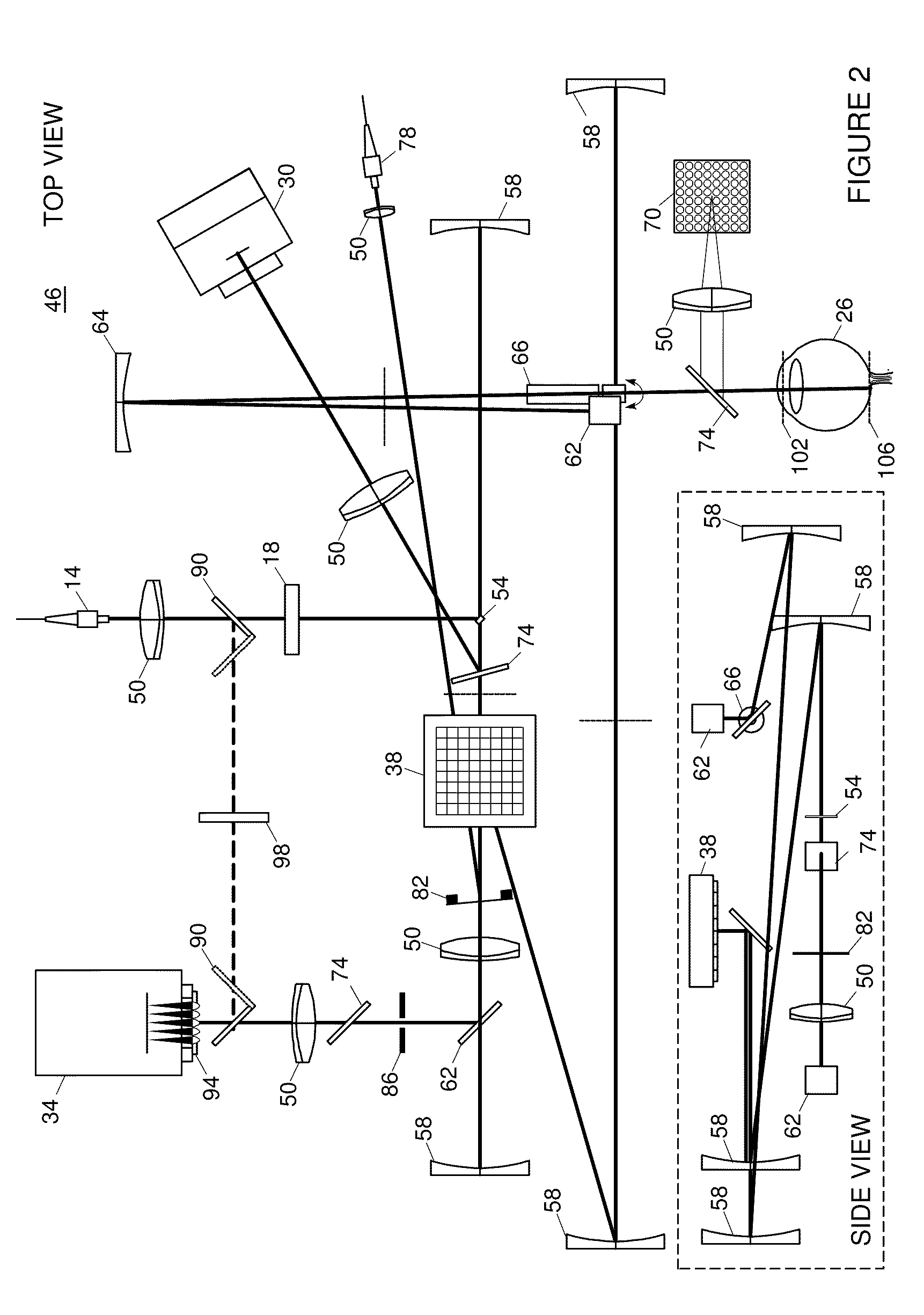

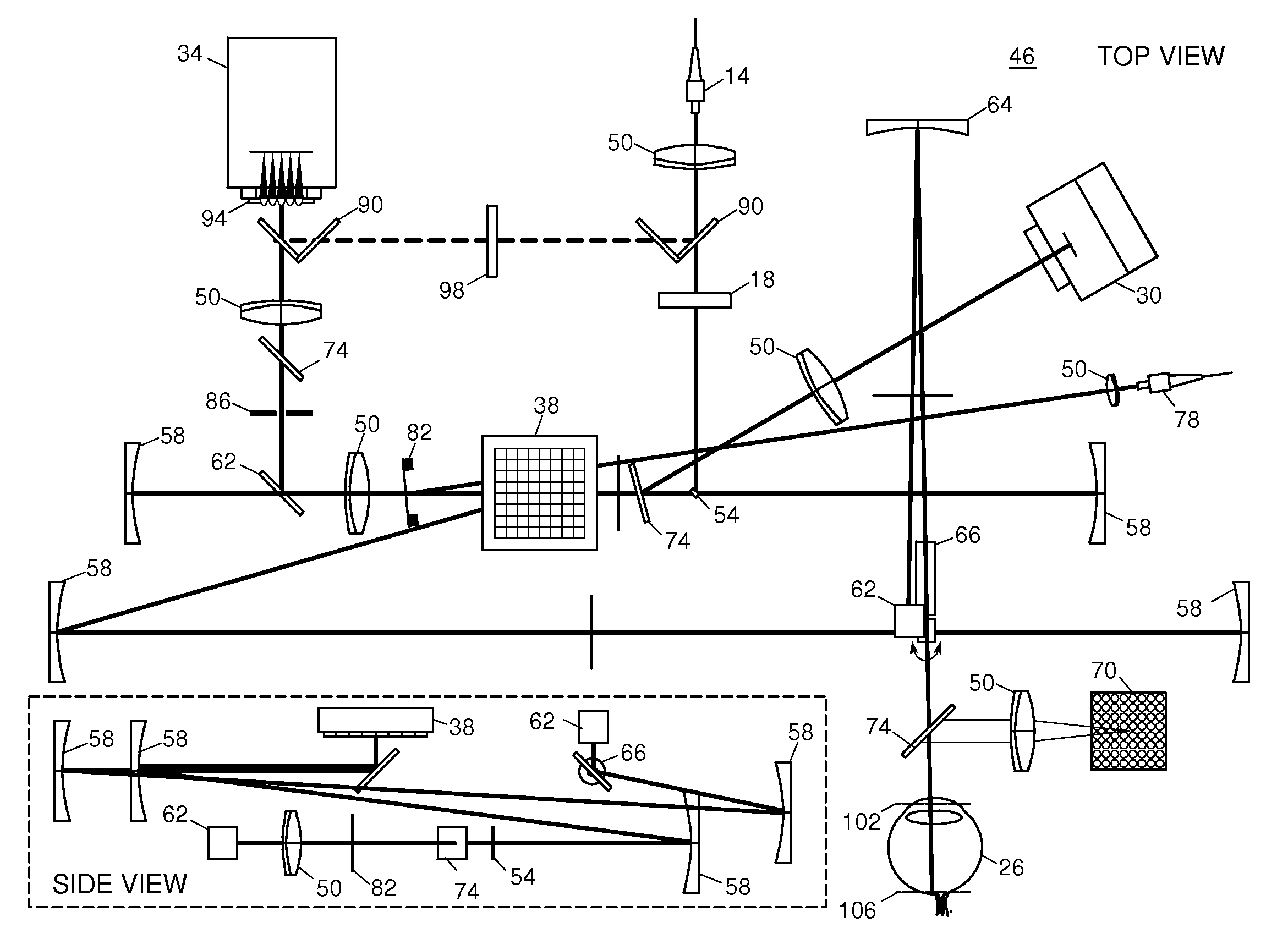

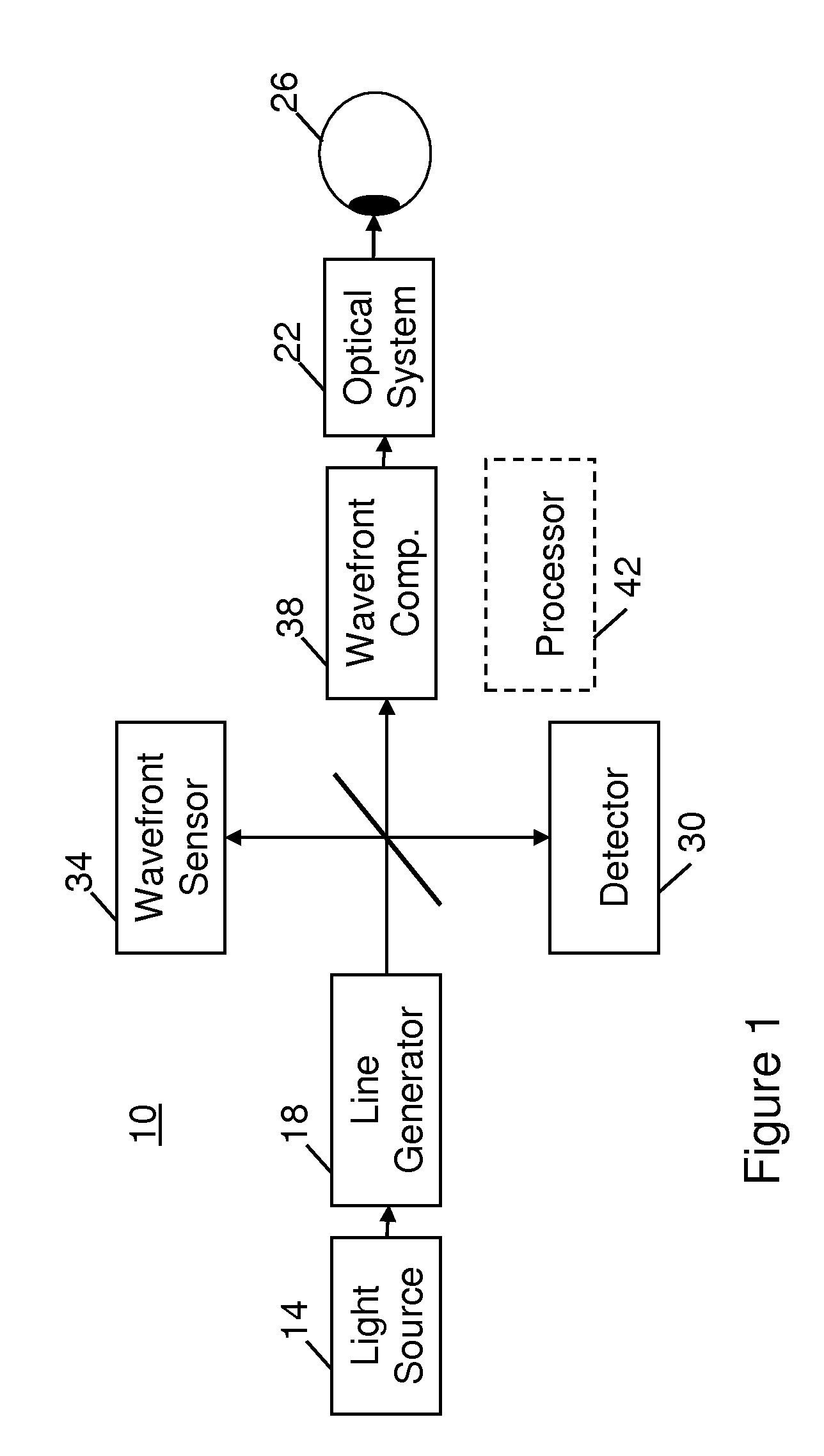

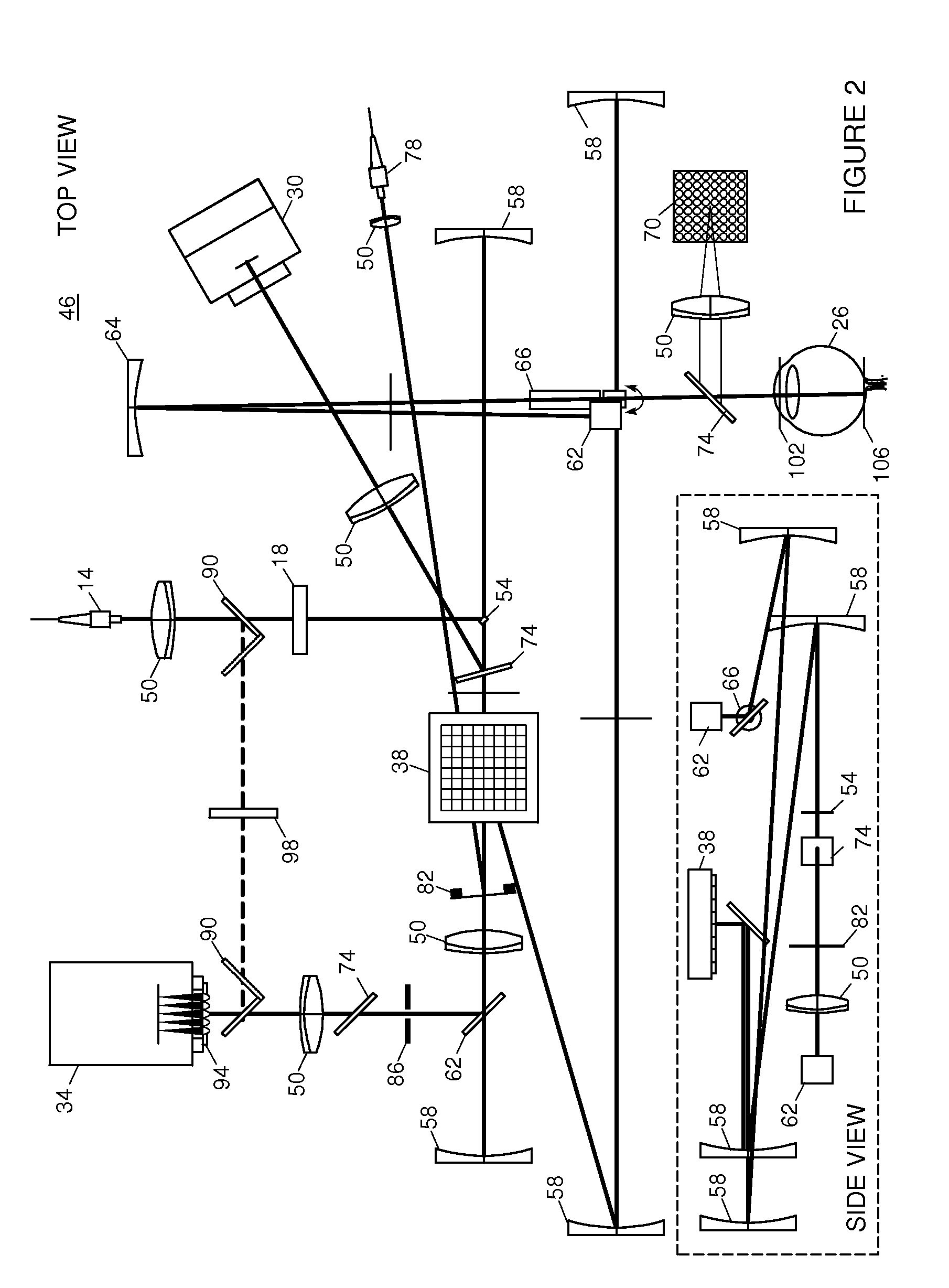

Adaptive optics line scanning ophthalmoscope

ActiveUS8201943B2Improve understandingSimplied optics, high-speed scanning componentsEye diagnosticsOptical ModuleOphthalmoscopes

A first optical module scans a portion of an eye with a line of light, descans reflected light from the scanned portion of the eye and confocally provides output light in a line focus configuration. A detection device detects the output light and images the portion of the eye. A second optical module detects an optical distortion and corrects the optical distortion in the line of light scanned on the portion of the eye.

Owner:PHYSICAL SCI

Adaptive Optics Line Scanning Ophthalmoscope

ActiveUS20100195048A1Advance understanding of visionCompact and simplifiedEye diagnosticsOptical ModuleOphthalmology

A first optical module scans a portion of an eye with a line of light, descans reflected light from the scanned portion of the eye and confocally provides output light in a line focus configuration. A detection device detects the output light and images the portion of the eye. A second optical module detects an optical distortion and corrects the optical distortion in the line of light scanned on the portion of the eye.

Owner:PHYSICAL SCI

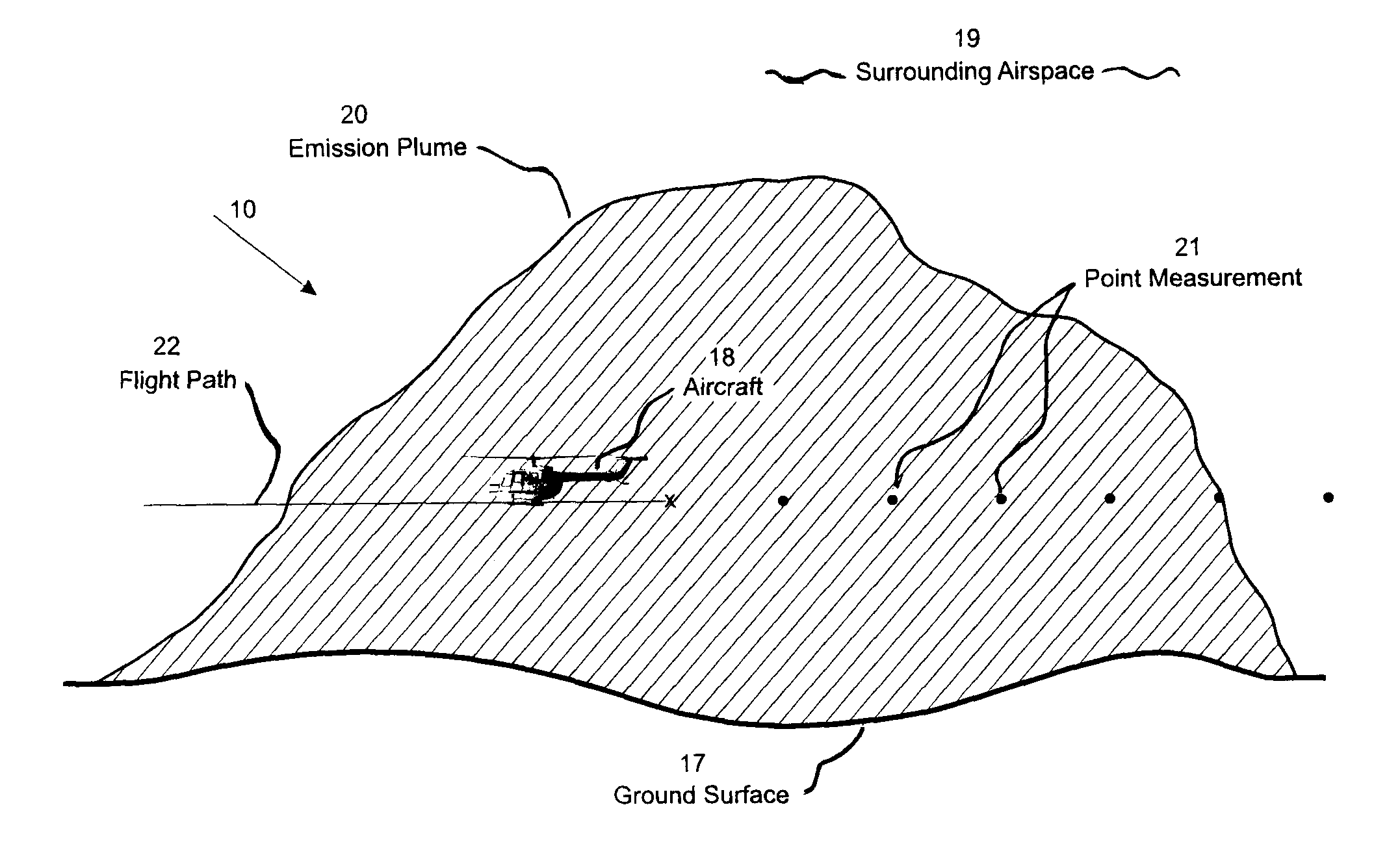

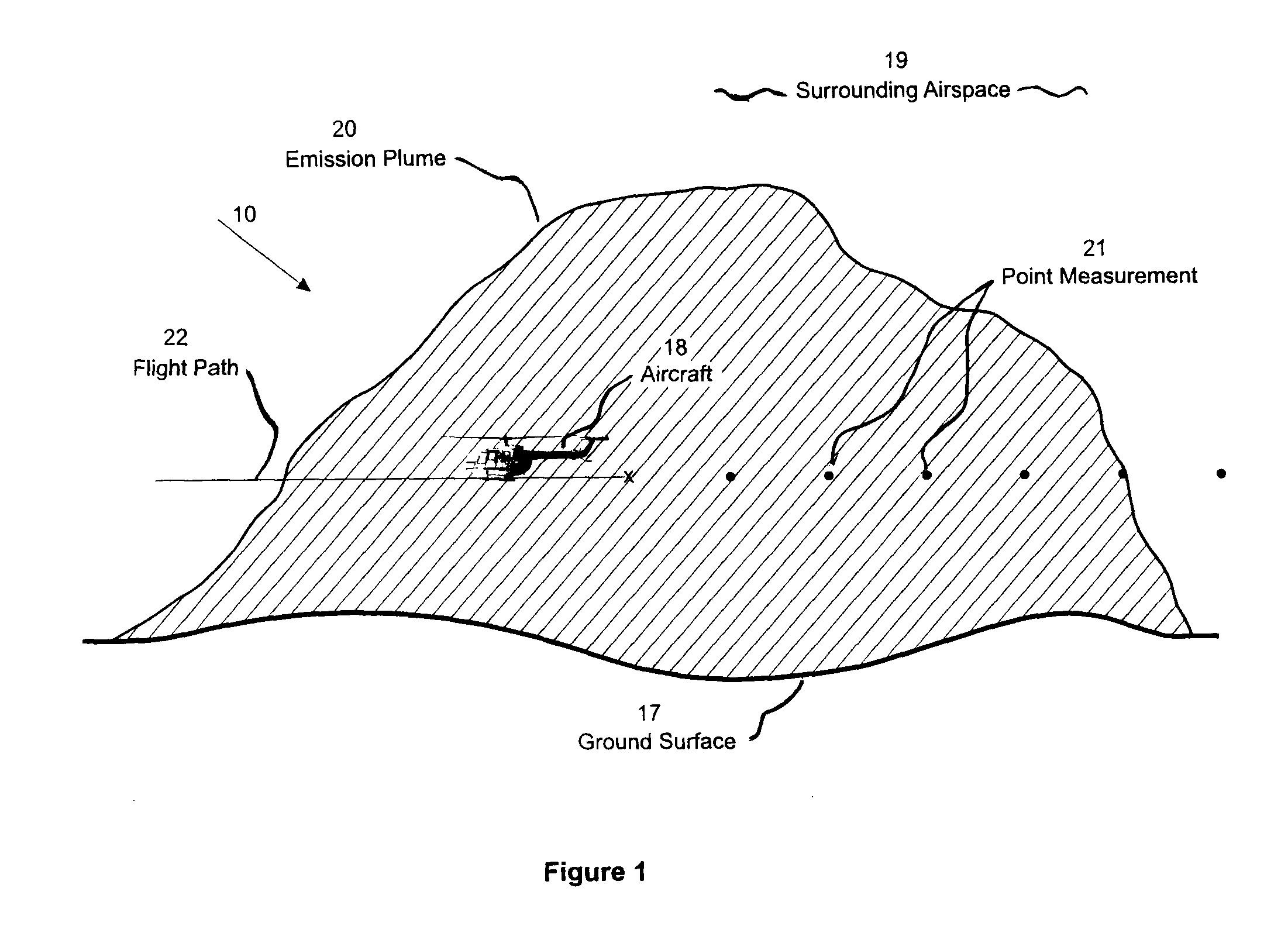

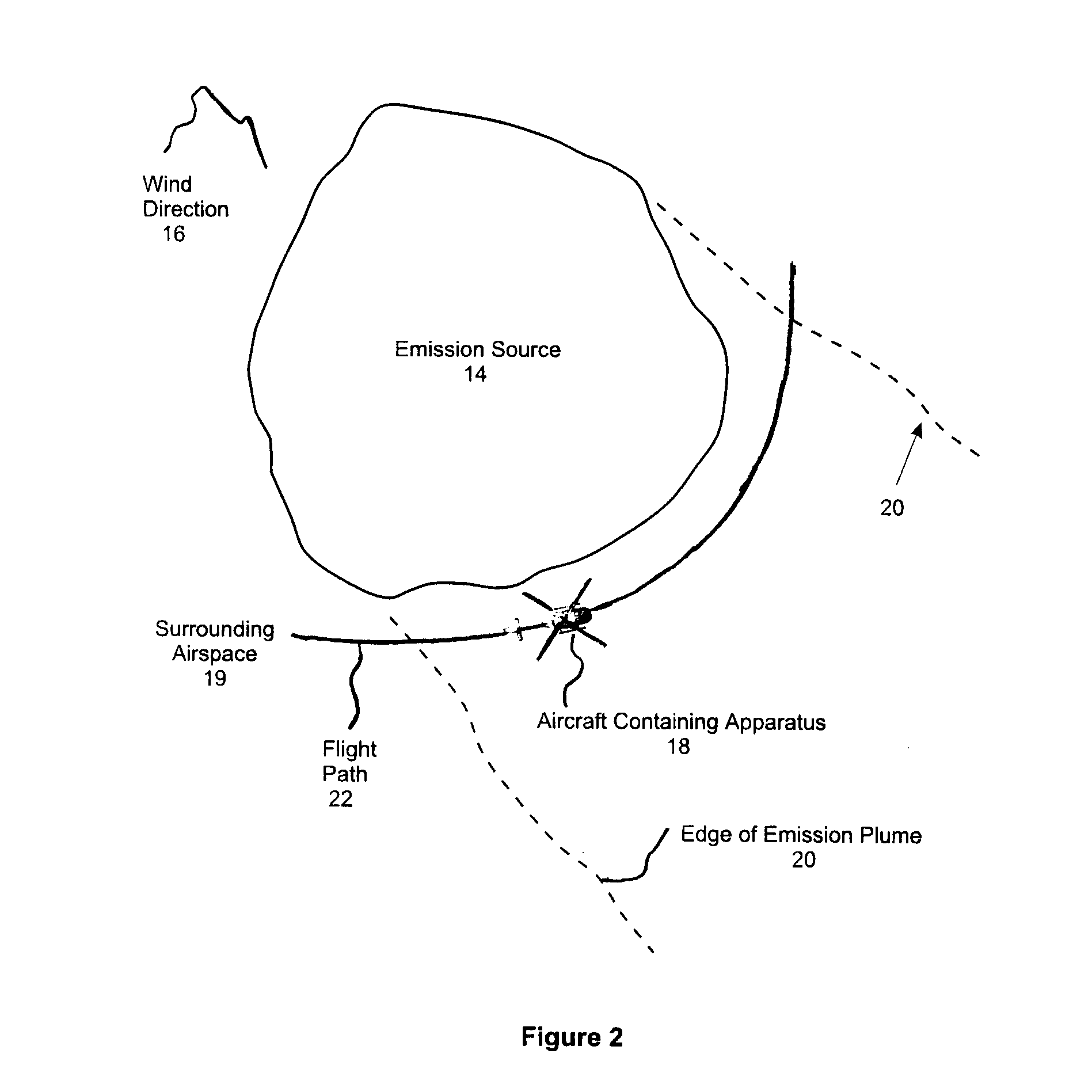

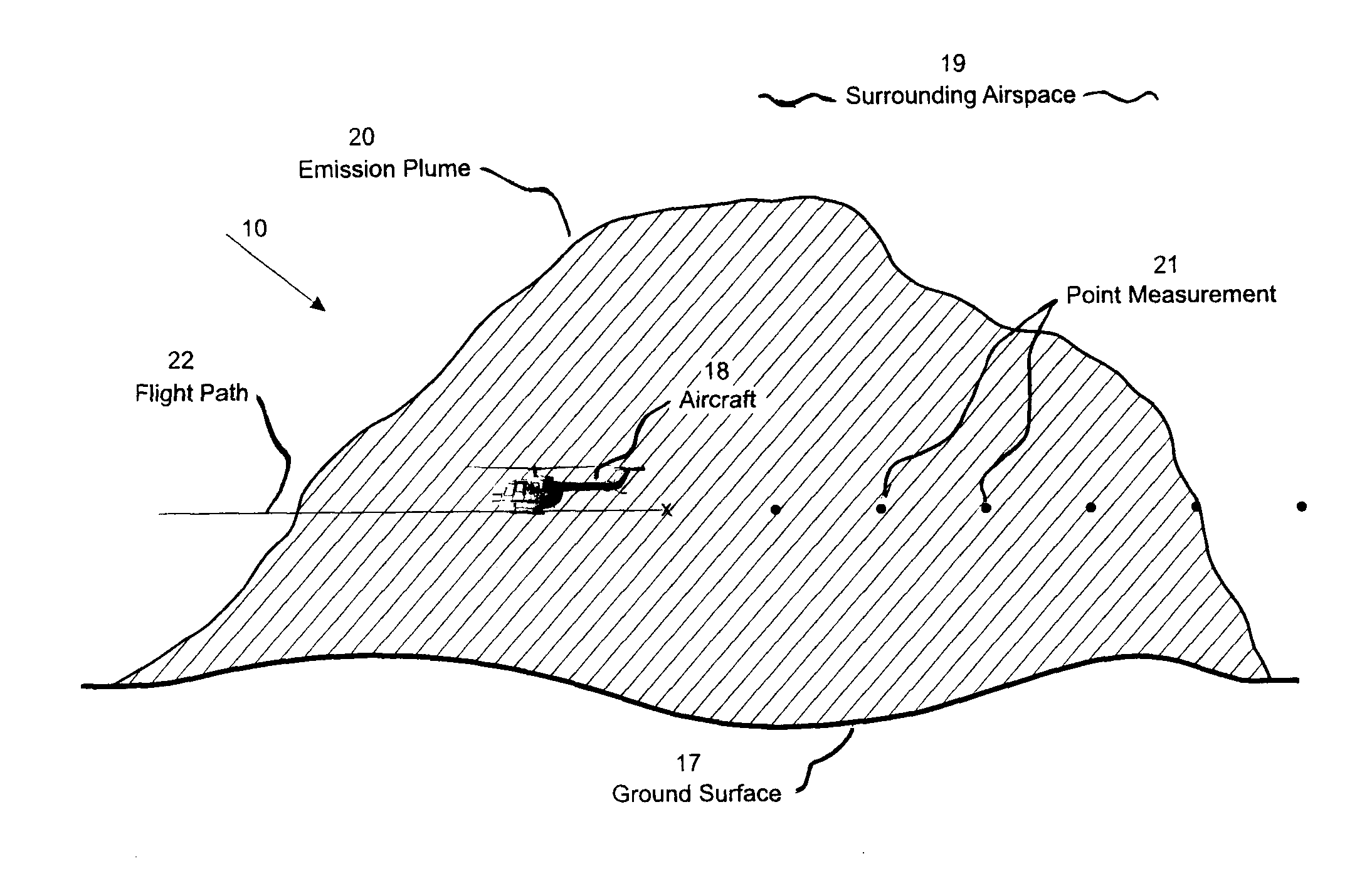

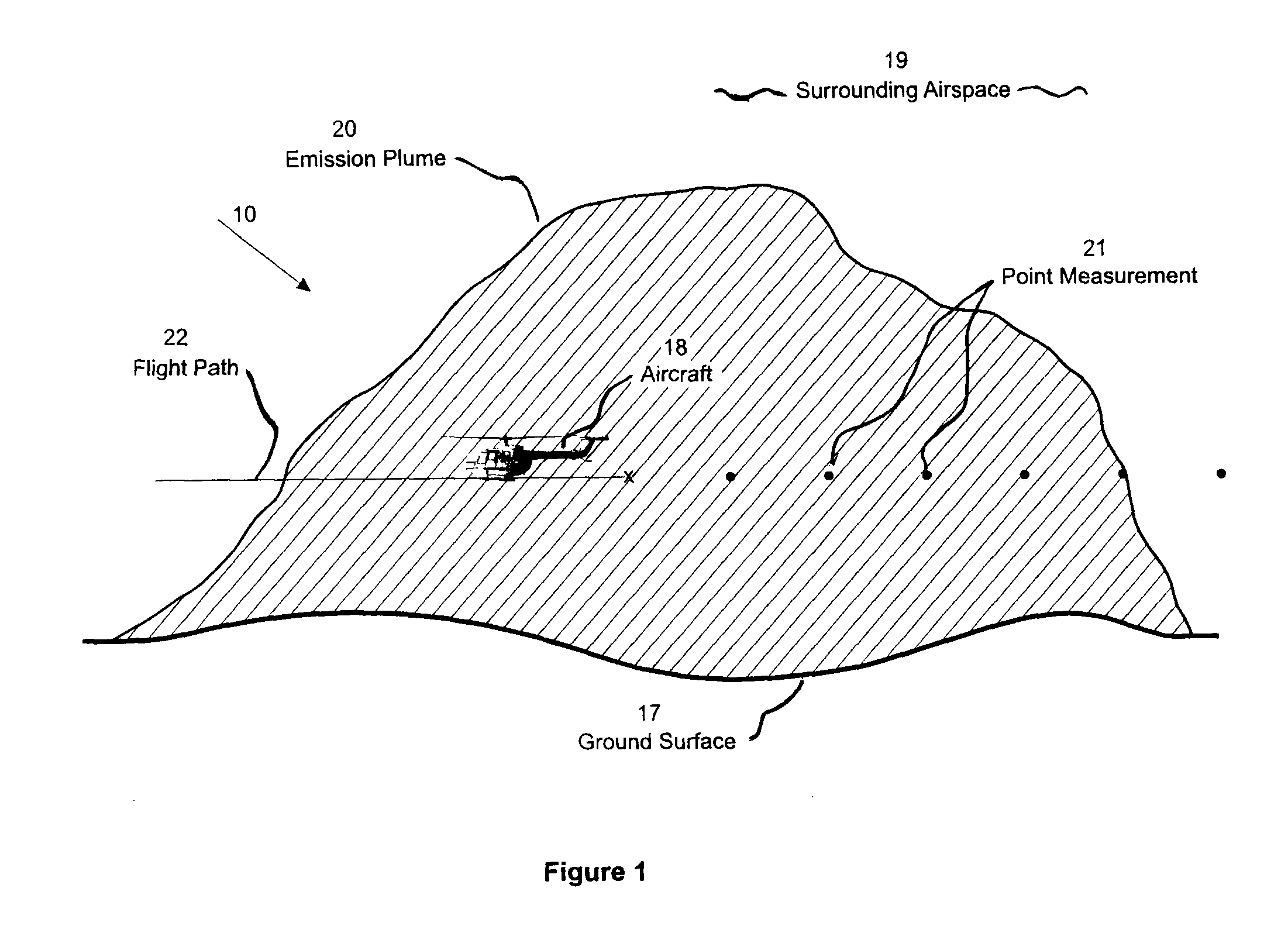

Mapping concentrations of airborne matter

ActiveUS20120092649A1Quick mapEasy to collectRadiation pyrometryMaterial analysis by optical meansGeographic siteOptical sensing

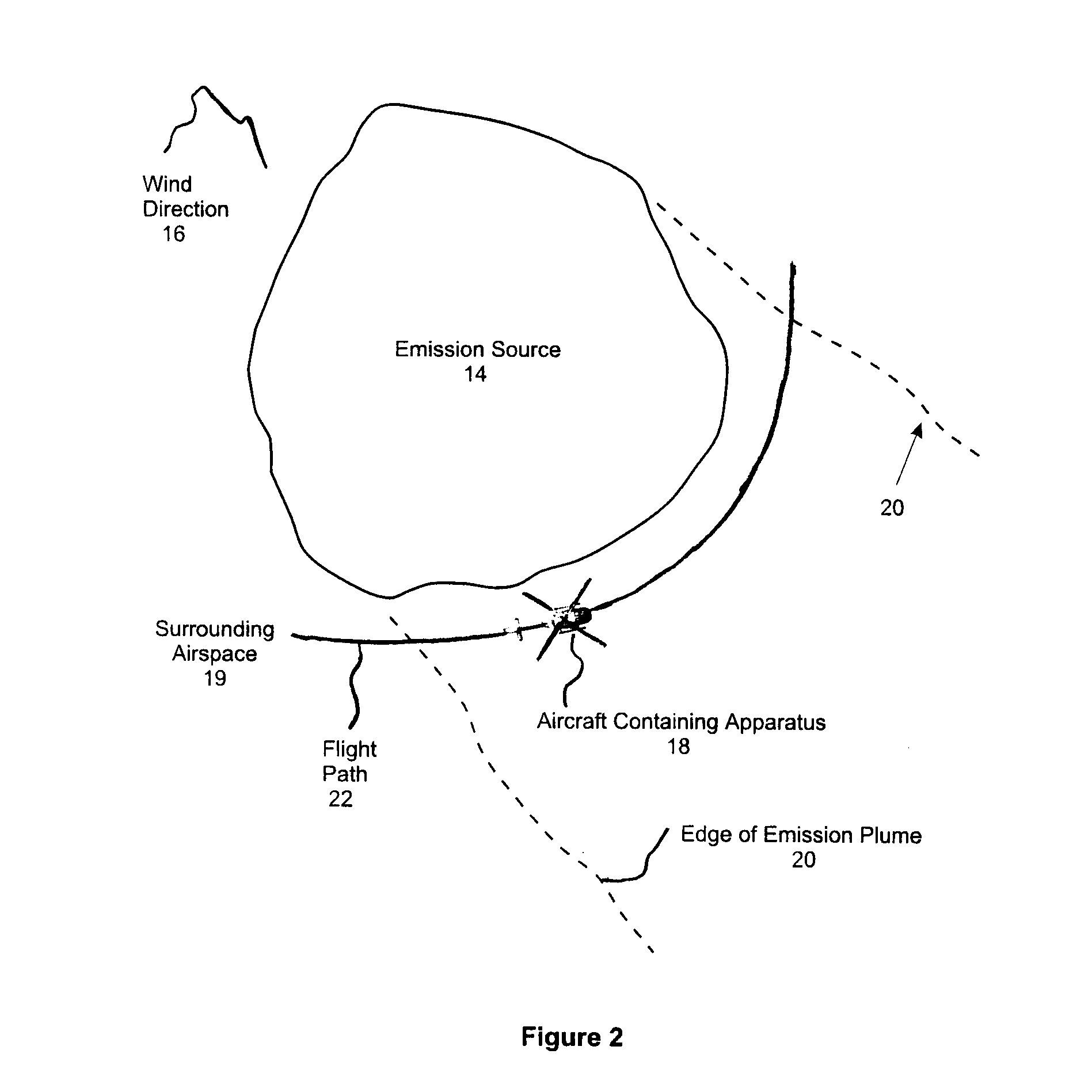

A method of mapping concentrations of airborne matter from an emission source of interest in an emission plume is provided. The method involves measuring airborne matter at one or more than one identified locations using an optical sensing instrument (OSI) operatively connected with one or more than one matter samplers and mounted on a vehicle. The one or more than one airborne matter samplers are passed through an airspace to be sampled, and one or more concentration measurements are obtained. Geographic positions and altitude values for each of the one or more identified locations are established, and a point concentration measurement for the airborne matter for each identified location determined. The concentration measurements are mapped relative to the geographic position and altitude values for each of the one or more identified locations to obtain an airborne matter concentration distribution map in one or more measurement surfaces through a cross-section or profile of the emission plume. The method further comprises a step of determining a representative wind velocity distribution at one or more measurement surfaces and calculating the mass flow rate of airborne matter across the measurement surface in mass per unit time.

Owner:GOLDER ASSOCIATES

Mapping concentrations of airborne matter

ActiveUS8294899B2Quick mapRadiation pyrometryMaterial analysis by optical meansGeographic siteOptical sensing

A method of mapping concentrations of airborne matter from an emission source of interest in an emission plume is provided. The method involves measuring airborne matter at one or more than one identified locations using an optical sensing instrument (OSI) operatively connected with one or more than one matter samplers and mounted on a vehicle. The one or more than one airborne matter samplers are passed through an airspace to be sampled, and one or more concentration measurements are obtained. Geographic positions and altitude values for each of the one or more identified locations are established, and a point concentration measurement for the airborne matter for each identified location determined. The concentration measurements are mapped relative to the geographic position and altitude values for each of the one or more identified locations to obtain an airborne matter concentration distribution map in one or more measurement surfaces through a cross-section or profile of the emission plume. The method further comprises a step of determining a representative wind velocity distribution at one or more measurement surfaces and calculating the mass flow rate of airborne matter across the measurement surface in mass per unit time.

Owner:GOLDER ASSOCIATES

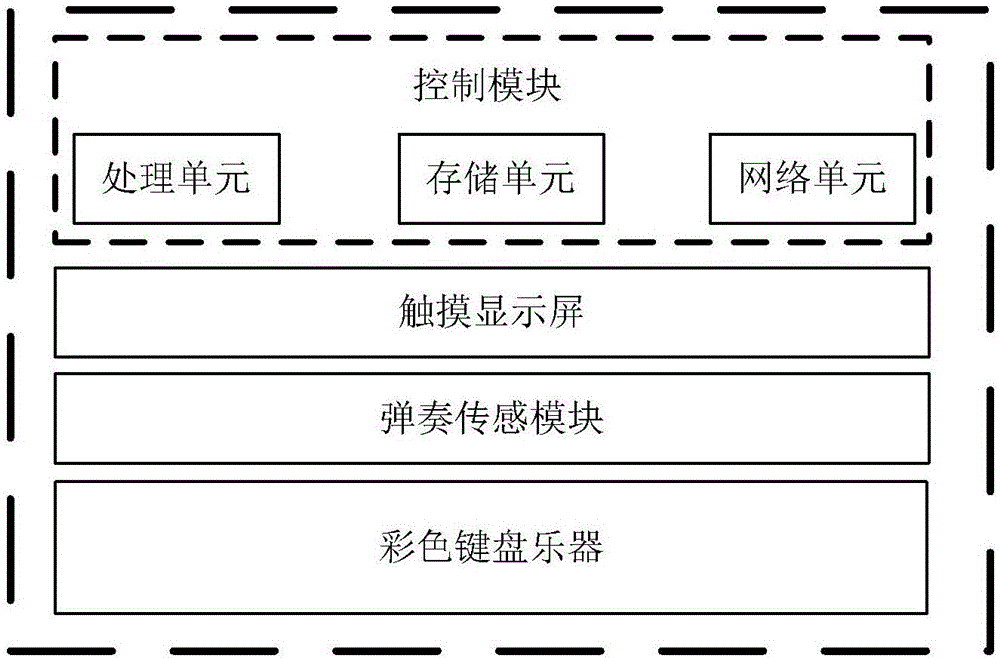

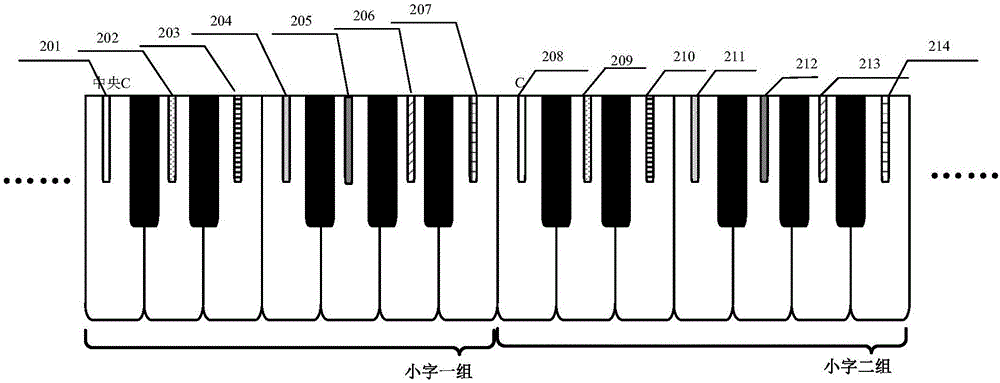

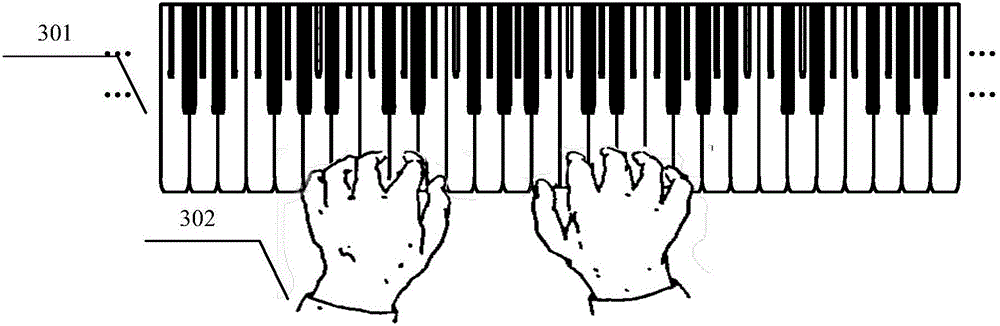

Interactive dynamic colorful form and meaning music score explaining method and musical instrument playing teaching and practicing device

The invention discloses an interactive dynamic colorful form and meaning music score explaining method and a musical instrument playing teaching and practicing device. The device comprises a colorful line keyboard musical instrument, a playing sensing module, a control module and a touch display screen. A dynamic form and meaning music score and a real person finger technique teaching and practicing music score are manufactured in advance according to the music score, keyboard distribution of a keyboard musical instrument and the real person teaching and practicing playing condition; the music score (such as a numbered musical notation and a stave) is visually and completely analyzed through the dynamic form and meaning music score, colorful vertical score lines corresponding to keys of a colorful line keyboard one to one represent the pitch, and aureole dynamic water leakage balls represent the pitch, sound value and sound volume of notes; the playing key positions and real-time prompts of the playing finger technique are shown in the real person finger technique teaching and practicing music score. When playing practicing is conducted, the music score is converted into the dynamic form and meaning music score, the real person finger technique teaching and practicing music score is downloaded through the parallel Internet, real-time broadcasting is conducted, a player is helped to quickly read the music score, the keys and the playing gestures are mapped, beginners and amateurs can be helped to quickly learn the rudiments of playing and conduct playing, and then the learning interestingness is promoted.

Owner:GUANGZHOU FENGPU INFORMATION TECH CO LTD

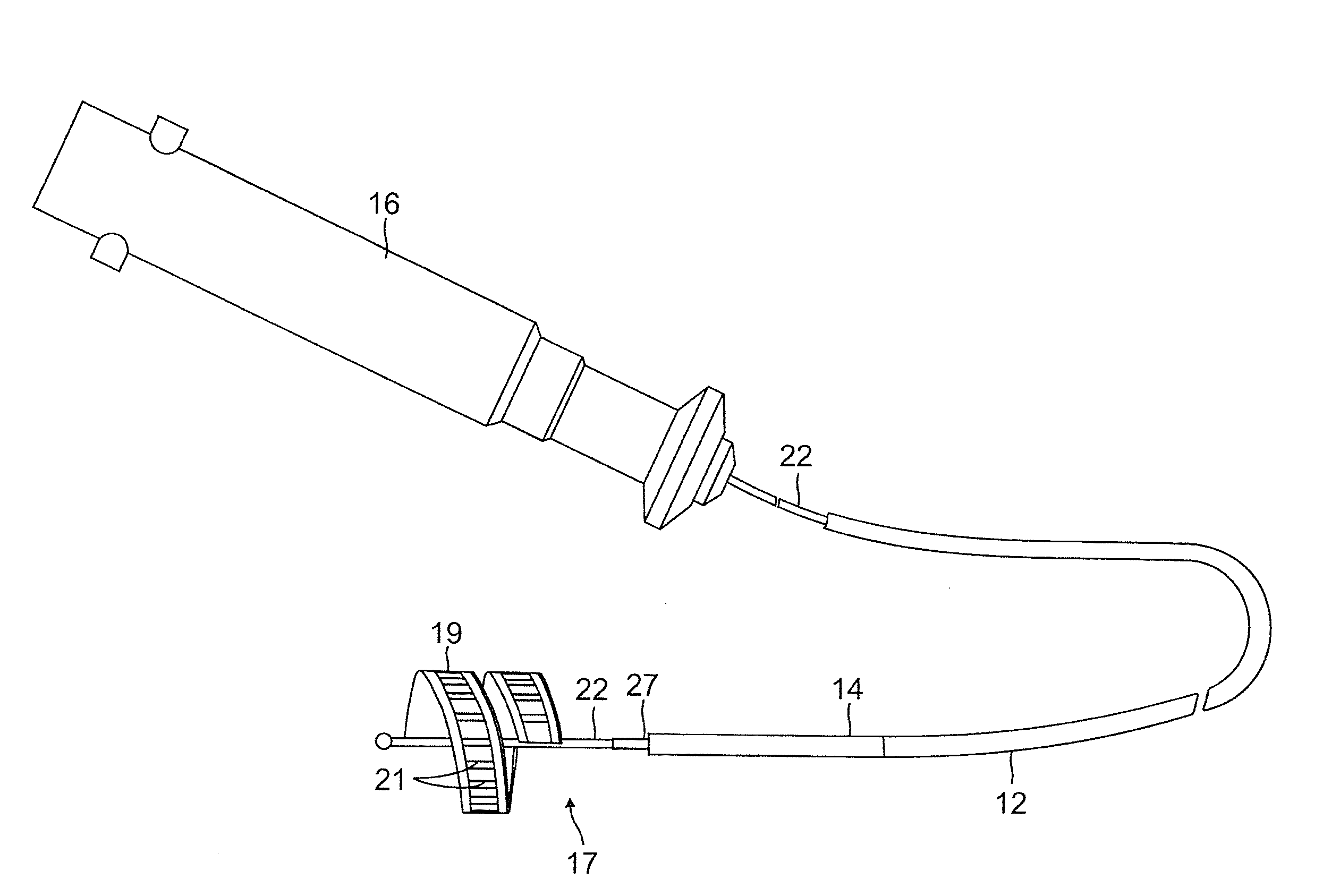

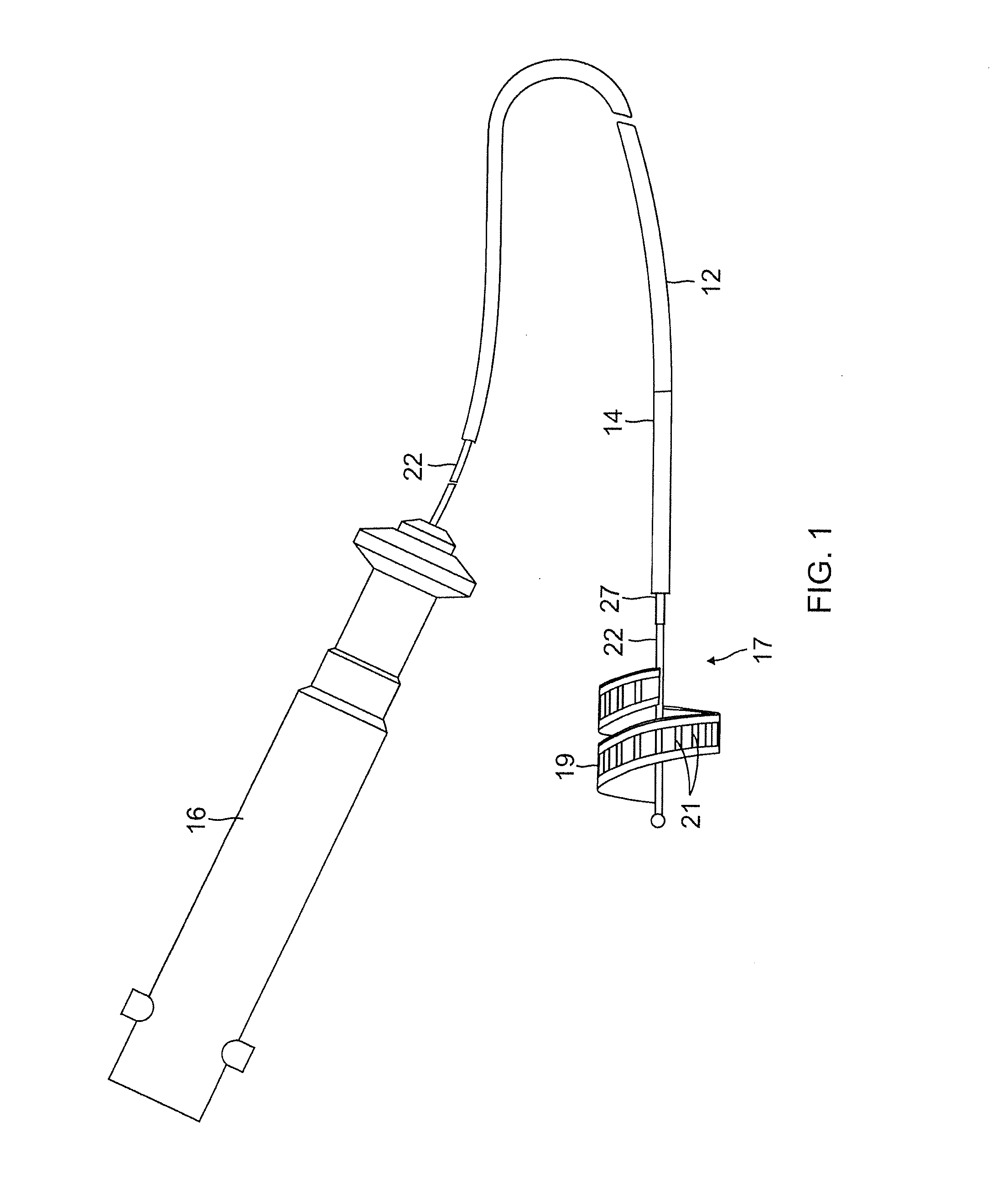

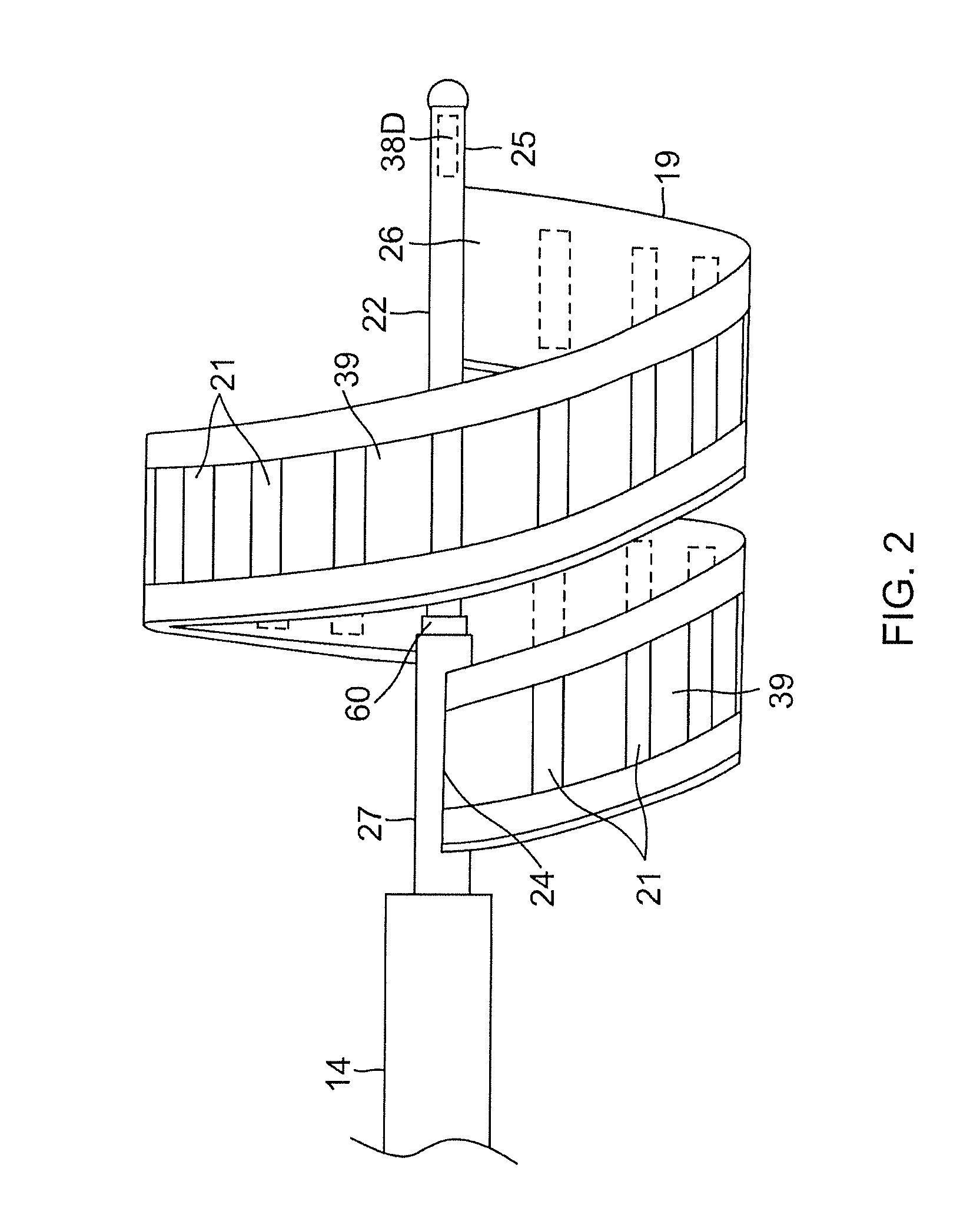

Mapping catheter with spiral electrode assembly

InactiveUS20130085360A1Quick mapIncrease the number ofElectrocardiographySensorsHeart chamberHeart wall

A mapping catheter adapted for use in a heart chamber, has a distal mapping assembly with a spiral ribbon that is radially expandable and contractable by means of an expander so that electrodes on the ribbon can contact heart wall at a plurality of locations simultaneously. The expander extends the length of the catheter between a control handle and a distal end of the spiral ribbon. The expander can be controlled directly at its proximal end by a user or the expander can be responsive to a puller wire controlled by a user interface on the control handle.

Owner:BIOSENSE WEBSTER (ISRAEL) LTD

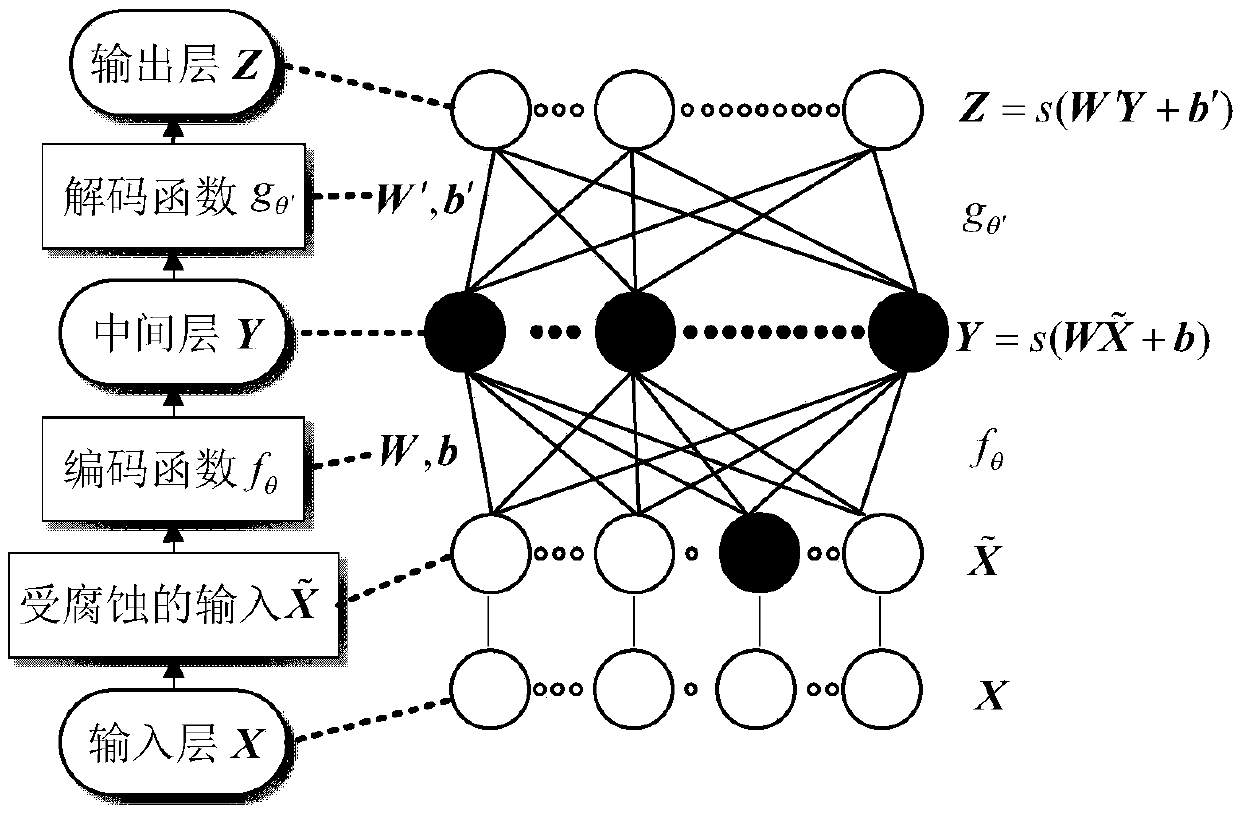

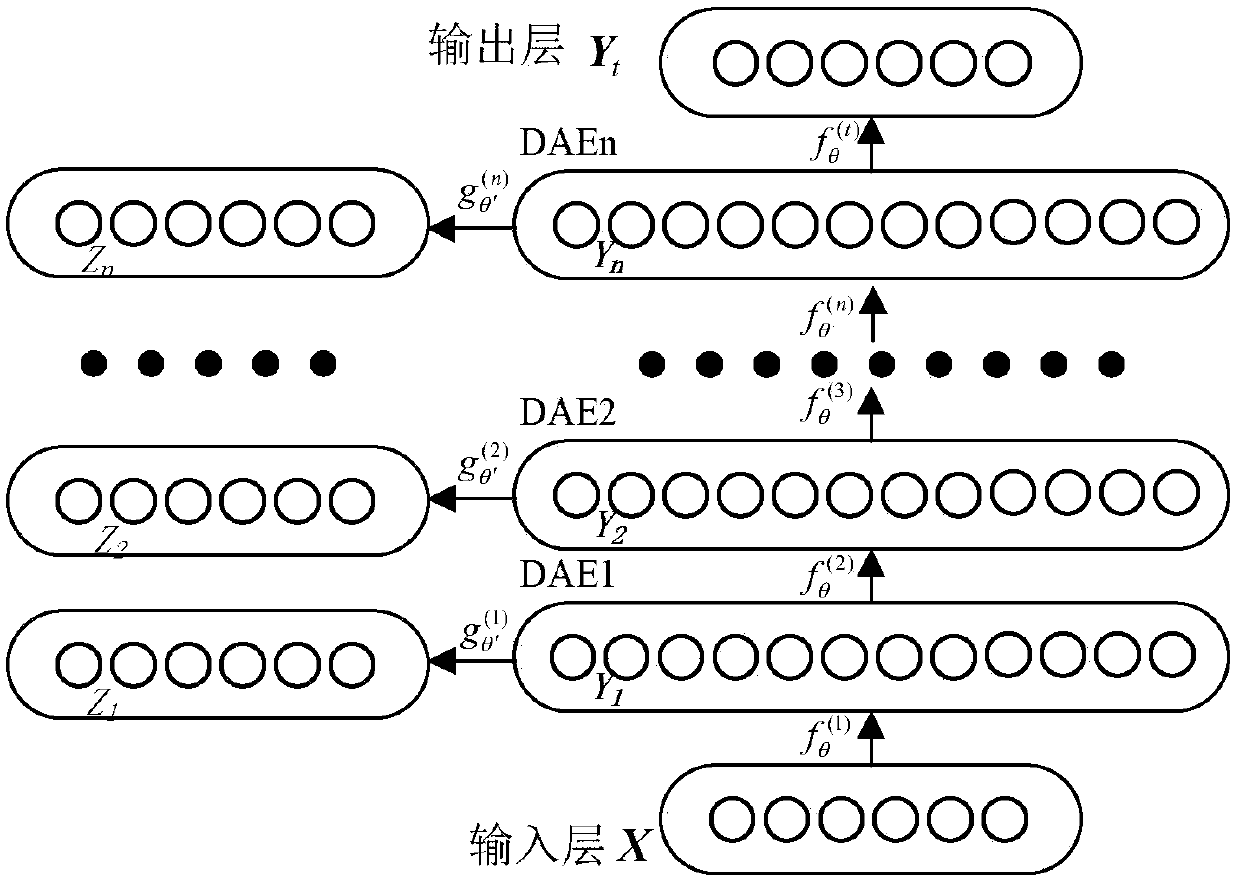

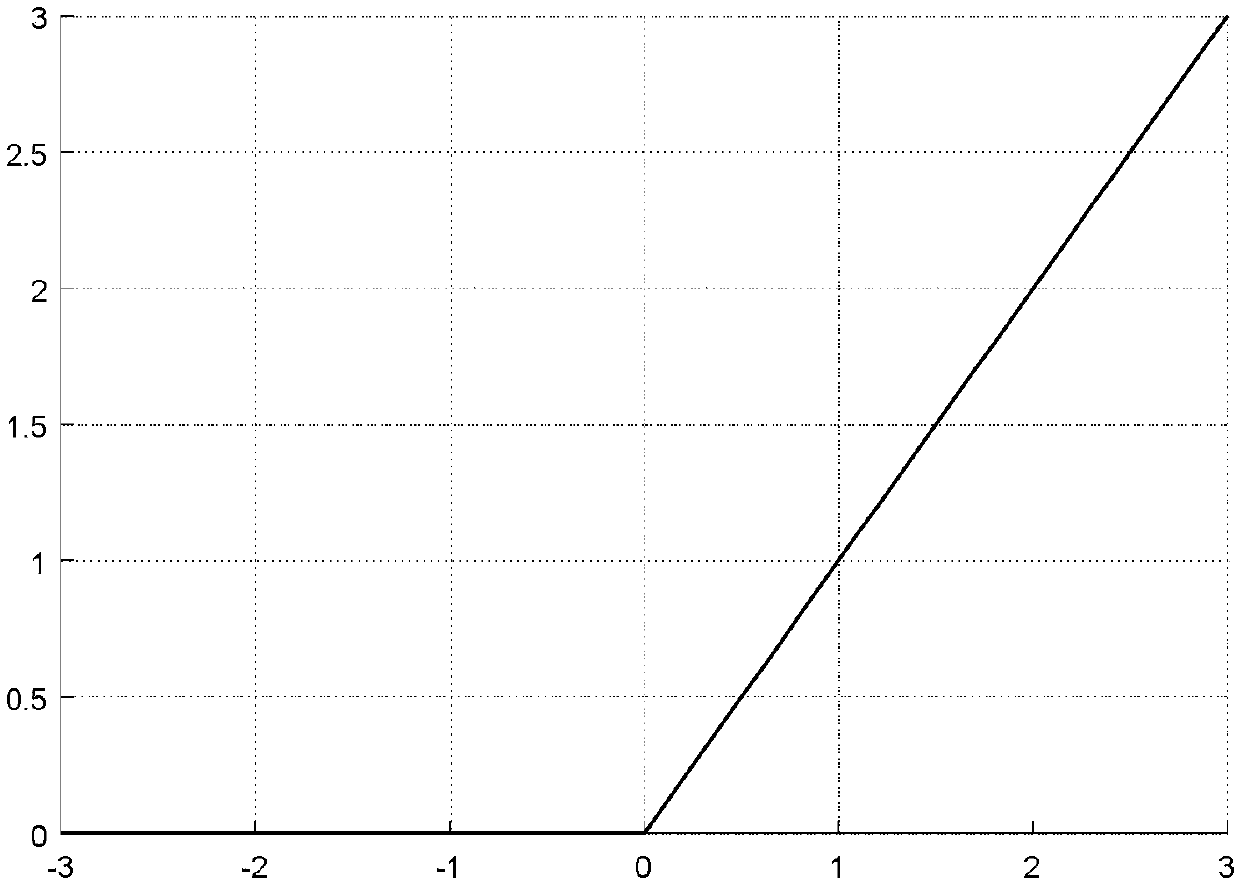

Integrated electrical and natural-gas energy system probability energy flow calculation method based on stacked denoising autoencoder

ActiveCN108734391AQuick mapHigh solution accuracyResourcesNeural architecturesComputer scienceStandardization

The invention discloses an integrated electrical and natural-gas energy system probability energy flow calculation method based on a stacked denoising autoencoder. The method comprises the following steps that: firstly, by virtue of the deep stack structure and the coding and decoding process of an SDAE (Stacked Denoising Autoencoder), establishing an energy flow model based on the SDAE to effectively mine the high-order characteristics of a nonlinear energy flow equation; on the basis, combining with numerical value characteristics input and output by the energy flow to put forward a trainingmethod based on a ReLU activation function, deviation standardization normalization and a small-batch gradient descent method to improve training accuracy and speed; and then, combining with an MCS (Modulation and Coding Scheme) method to sample a sample to be solved, and using a trained SDAE energy flow model to directly map the energy flow values of all sampled samples so as to realize the high-accuracy online calculation of the probability energy flow on a premise that hardware cost is not increased.

Owner:CHONGQING UNIV

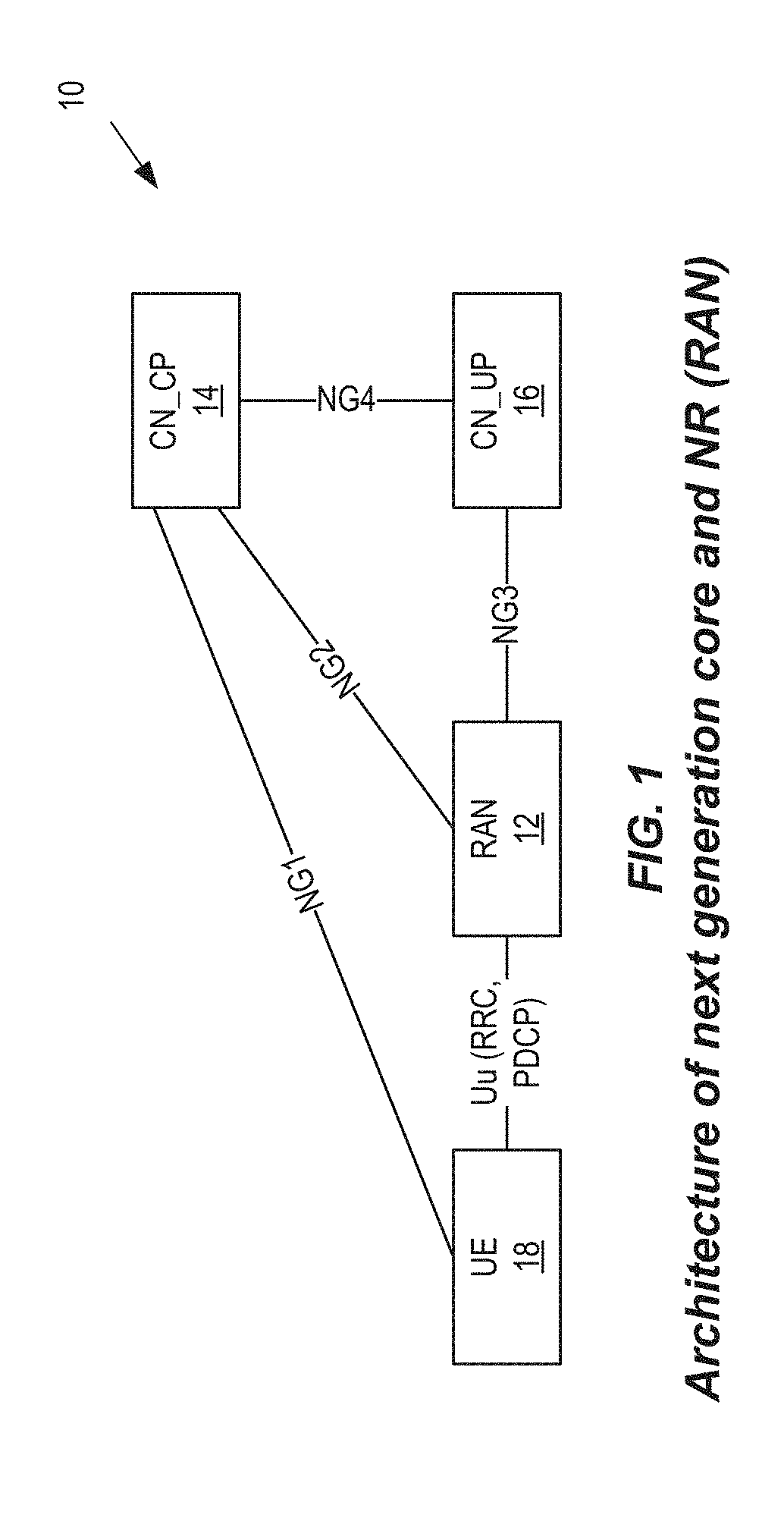

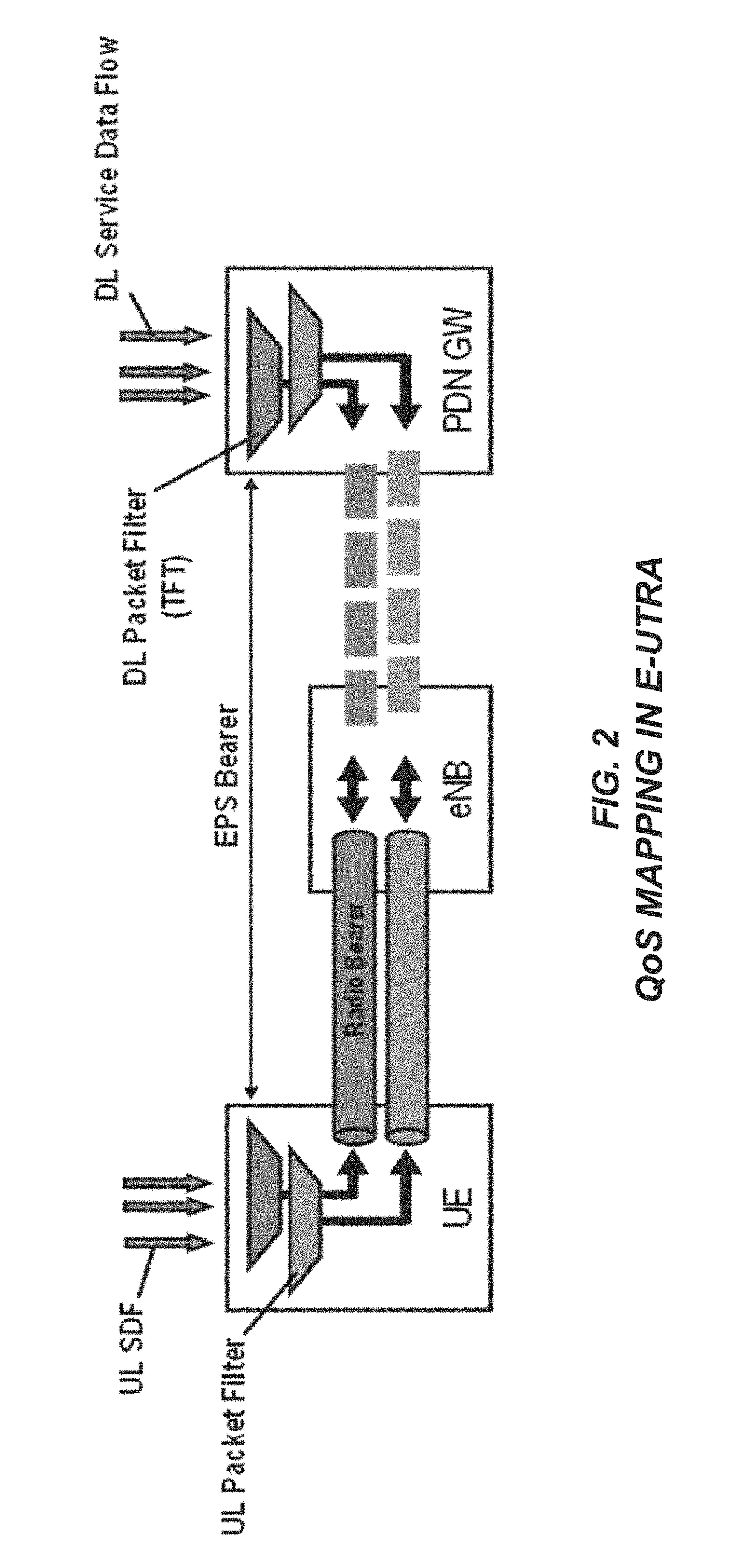

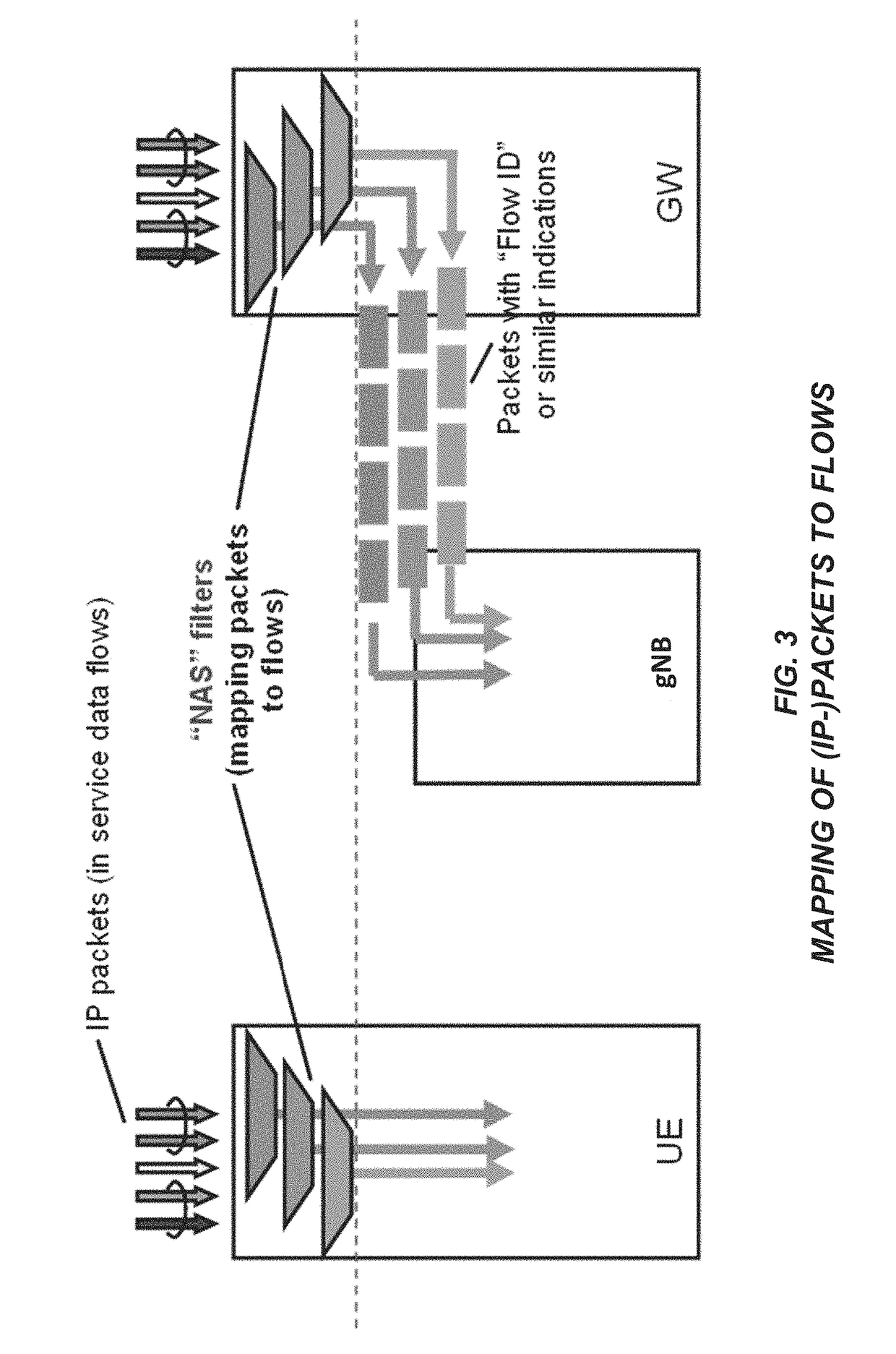

Reflective mapping of flows to radio bearers

InactiveUS20190075482A1Reduce control signalingQuick mapNetwork traffic/resource managementConnection managementTraffic capacityTelecommunications

Systems and methods for reflective mapping of flows to radio bearers are provided. In some embodiments, a method of operation of a radio access node includes determining a flow-to-radio bearer mapping by determining a radio bearer to which to map a flow. The method also includes mapping the flow to the radio bearer according to the flow-to-radio bearer mapping, where the radio bearer is different than a previous radio bearer to which the flow was mapped and transmitting a downlink transmission for the flow on the radio bearer according to the flow-to-radio bearer mapping. The downlink transmission includes a flow identifier of the flow. In this way, a flow may be quickly mapped to another radio bearer for a wireless device. This may be for when the transmission of a flow starts or changes in characteristics. Also, control signaling is reduced between the radio access node and the wireless device.

Owner:TELEFON AB LM ERICSSON (PUBL)

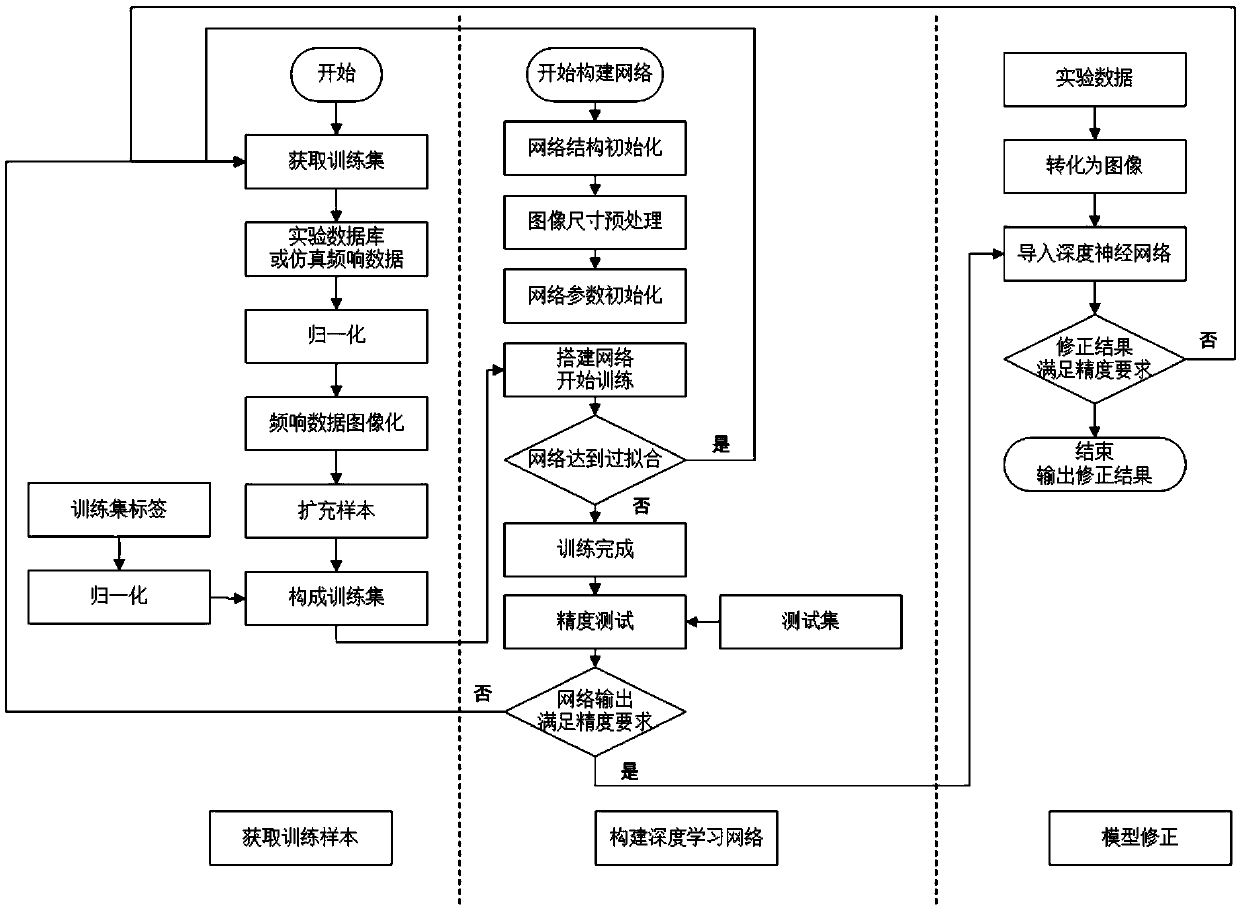

A structure frequency response dynamic model correction method based on deep learning

ActiveCN108959794ATake advantage ofStrong representation abilityDesign optimisation/simulationSpecial data processing applicationsNerve networkDynamic models

The invention discloses a structure frequency response dynamic model correction method based on deep learning. The method includes transforming the frequency response value of the experimental measured structure and the frequency response value of the dynamic model simulation into an image mode for storing and feature extraction, taking the corresponding parameters of the training sample images aslabels of the training set, and establishing the training sample sets of multi-frequency points, multi-observation points and multi-observation directions, and based on this, building a deep neural network and other processes. The method combines the advantages of deep learning in the field of image recognition, establishes the fast mapping relationship between the dynamic output and the parameters to be corrected, inputs the experimental measurement image into the trained neural network, outputs the model correction result, and effectively solves the problems of poor model representation ability of the manual feature extraction method and the like. In addition, considering the possibility of over-fitting caused by less training samples, the method of adding fast connection structure in the network forward transmission and adding noise expansion samples are adopted to reduce the parameter correction error.

Owner:BEIHANG UNIV

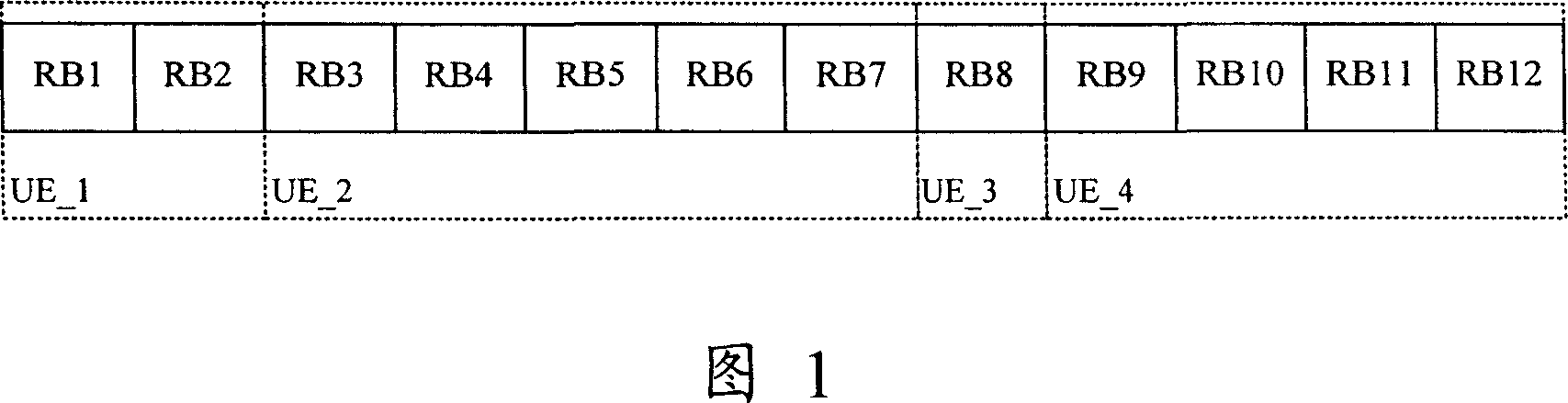

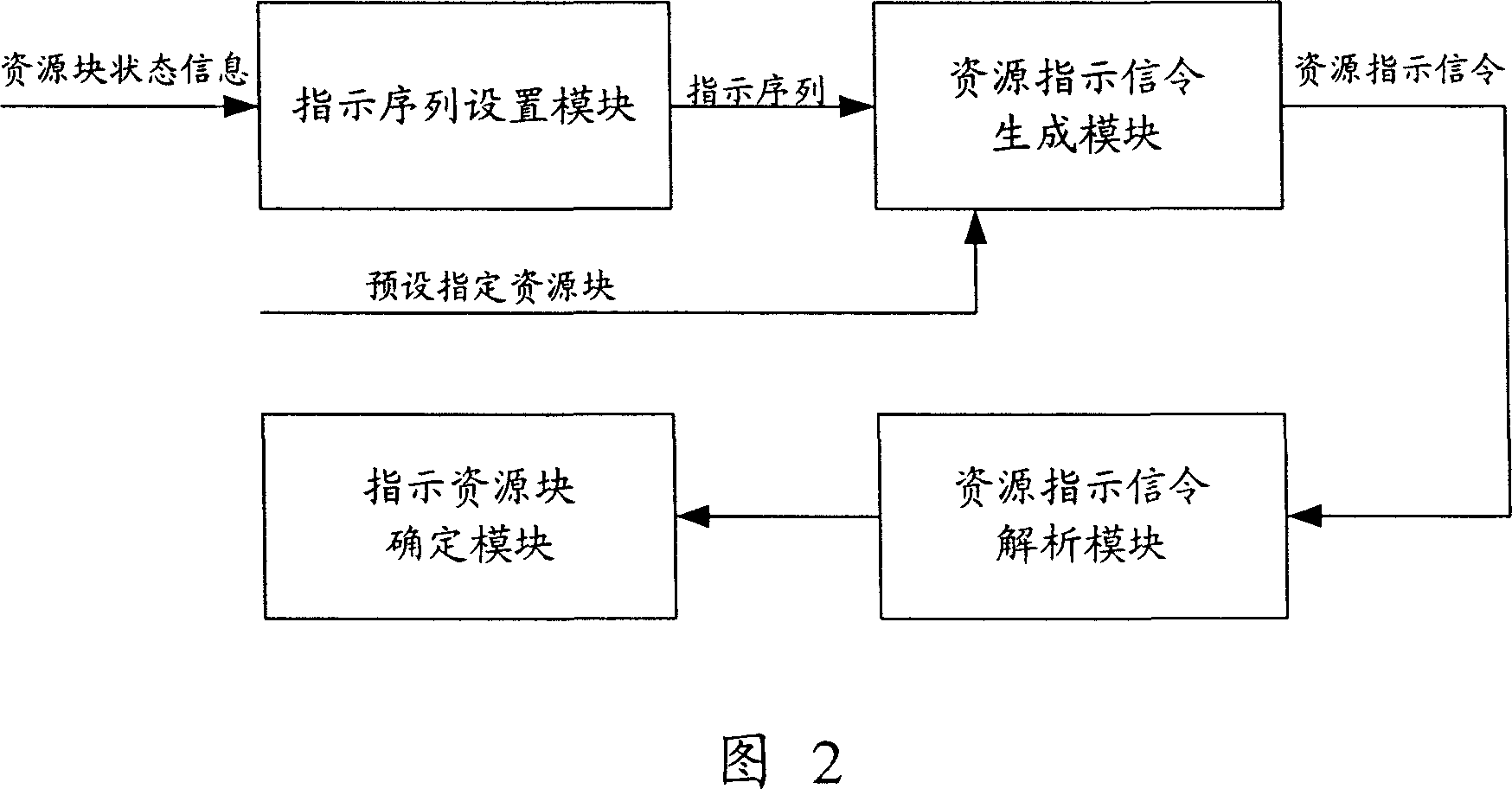

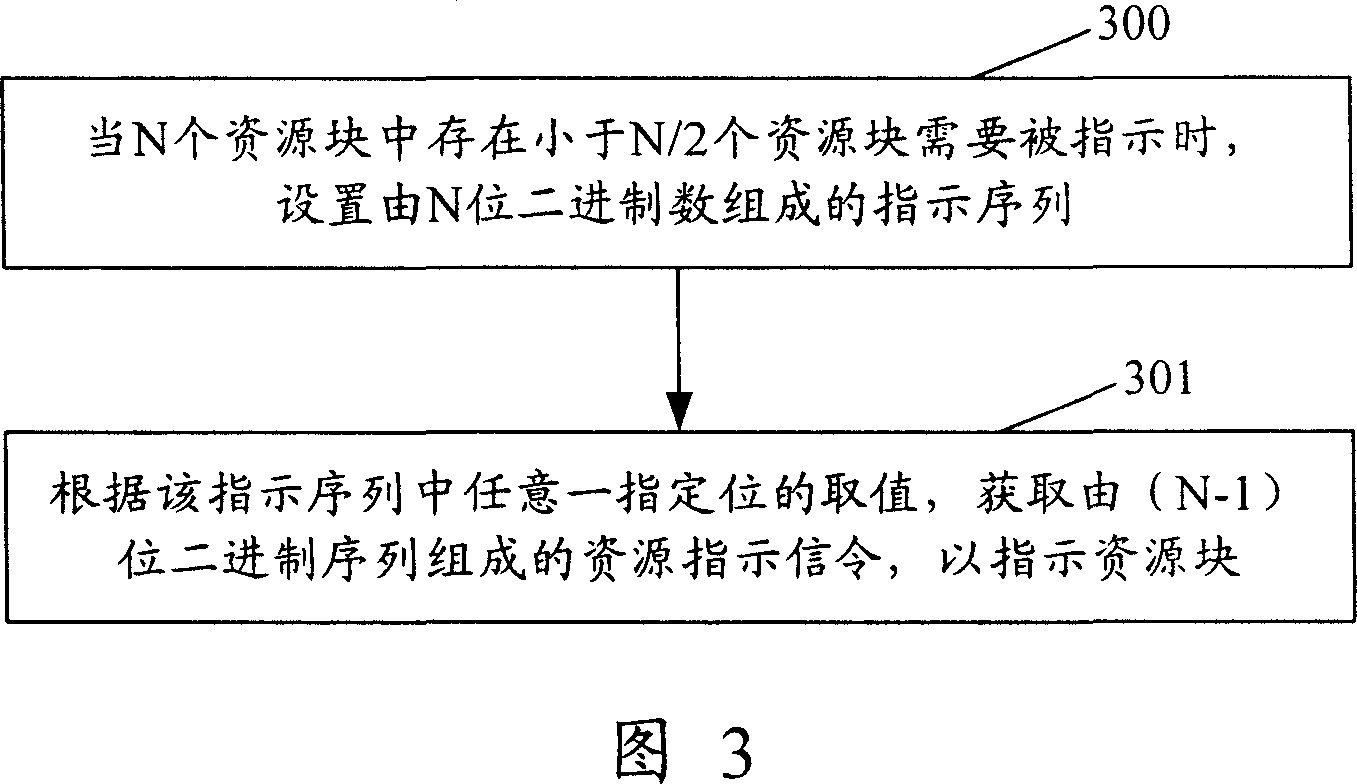

Method for indicating telecommunication system resources and system, transmitter and receiver

InactiveCN101076139AQuick mapReduce signaling volumeNetwork traffic/resource managementRadio/inductive link selection arrangementsCommunications systemResource block

In the invention, when less than N / 2 resource blocks in N resource blocks needs to be indicated, the method comprises: a) setting an indication sequence composed of N bit binary numbers; b) according to the value of any appointed bit in the indication sequence, getting a resource indication signaling composed of N-1 bit binary sequence to indicate the resource block. The invention also reveals a communication system resource indication system, an apparatus for sending communication system resource indication and an apparatus for receiving the communication system resource indication. By the invention, the resource indication signaling can reduce one bit information comparing the resource indication signaling obtained from bitmap method.

Owner:HUAWEI TECH CO LTD

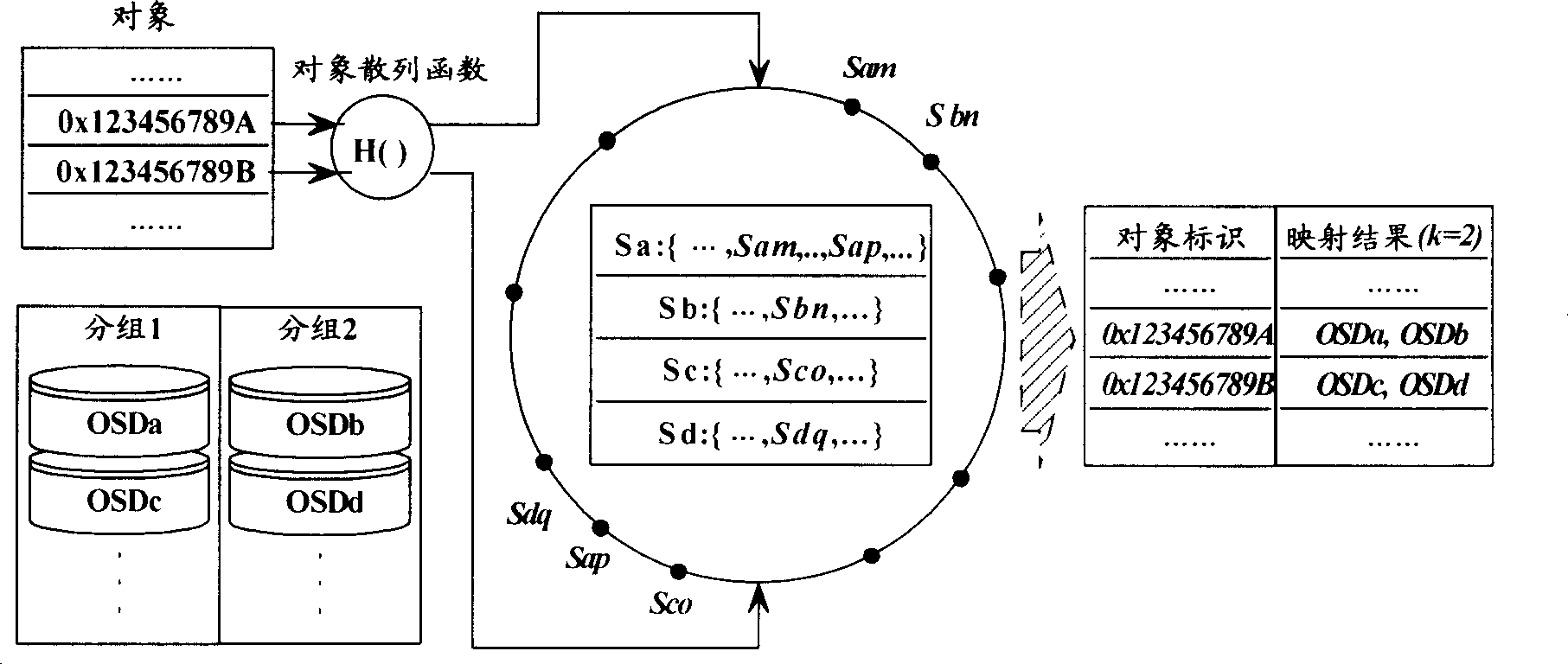

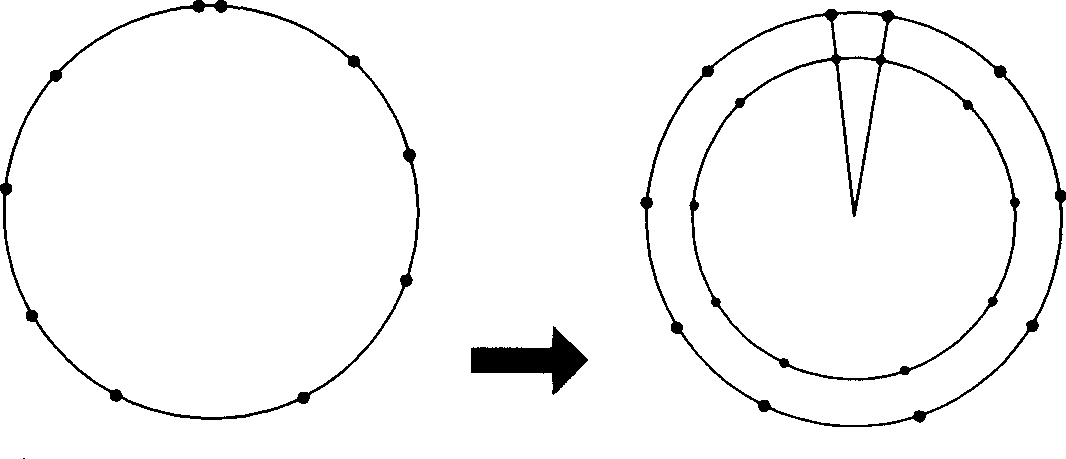

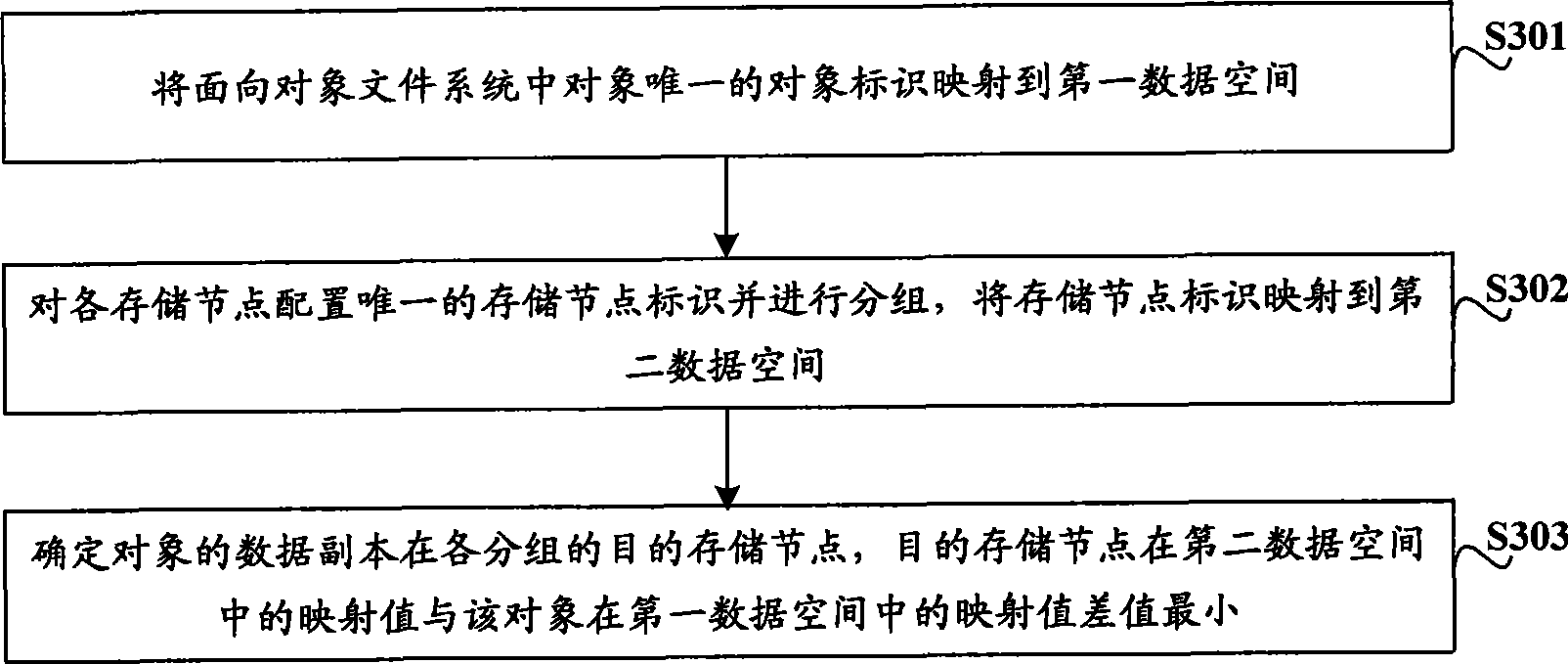

Data copy mapping method and device based on object-oriented file system

InactiveCN101419600AAddress reliabilitySimple methodSpecial data processing applicationsData spaceFile system

The invention discloses a data copy mapping method based on an object-oriented file system and a device thereof; the invention can support the data copy technology and achieve the purpose of fast mapping with a simple and effective method. The data copy mapping method based on the object-oriented file system which is provided by the embodiment of the invention comprises: the only object mark for the object of an object-oriented file system is mapped to a first data space; each storage node is configured with an only storage node mark and grouped and the storage node mark is mapped to a second data space; the destination storage node of the data copy of the object in each group is determined, and the difference value between the mapping value of the destination storage node in the data second space and the mapping value of the object in the first data space is a minimum. The data copy mapping device based on the object-oriented file system which is provided by the embodiment of the invention includes an object mapping module, a data copy mapping control module, and a storage node group mapping module.

Owner:深圳市亚贝电气技术有限公司

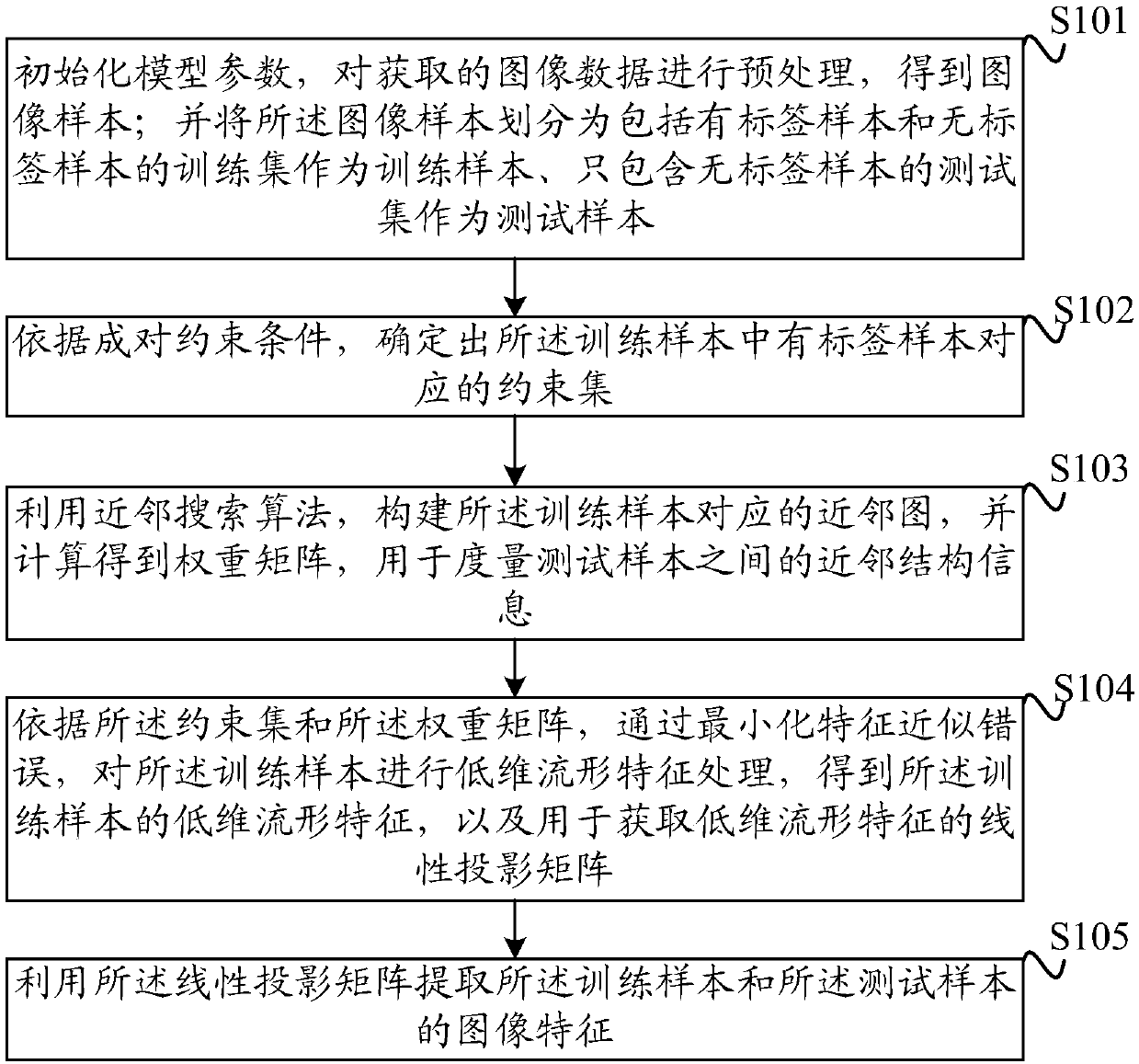

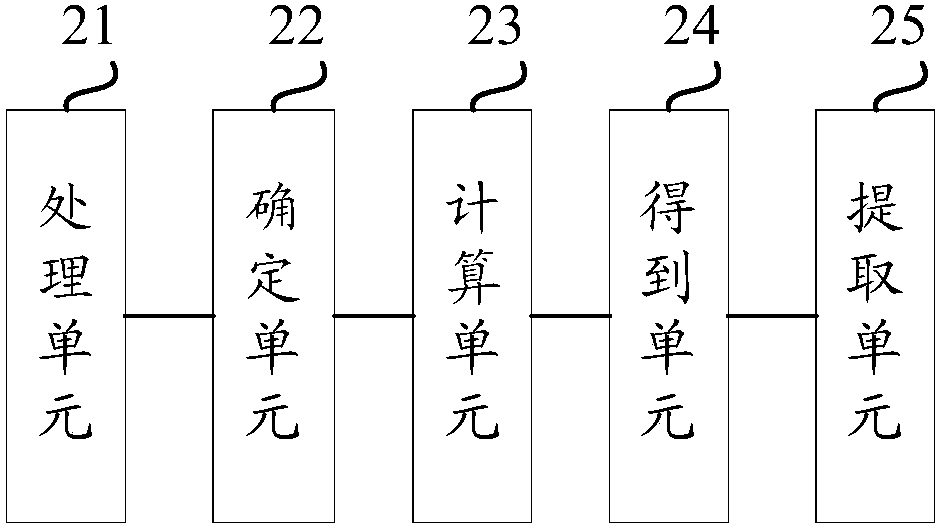

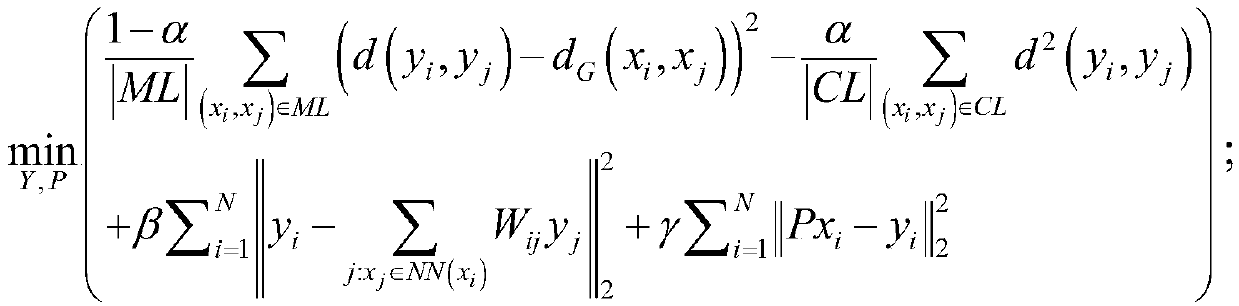

Method and device for extracting image features based on semi-supervised learning

InactiveCN107563445AQuick mapImprove recognizabilityCharacter and pattern recognitionHat matrixFeature extraction

The embodiment of the invention discloses a method and device for extracting image features based on semi-supervised learning. The method comprises steps of: initializing a model parameter and preprocessing image data to obtain image samples, and dividing the image samples into training samples including tagged samples and untagged samples, and test sample just including the untagged samples; according to a pairing constraint condition, determining a constraint set corresponding to the tagged samples in the training samples; by using a neighbor search algorithm, constructing neighbor graphs corresponding to all the training samples and calculating a weight matrix; by minimizing a feature approximate error, subjecting the training samples to low-dimensional manifold feature processing to obtain low-dimensional manifold features and a linear projection matrix; and extracting the image features of the training samples and the test samples by using the linear projection matrix. The methodand device can simultaneously maintain the global and local structure information of the sample data, improve the distinguishability of the features, quickly map new test data to low dimension and improve the performance of image feature extraction.

Owner:SUZHOU UNIV

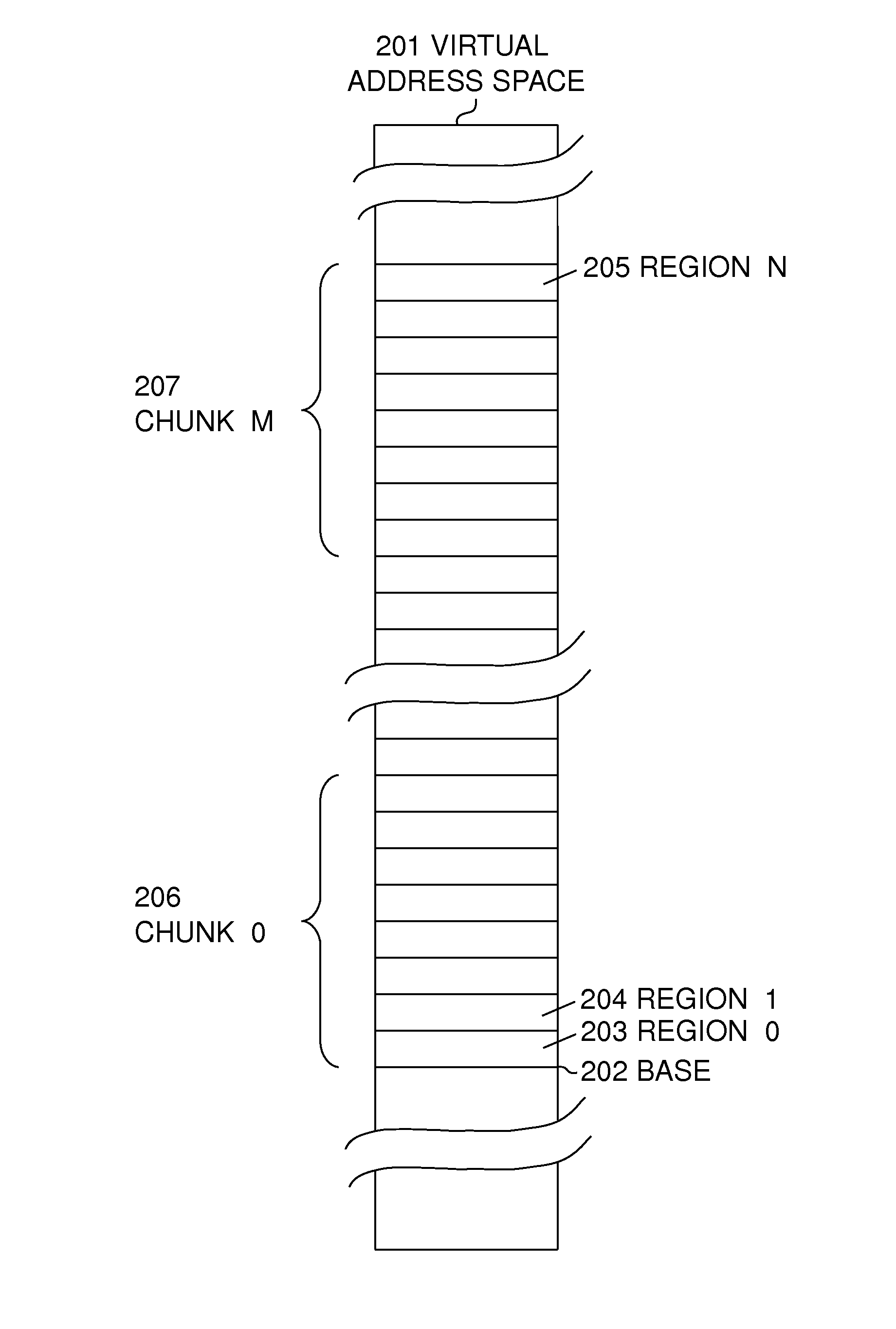

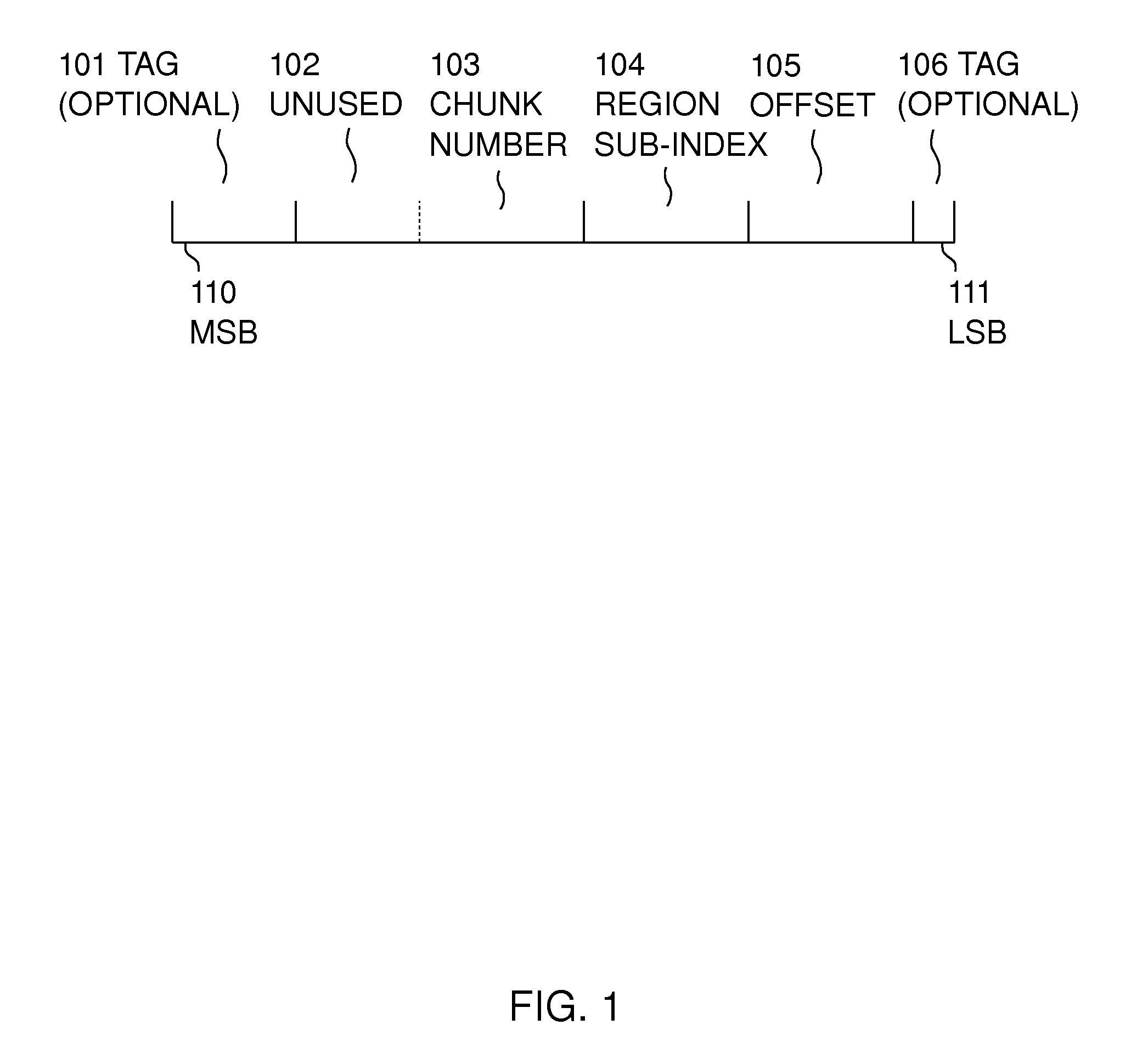

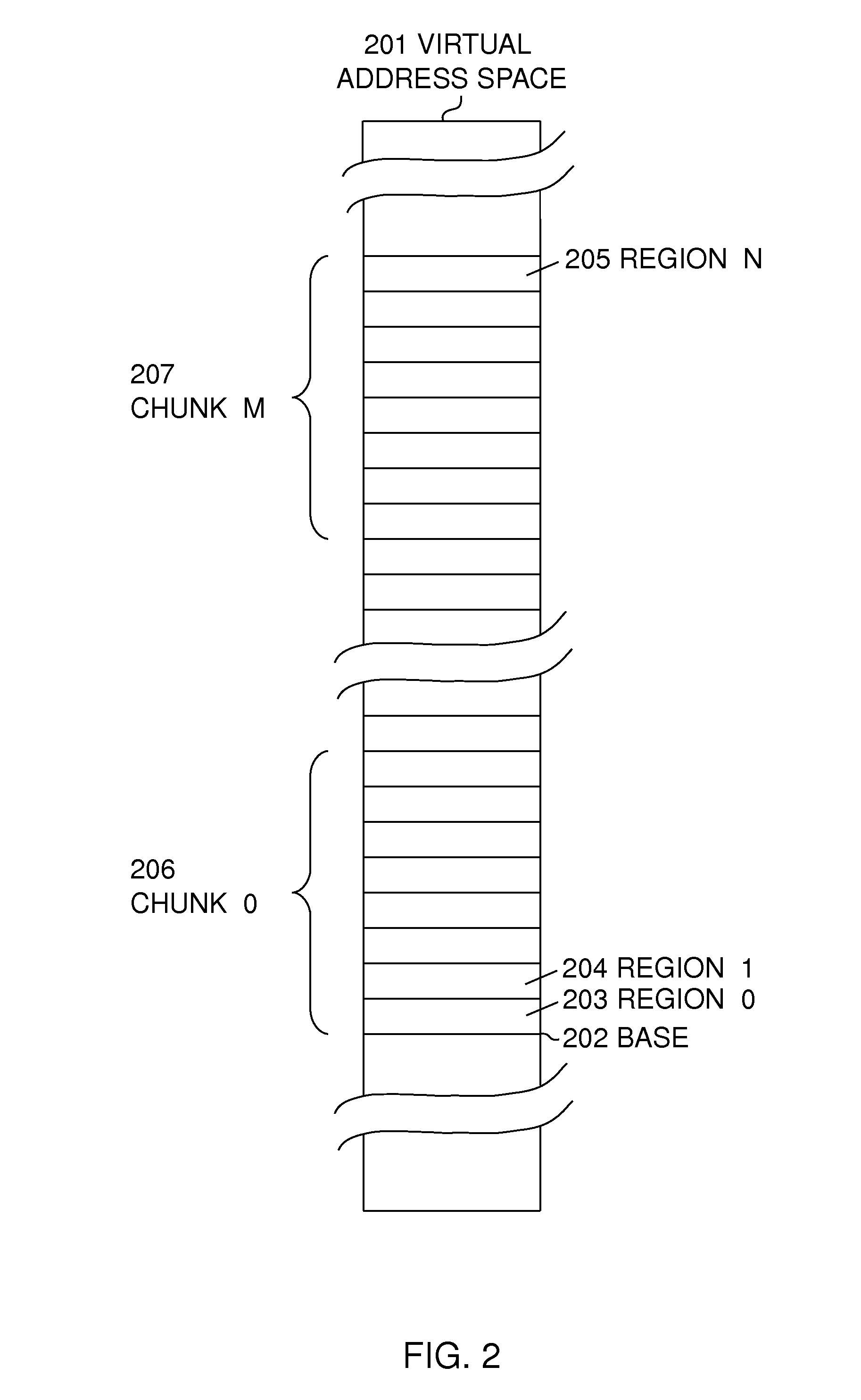

Addressing for Huge Direct-Mapped Object Systems

InactiveUS20110276776A1Convenient ArrangementQuick mapMemory architecture accessing/allocationMemory adressing/allocation/relocationData setLookup table

A method, computing system, and computer program product are provided for quickly and space-efficiently mapping an object's address to its home node in a computing system with a very large (possibly multi-petabyte) data set. The addresses of objects comprise three fields: a chunk number, a region sub-index within the chunk, and an offset within the region, with chunks being used to achieve good compromise between small lookup tables and reducing waste of usable virtual address space.

Owner:CLAUSAL COMPUTING

Reconfigurable arithmetic unit supporting multiple working modes and working modes thereof

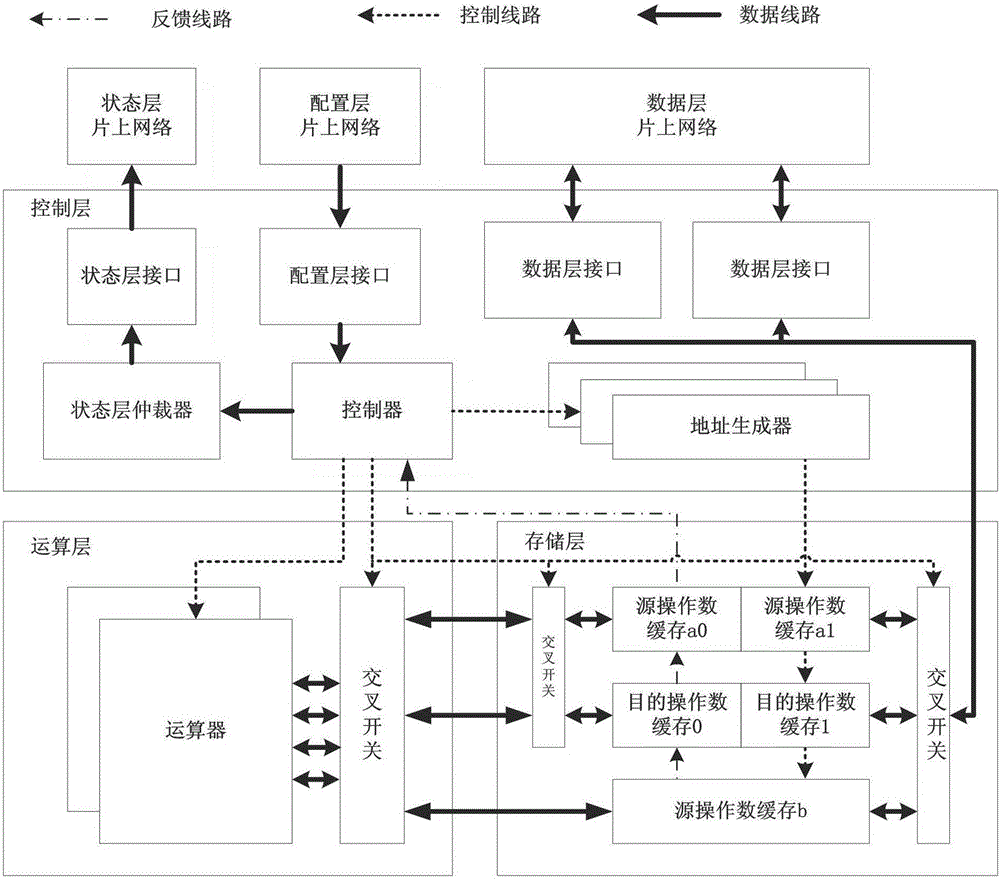

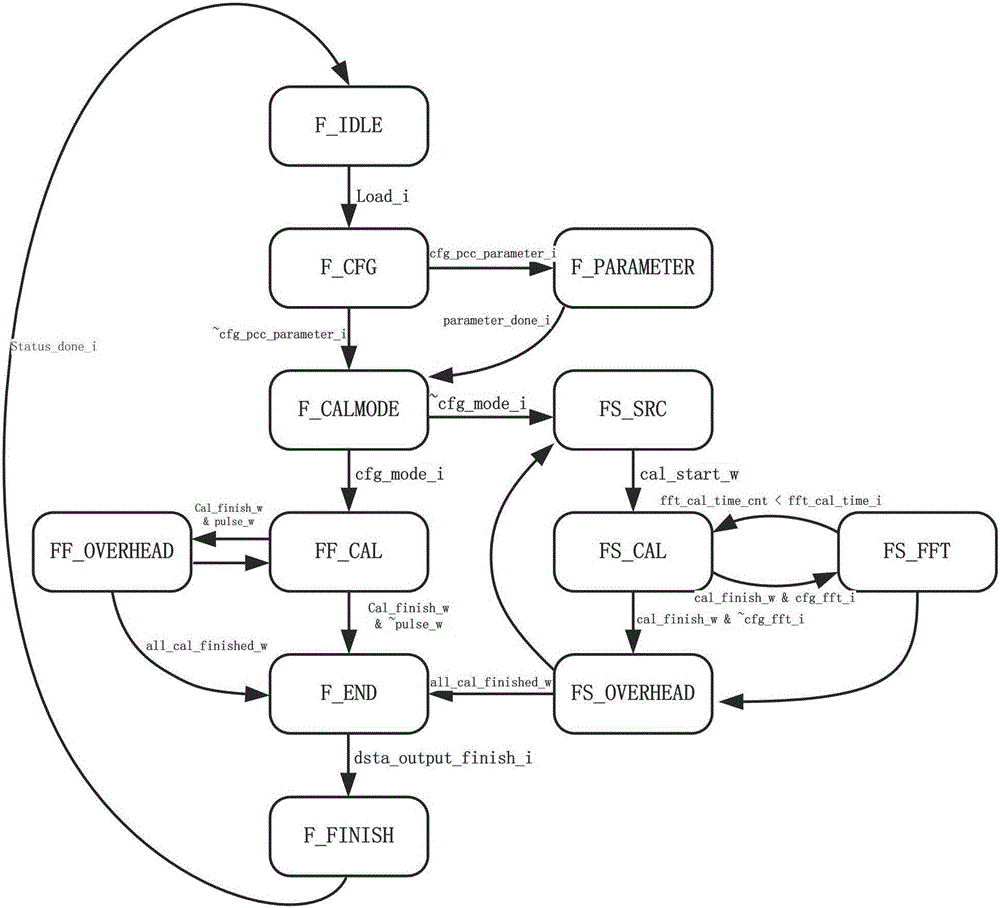

ActiveCN106155814AImprove work efficiencyEasy to integrateResource allocationDigital computer detailsControl layerLayer interface

The invention discloses a reconfigurable unit supporting multiple working modes and the working modes thereof. The reconfigurable unit is characterized by comprising a control layer, an arithmetic layer and a storage layer; the control layer comprises a state layer interface, a configuration layer interface, a data layer interface, an address generator and a controller; the arithmetic layer comprises an arithmetic device; the storage layer comprises a source operand cache unit and a destination operand cache unit. The working modes of the reconfigurable arithmetic unit comprise the storage arithmetic mode, the pulse arithmetic mode and the stream arithmetic mode, and higher flexibility is provided for algorithm mapping of a computing system. When task mapping is carried out in the computing system, the specific working modes of the reconfigurable arithmetic unit can be selected according to specific features and the bottleneck of the algorithm to be mapped and in combination with specific conditions of network communication and storage bandwidth in the computing system, therefore, the arithmetic throughput capacity and network communication and storage access pressure are considered, and the working efficiency of the whole system is improved.

Owner:HEFEI UNIV OF TECH

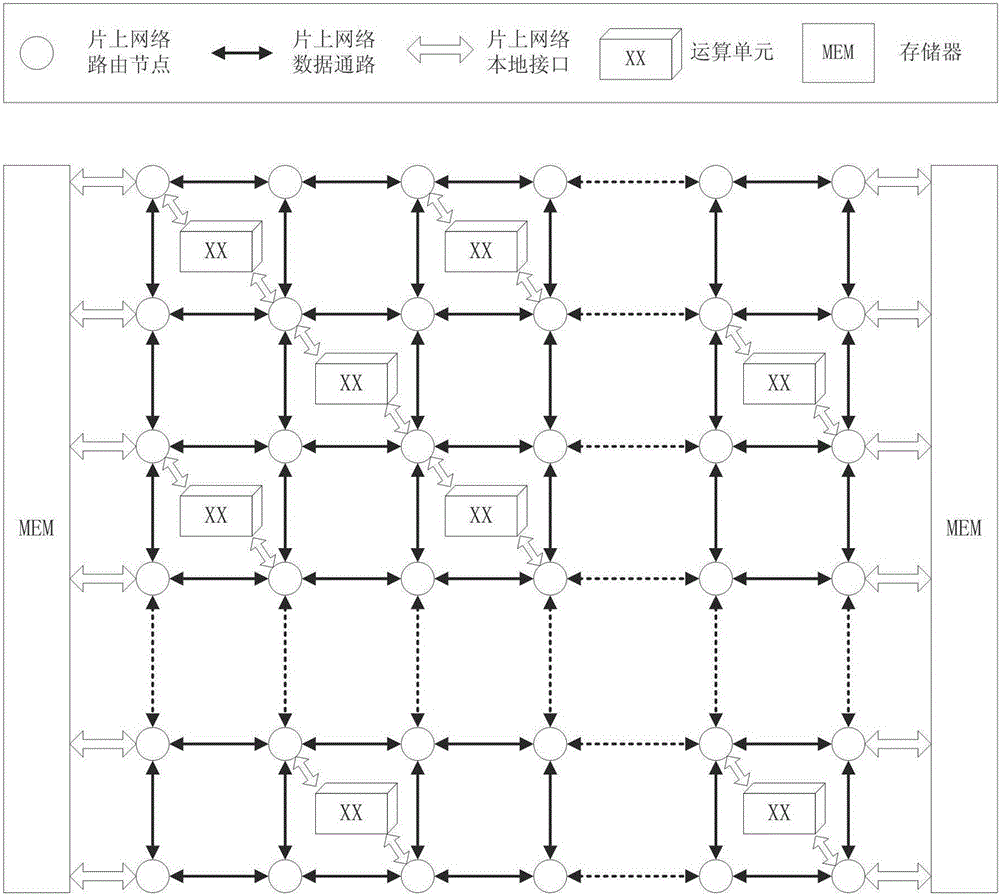

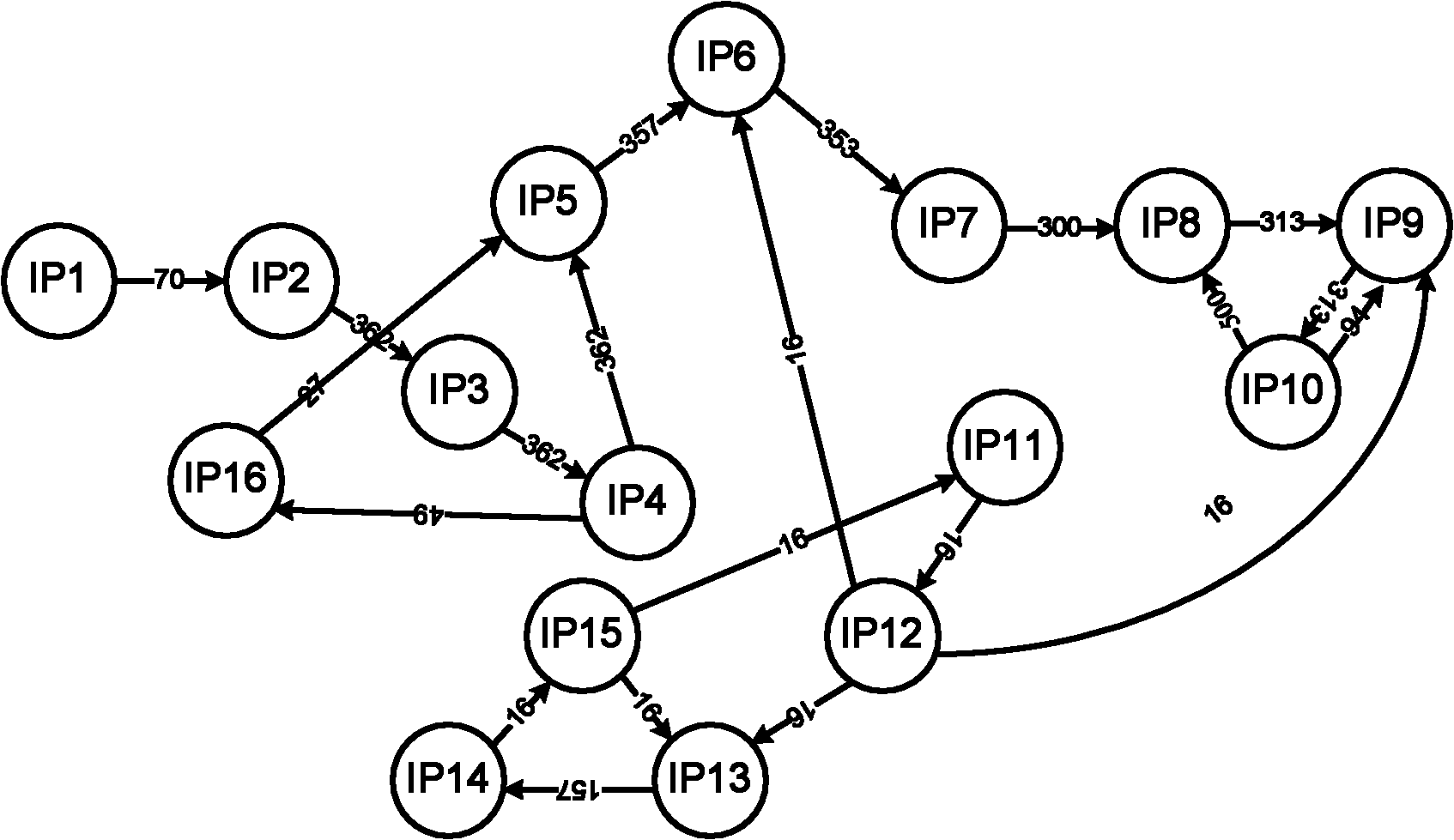

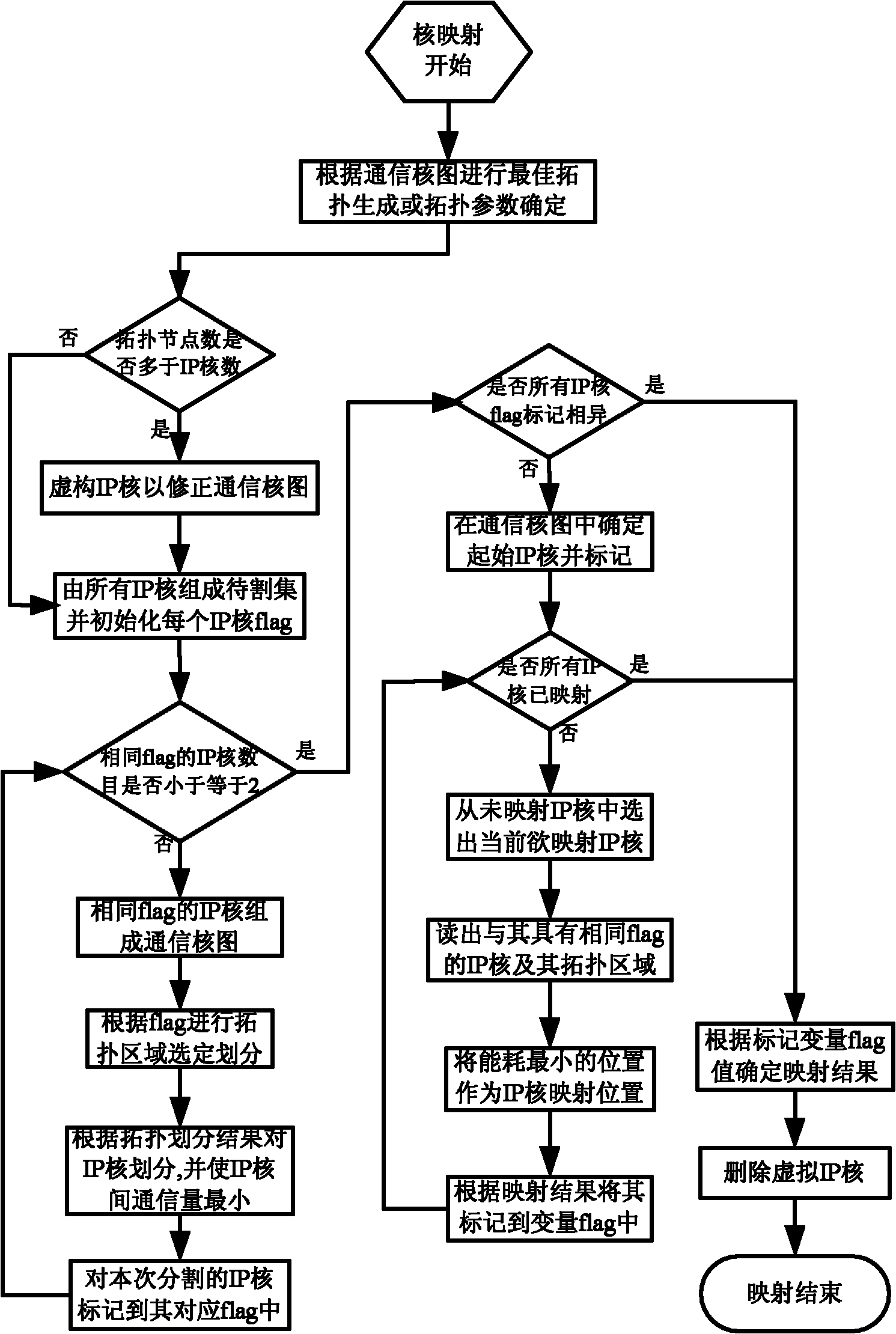

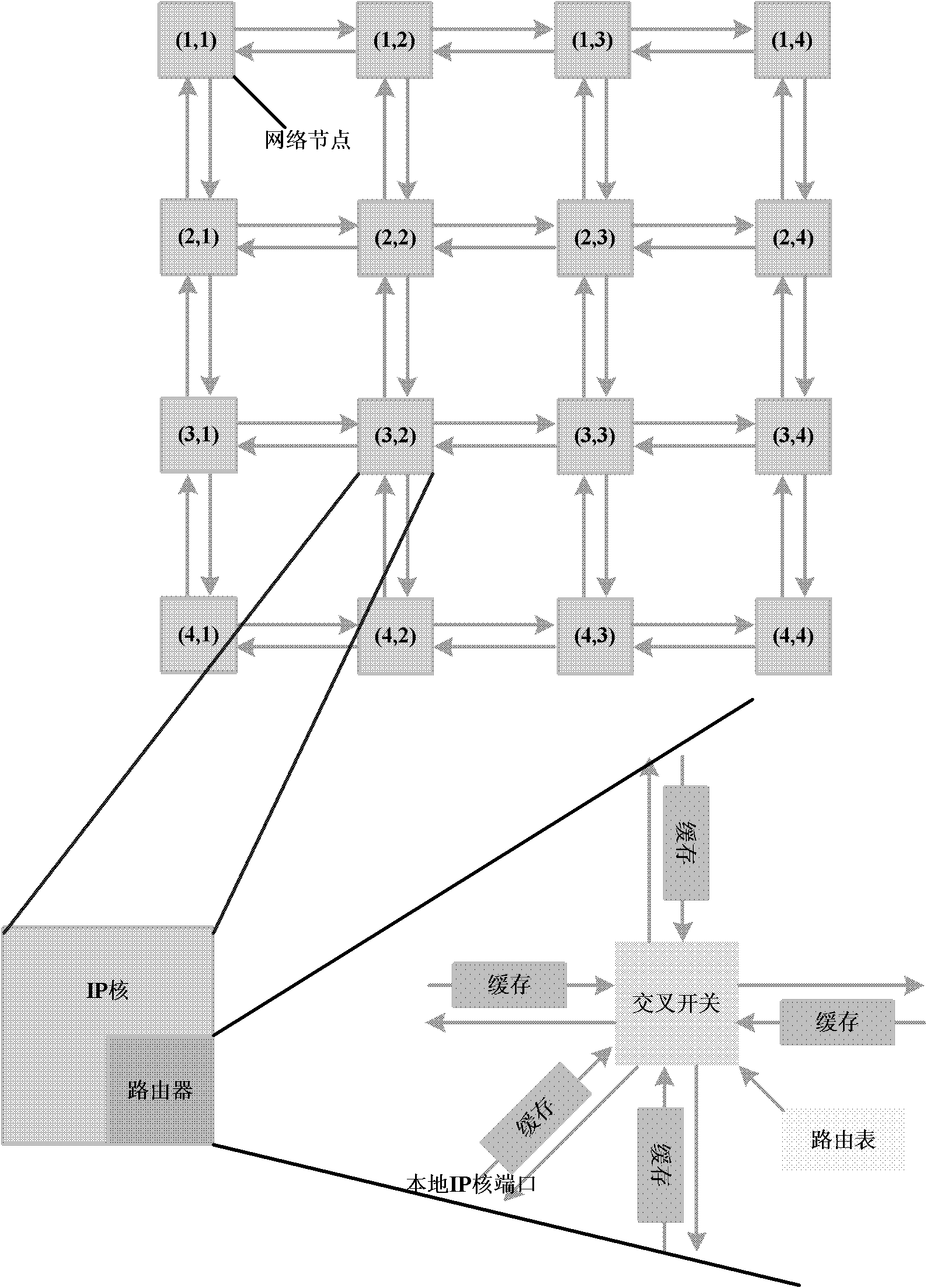

IP (Internet Protocol) core fast mapping method for network on chip based on region division

InactiveCN102065019AReduce complexityReduced execution timeData switching networksTraffic capacityRound complexity

The invention discloses an IP (Internet Protocol) core fast mapping method for network on chip based on region division, which mainly solves the problem of performance optimization when IP cores are mapped to network nodes. The method comprises the following steps of: (1) generating an optimal network topology according to the number of IP cores in a core communication graph, and enabling the IP cores to be virtual IP cores so as to correct the core communication graph if the node number in the optimal topology is more than the number of the IP cores; (2) dividing topological regions corresponding to IP cores to be mapped, and dividing and matching a corresponding number of IP cores to the core communication graph according to the topology division results; (3) determining and marking the specific location of each IP core in the network through location energy consumption calculation; and (4) mapping each IP core to a corresponding network node according to the mark of each IP core, deleting the virtual IP cores obtained in the step (1), and outputting final mapping results. The method disclosed by the invention reduces the computational complexity, avoids the generation of hot spots on a network center when guaranteeing the low energy consumption of full-network communication, improves the network reliability, and can be used for large-scale IP core fast mapping with the advantages of low energy consumption and flow equalization.

Owner:陕西光电子先导院科技有限公司

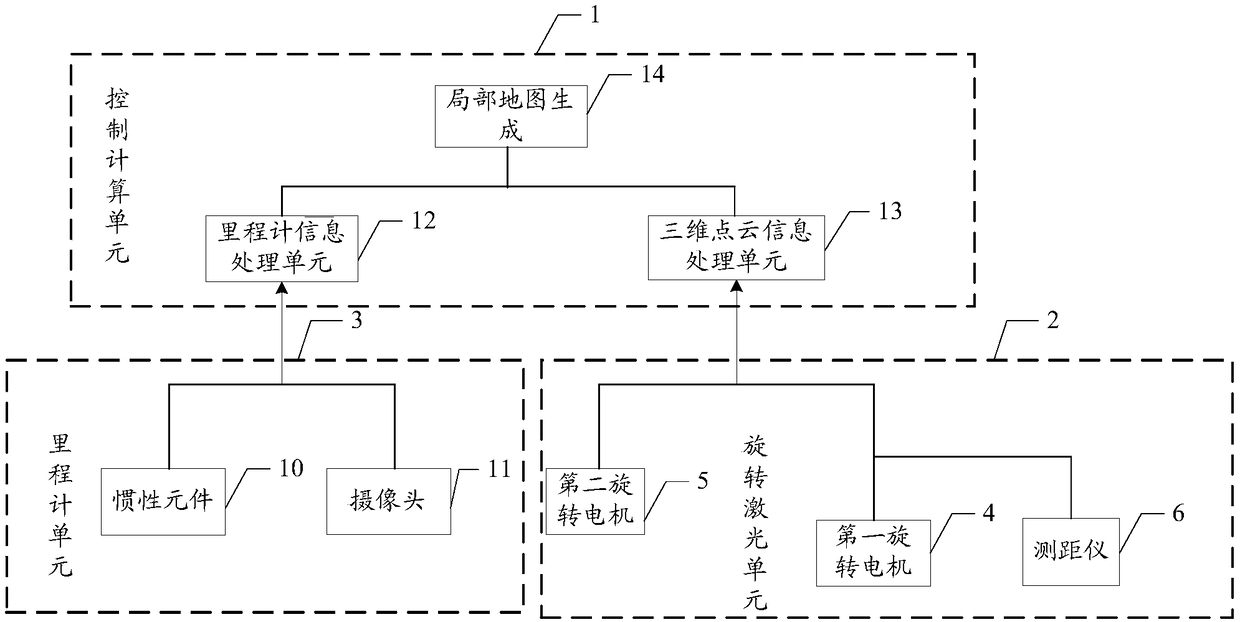

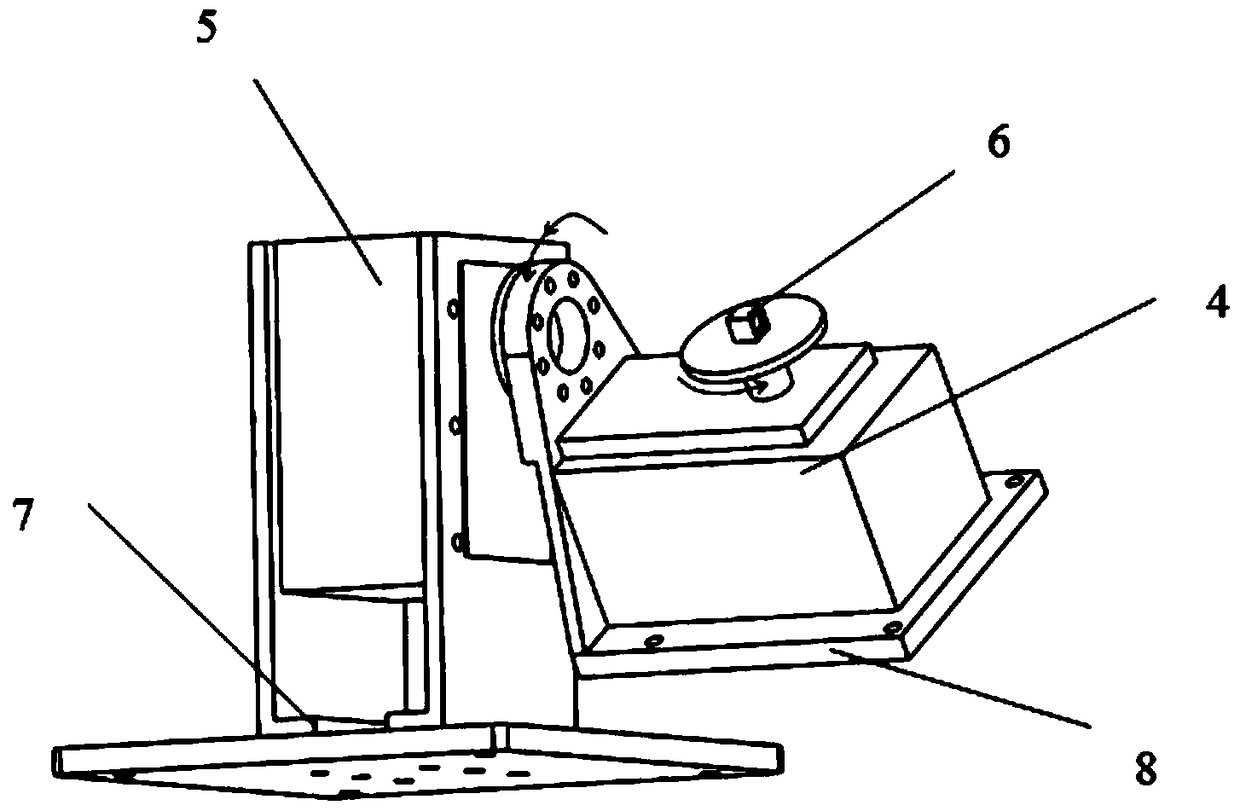

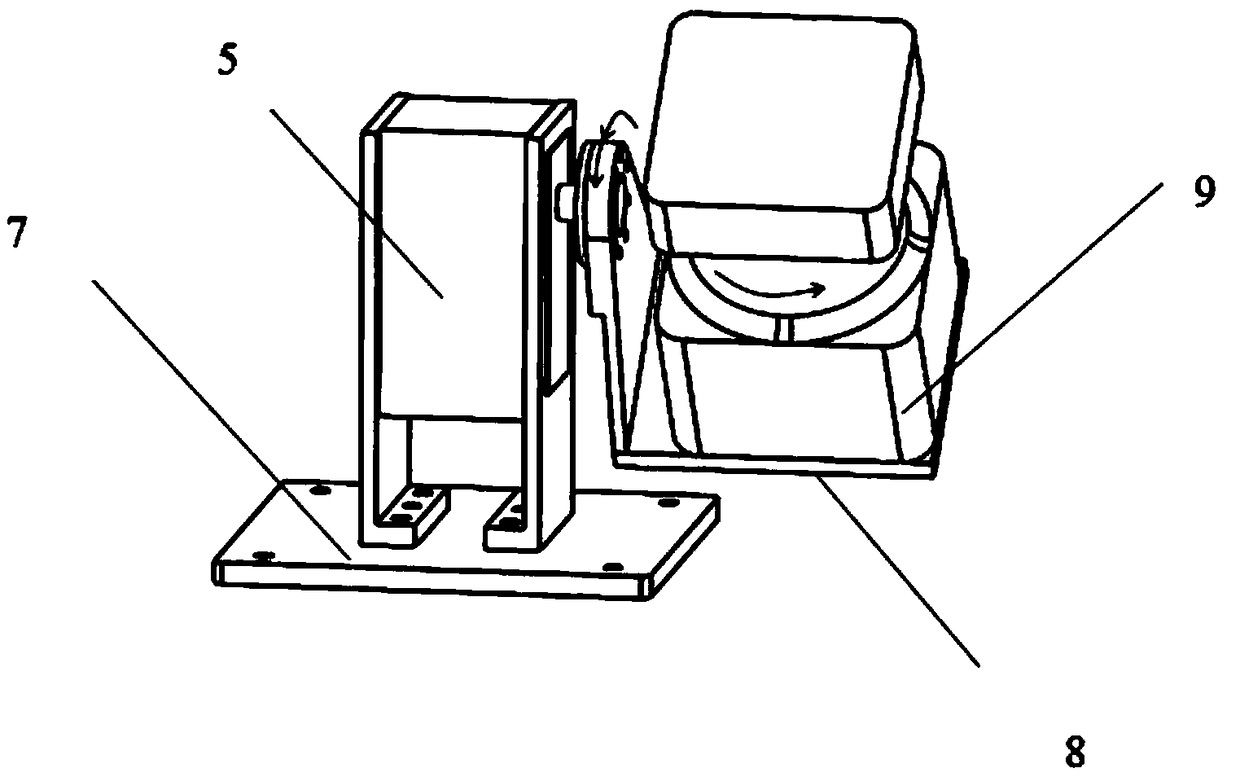

Omnibearing three-dimensional point cloud map generation method and system

InactiveCN108267748AIncrease generation speedIncrease rotation speedNavigation by speed/acceleration measurementsElectromagnetic wave reradiationPoint cloudRotation velocity

The present invention discloses an omnibearing three-dimensional point cloud map generation method and system. The system comprises a control calculation unit, a rotation laser unit and a speedometerunit. The rotation laser unit comprises a first rotation motor, a second rotation motor and a diastimeter. The diastimeter collects single-point point cloud data, the rotating speeds of the two rotating motors are controllable and collect poses corresponding to the point cloud, and the speedometer unit collects speedometer data, the control calculation unit performs processing of the collected single-point point cloud data, the poses and the speedometer data to generate local maps. An output shaft of the second rotation motor is fixedly connected with the first rotation motor in the system, anoutput shaft of the first rotation motor is provided with the diastimeter, the rotation direction of the first rotation motor is mutually perpendicular to the rotation direction of the second rotation motor, and under the action of the first rotation motor and the second rotation motor, the diastimeter can perform omnibearing laser scanning to obtain three-dimensional point cloud data in each direction and generate the local map in each direction.

Owner:THE CHINESE UNIV OF HONG KONG SHENZHEN

Method and apparatus for binding domain name and specific service

InactiveCN101505305AFlexible topologyEffective Dynamic SettingsTransmissionDomain nameBinding domain

The invention discloses a method for binding a domain name and specific service, which comprises the following steps that: 1) a mapped domain name is generated for a user and specific service; 2) a service storage address corresponding to the domain name is set; 3) a service client requests the analysis of the domain name; 4) a domain name analysis server analyzes the domain name to the corresponding service storage address; and 5) the service client sends the request to the service storage address to acquire the specific service. The technical proposal maps each specific user and specific service to the specific domain name, and the subsequent access of the user is positioned to a preset server by analyzing the specific domain name, thereby achieving the aim of flexible network topology configuration and achieving complete and most effective load balance.

Owner:杭州比比西网络科技有限公司

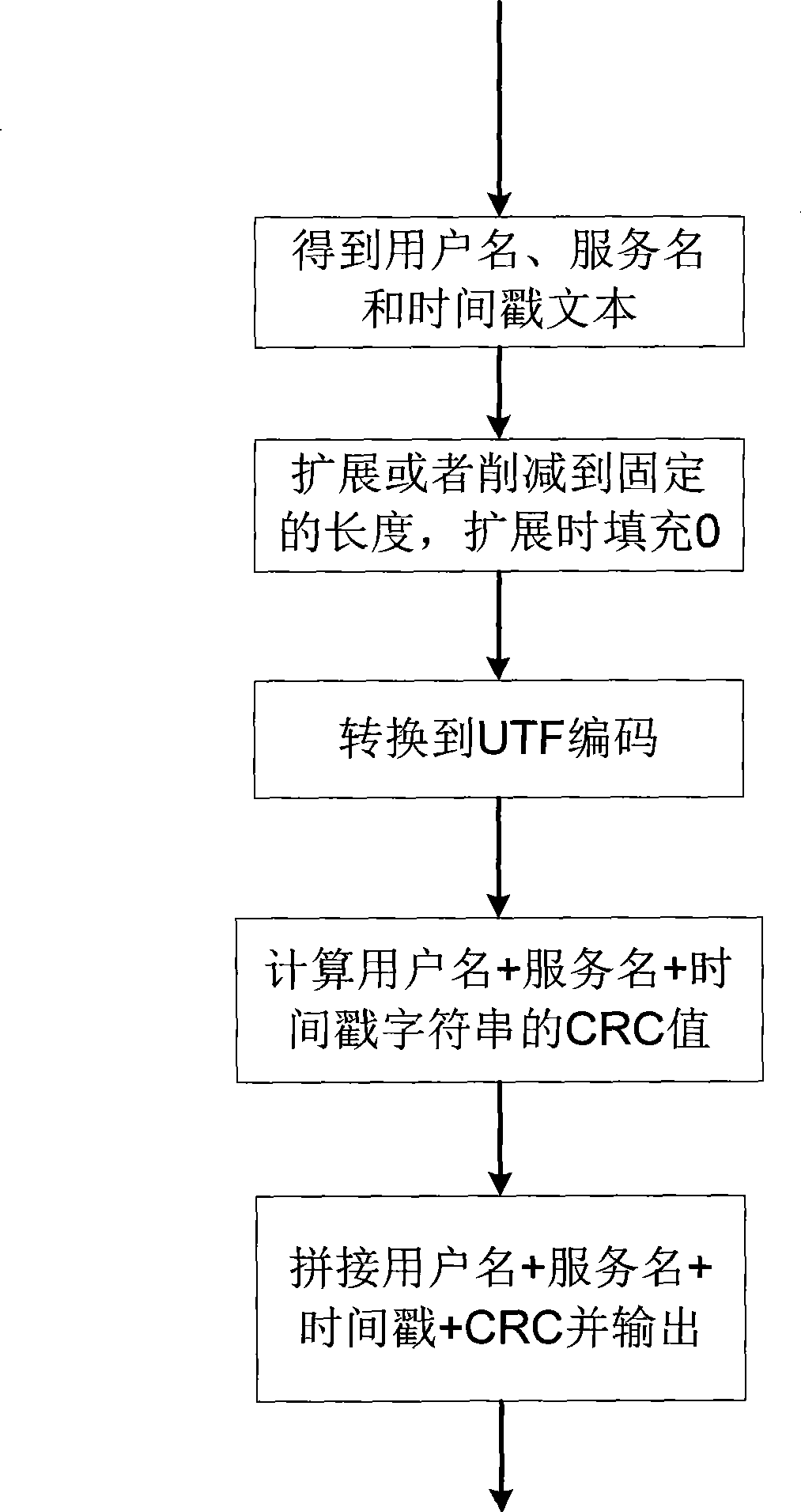

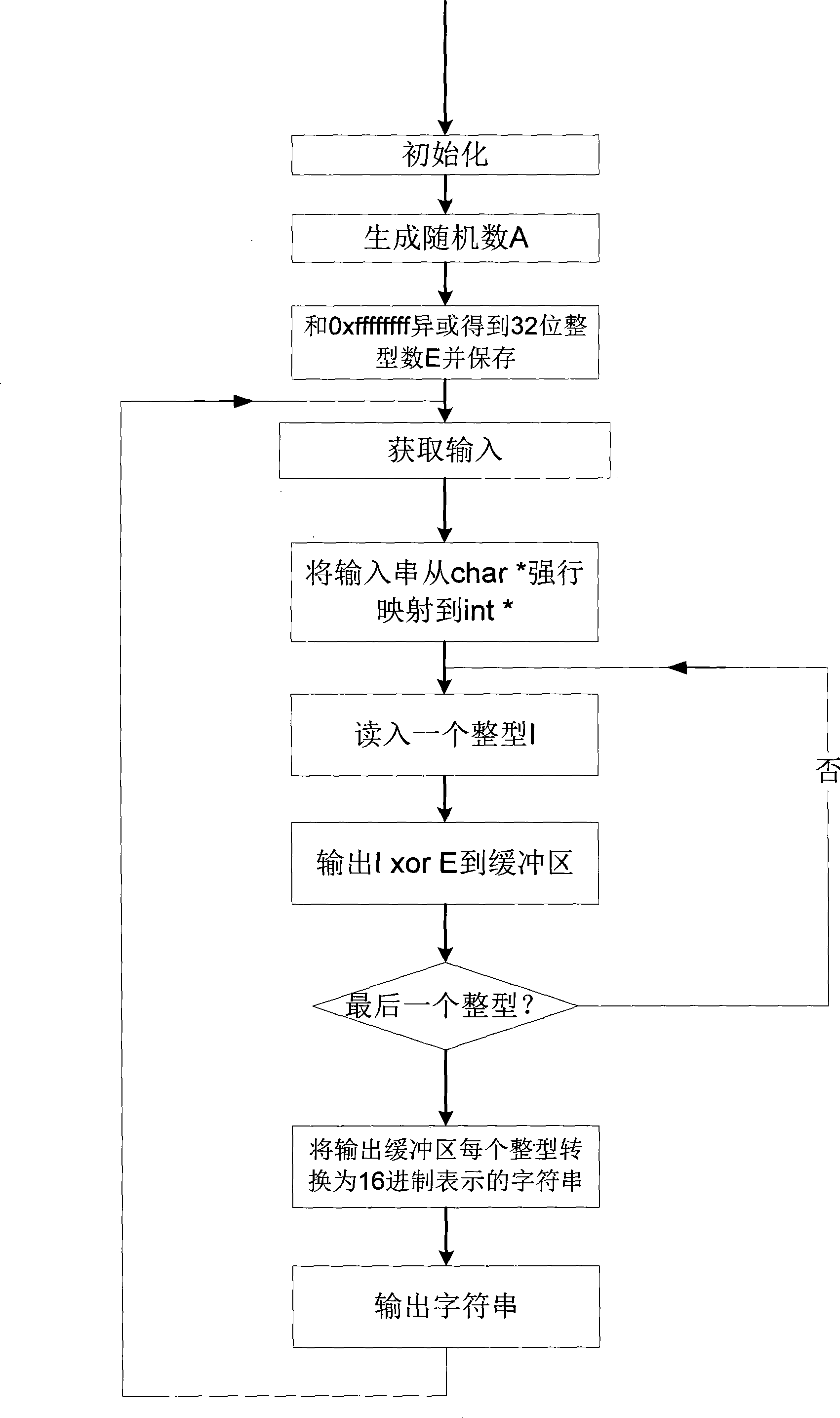

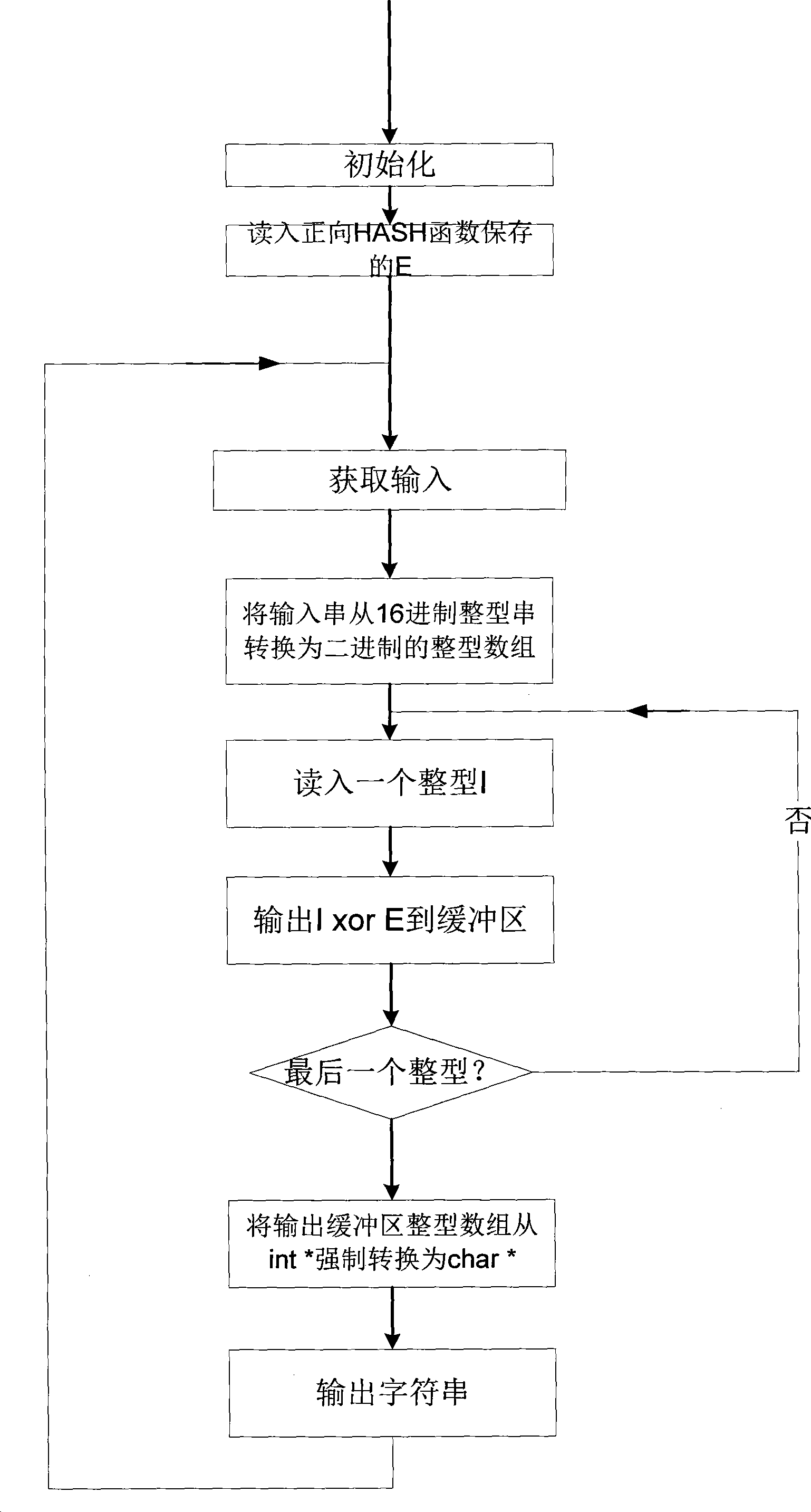

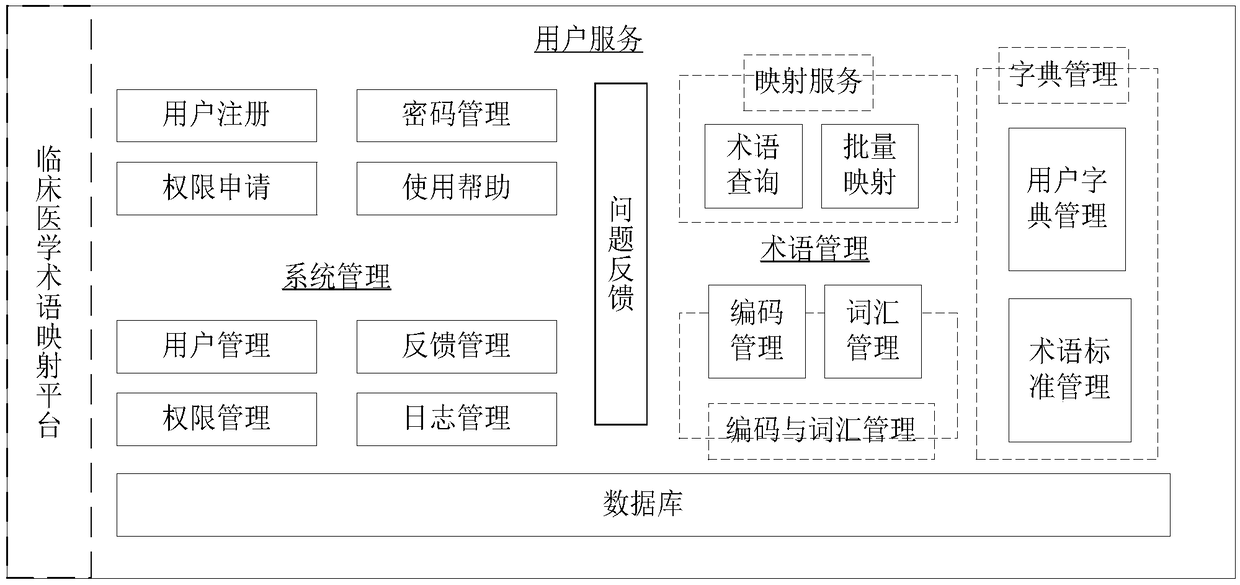

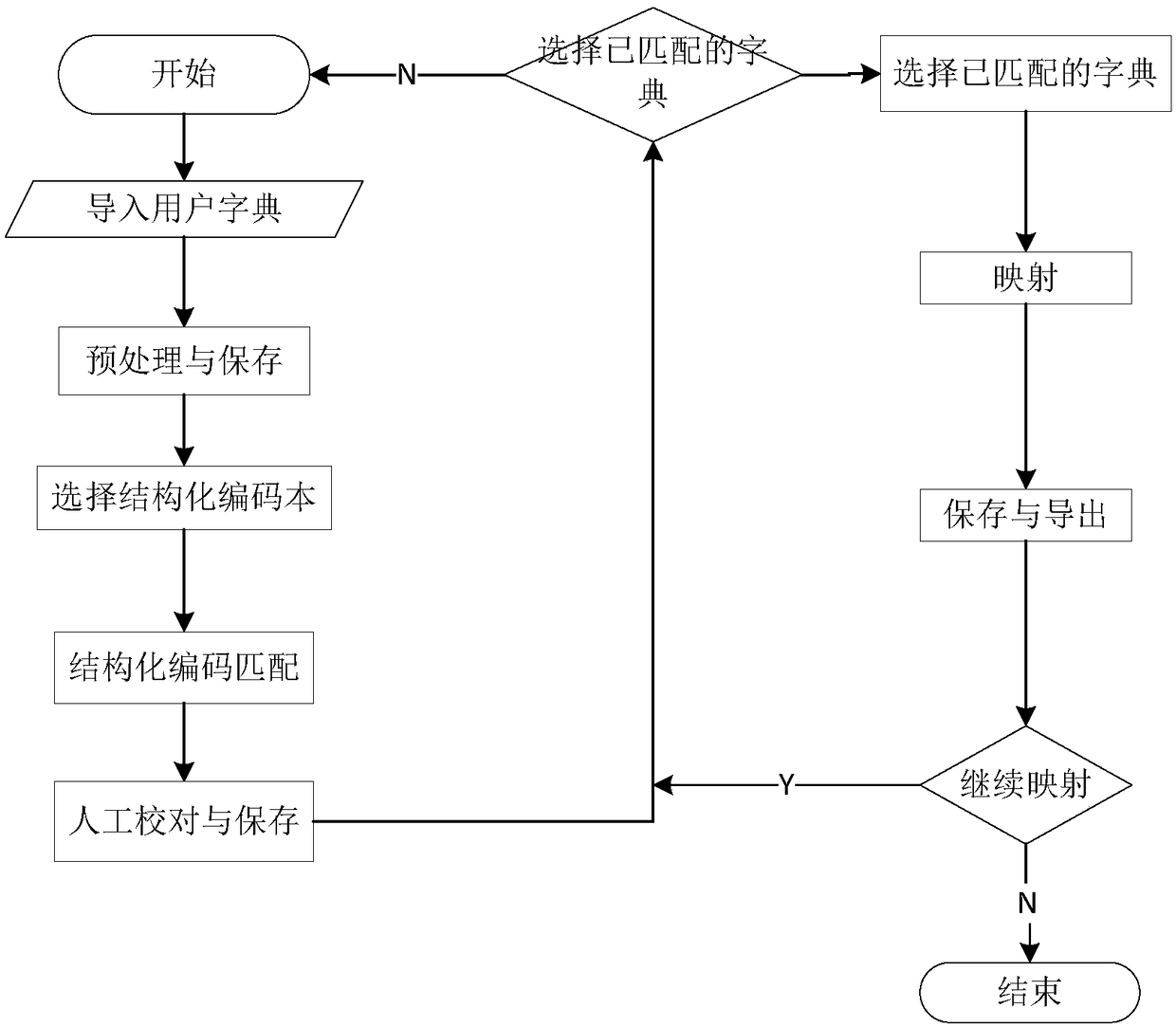

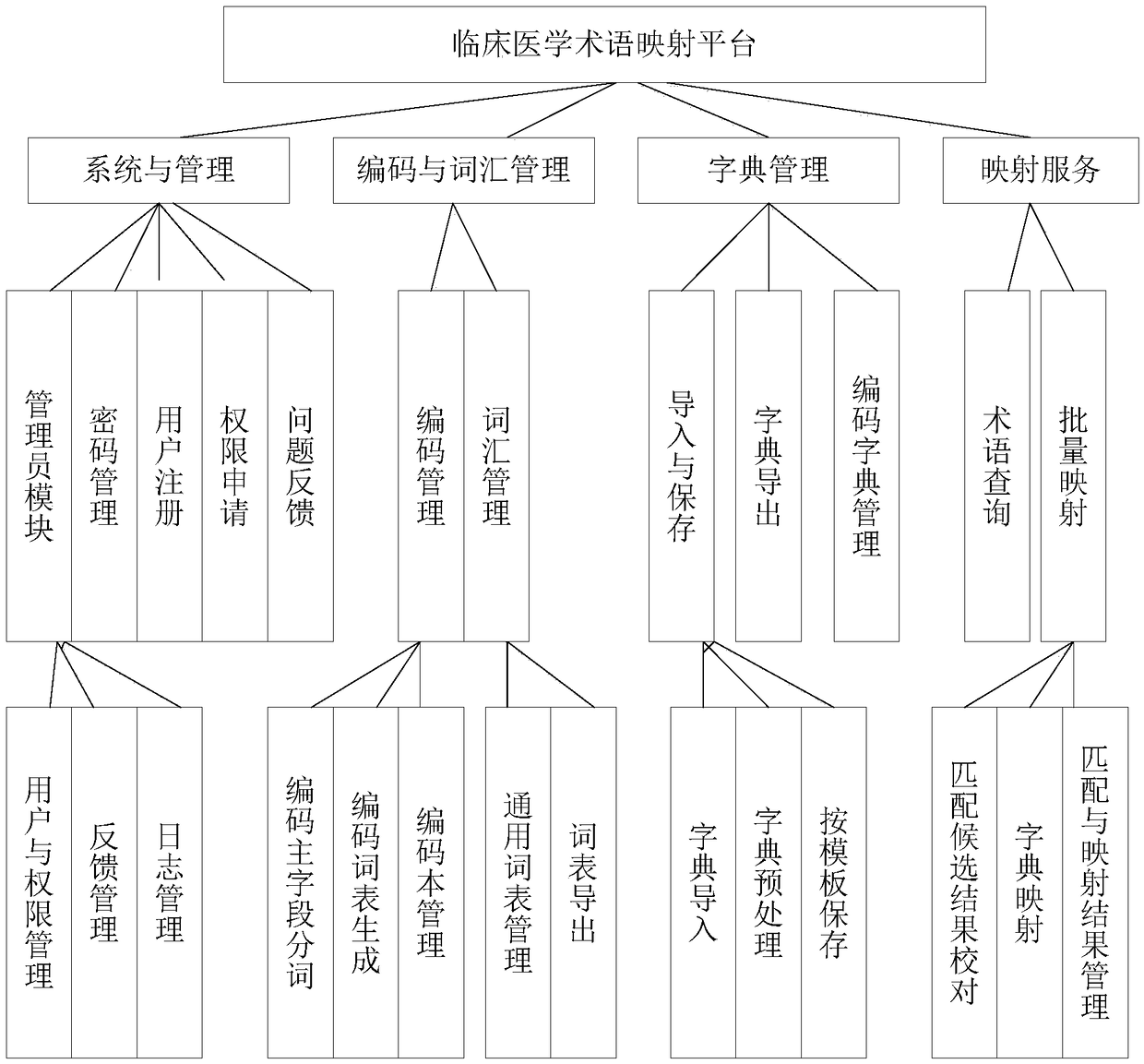

Medical term mapping system and method, apparatus and storage medium

InactiveCN109408820AQuick mapReduce manual workloadSemantic analysisPatient healthcareMedical terminologyChinese word

The invention discloses a medical term mapping system and method, a device and a storage medium, belonging to the technical field of life and health. The method comprises the following steps of: importing a user dictionary, preprocessing and saving; Selecting structured codebook, matching user dictionary and structured codebook, proofreading and saving the matched candidate manually; if the matching user dictionaries are selected, the two user dictionaries are mapped, and the mapping results are saved and exported. Also included are corresponding systems, devices, and storage media. It uses Chinese word segmentation technology and text correlation algorithm to design a set of fast mapping method of Chinese clinical medical terms based on the structured coding, and realizes the fast mappingof the same class of Chinese clinical medical terms. Based on this coding and mapping method, a mapping tool for Chinese clinical medical terms is designed and developed, which can reduce the manualwork and shorten the mapping time of Chinese clinical medical terms.

Owner:长沙瀚云信息科技有限公司

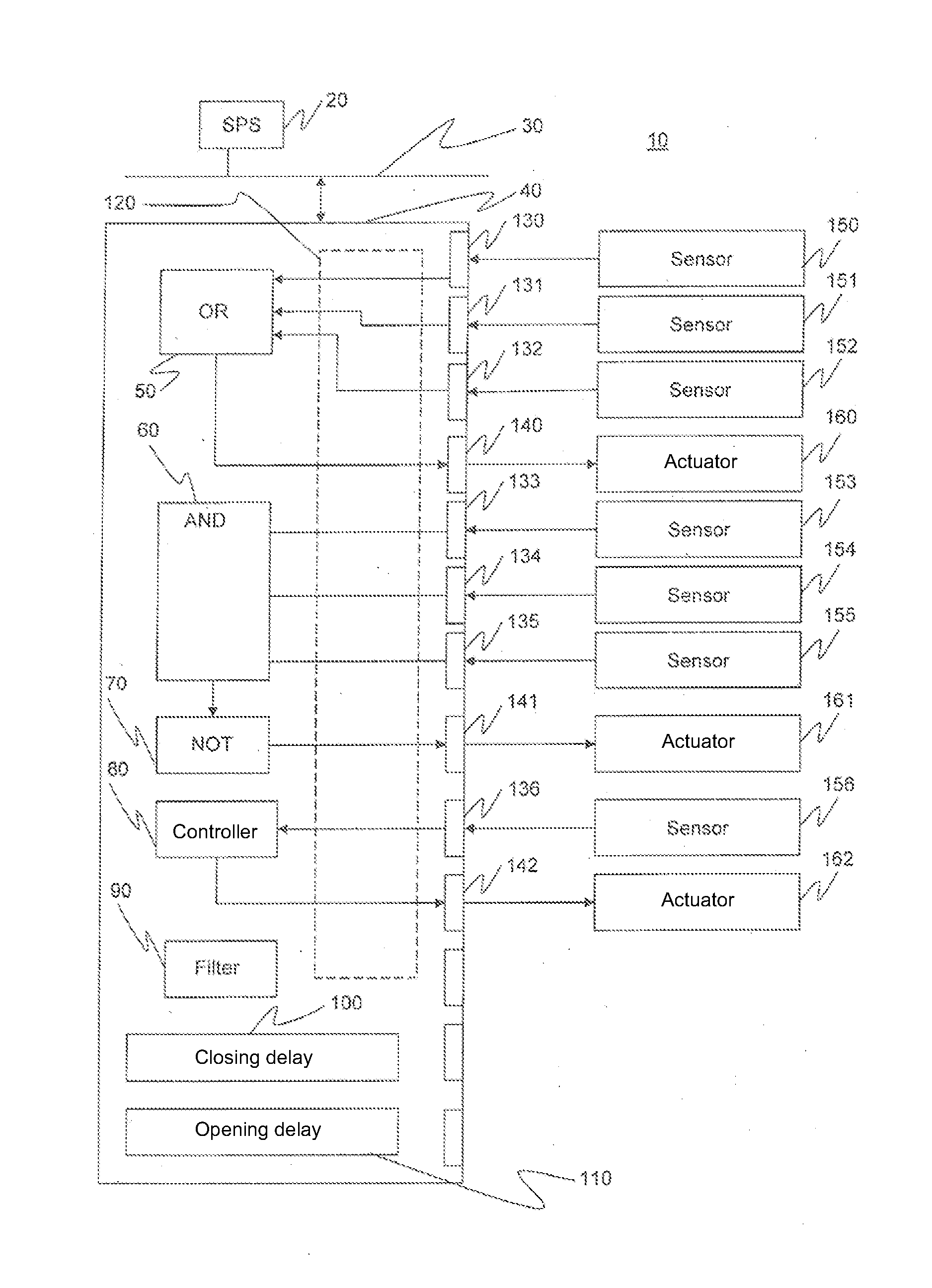

Communication system for connecting field devices to a higher-order control device

ActiveUS20130222123A1Mapped more quicklyQuick mapProgramme controlElectric signal transmission systemsEmbedded systemThrough transmission

To be able to achieve shorter communication cycles, the invention proposes a communication system which is able to connect field devices to a higher-order control device. For this purpose, a connection device is provided which is connectable to a higher-order control device via a transmission medium. The connection device has at least one first port and at least one second port, to each of which a field device may be connected. The connection device has at least one functional device which is switchable between at least one first port and at least one second port. The functional device is designed to generate output data intended for the second port in response to the input data arriving at the first port.

Owner:PHOENIX CONTACT GMBH & CO KG

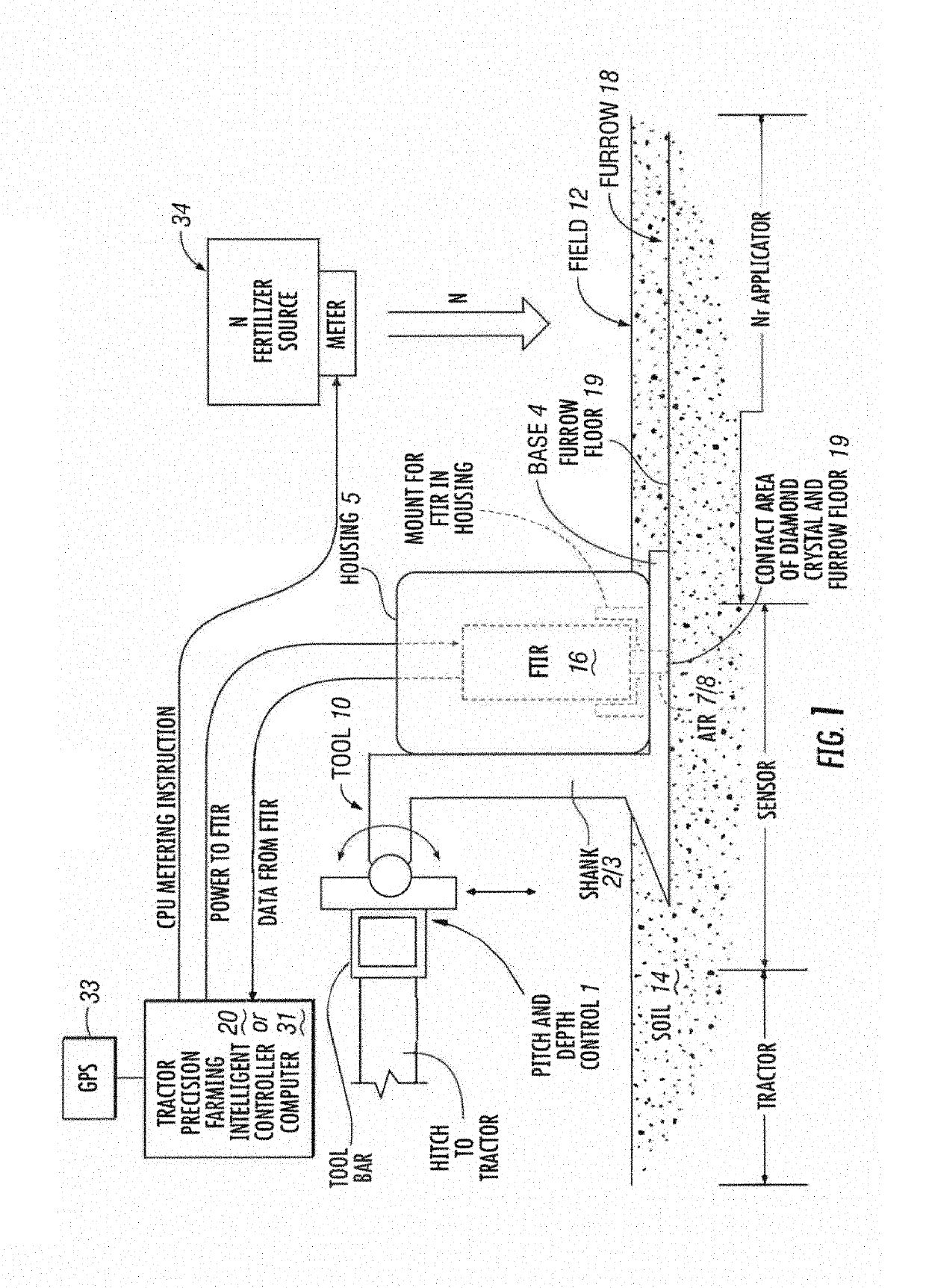

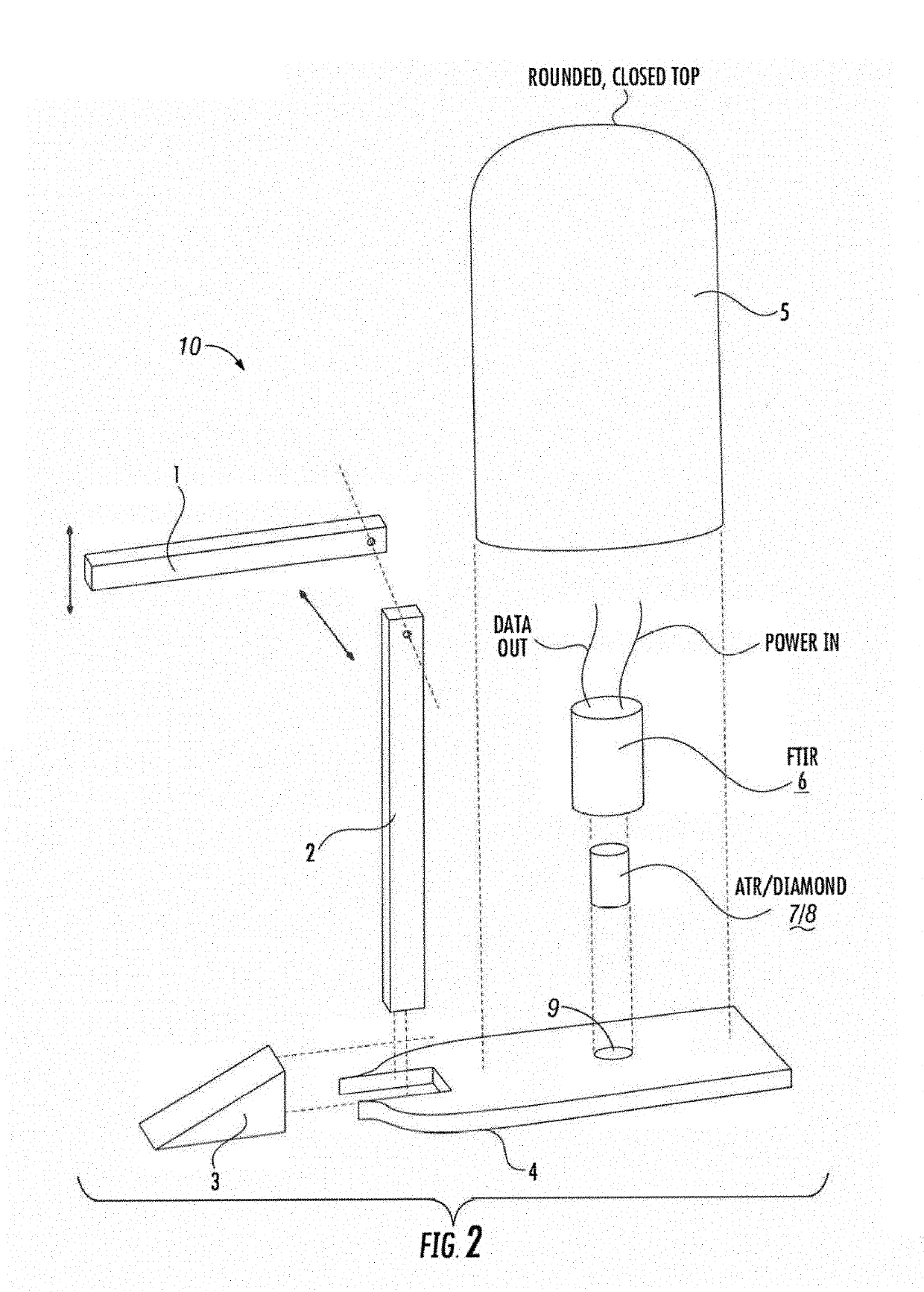

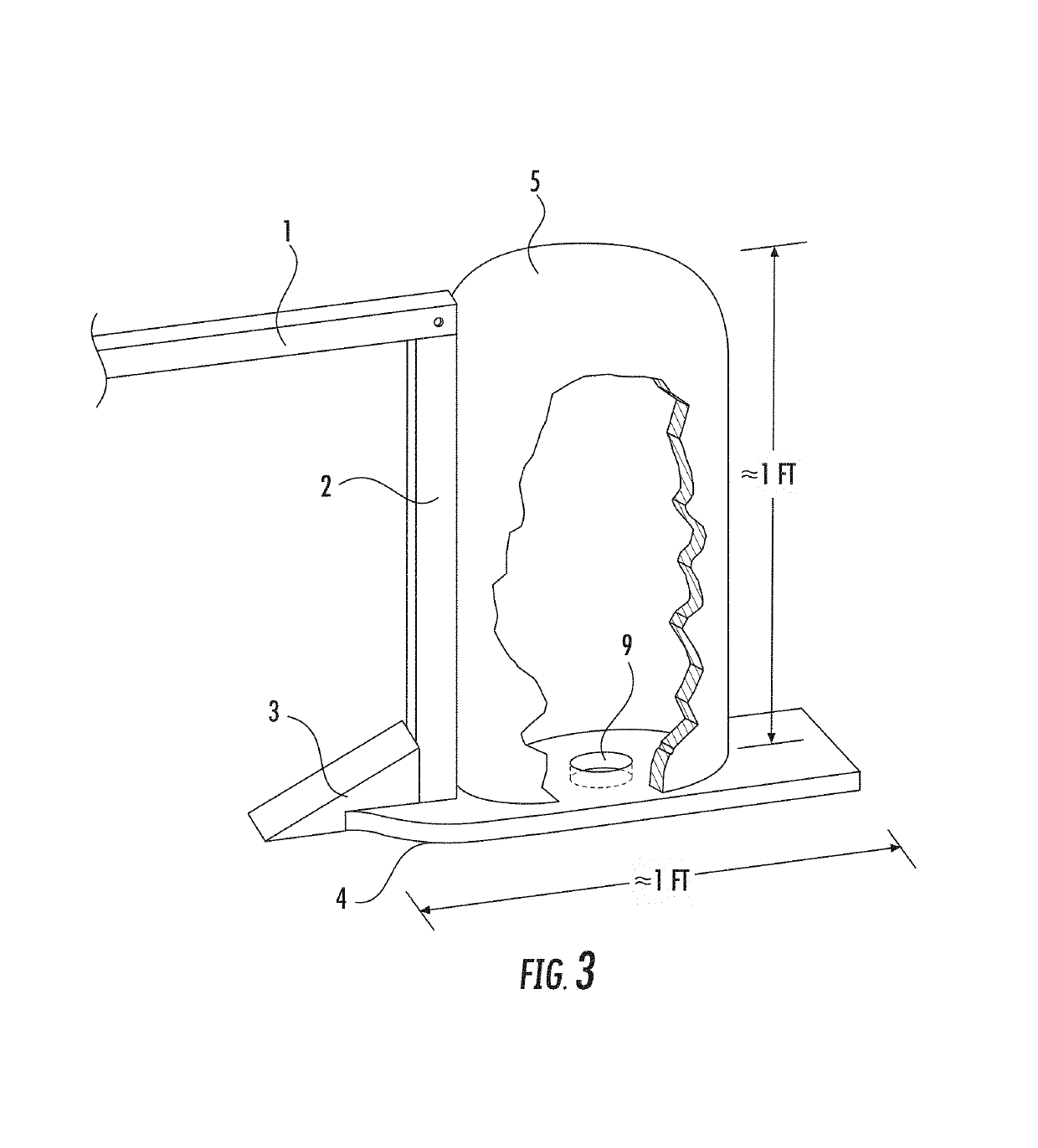

Soil nitrate sensing system for precision management of nitrogen fertilizer applications

ActiveUS10345283B1Facilitating precision applicationImprove accuracyEarth material testingFertilising methodsMedical prescriptionOptical surface

An apparatus, method, and system for on-the-go soil nitrate level sensing, and optionally using the sensing to inform or instruct nitrogen fertilizer application across the field. In one form, the apparatus includes a soil sensing tool which carries a diamond ATR cell in combination with an FTIR field ruggedized spectrometer. The optical surface of the diamond ATR cell can be adjusted in pitch and depth to the soil. A processor is programmed to manipulate acquired spectra to derive a prediction of nitrate level for a given soil position in the field. This can be used to modulate a fertilizer applicator operation or coupled with georeference data collected simultaneously to generate a map of soil nitrate levels for the field, which can be used as a prescription for nitrogen fertilizer application.

Owner:IOWA STATE UNIV RES FOUND

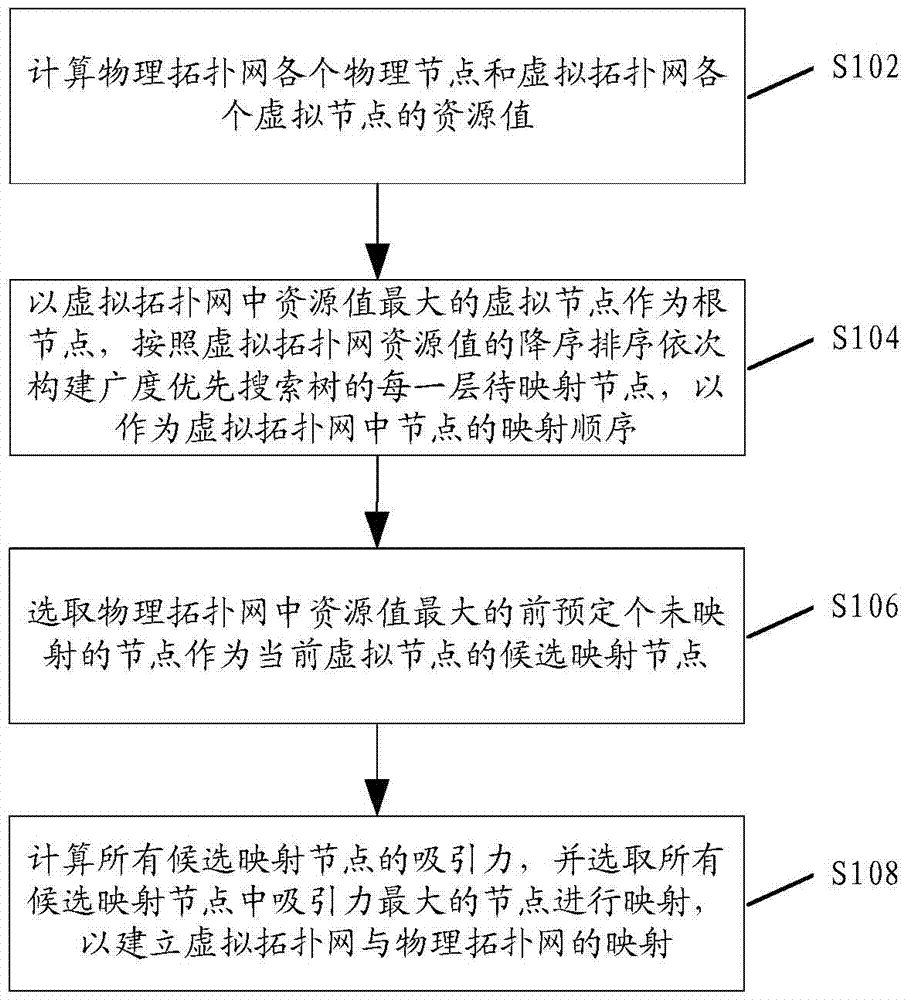

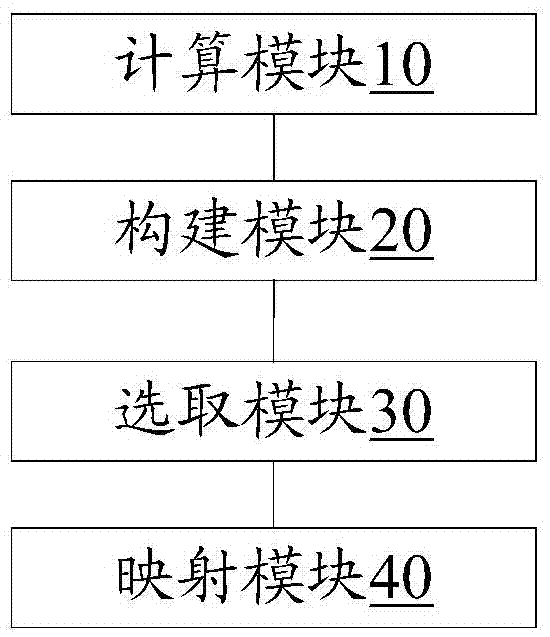

Virtual mapping method and virtual mapping device

ActiveCN106961343AIncrease acceptance rateQuick mapData switching networksDistributed computingVirtual network mapping

The invention discloses a virtual mapping method and a virtual mapping device. The virtual mapping method comprises steps that resource values of various physical nodes of a physical topology network and resource values of various virtual nodes of a virtual topology network are calculated; the virtual node having the maximum resource value of the virtual topology network is used as a root node, according to the descending sort of the resource values of the virtual topology network, every layer of to-be-mapped nodes of a breadth first search tree is built sequentially to be used as the mapping sequence of the nodes of the virtual topology network; the unmapped nodes previous to the node having the maximum resource value of the physical topology network by a predetermined number are used as candidate mapping nodes of a current virtual node; the attraction of all of the candidate mapping nodes is calculated, and the node having the greatest attraction of the candidate mapping node is selected for mapping, and the mapping between the virtual topology network and the physical topology network is established. The problem of the virtual network mapping method of the prior art of large data processing amount caused by requirement on the traversal of the nodes satisfying requirements is solved.

Owner:ZTE CORP

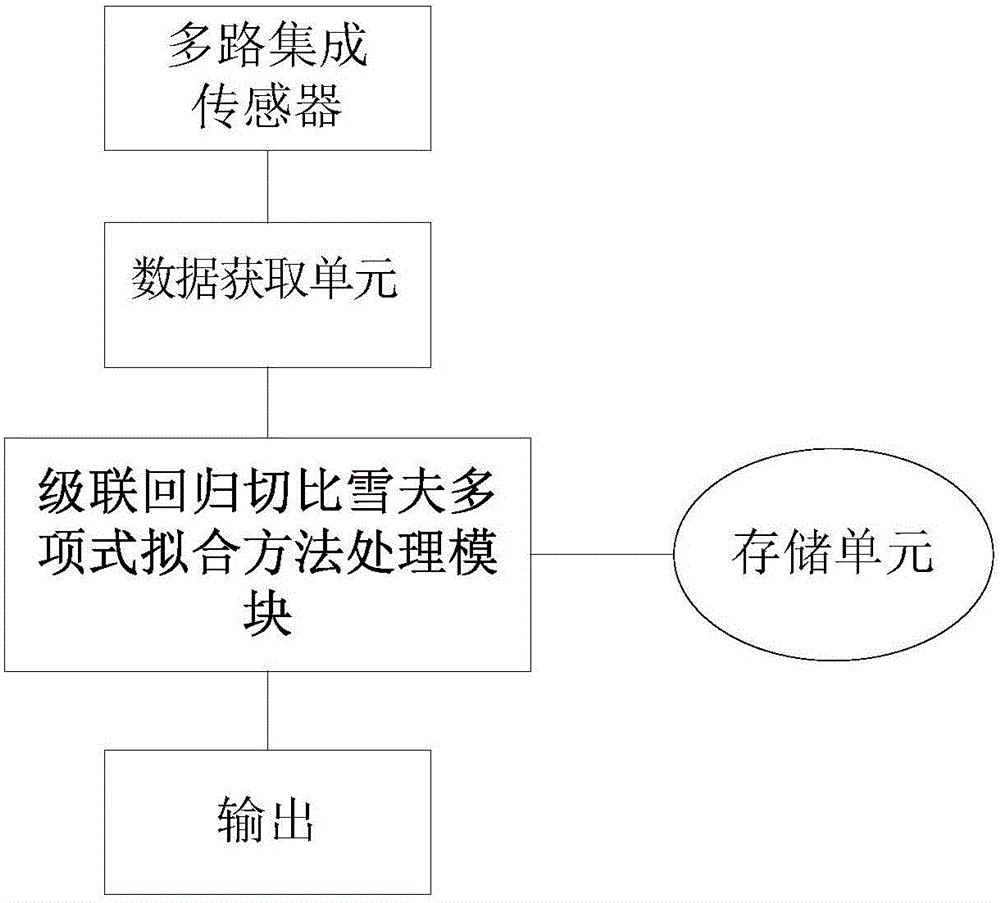

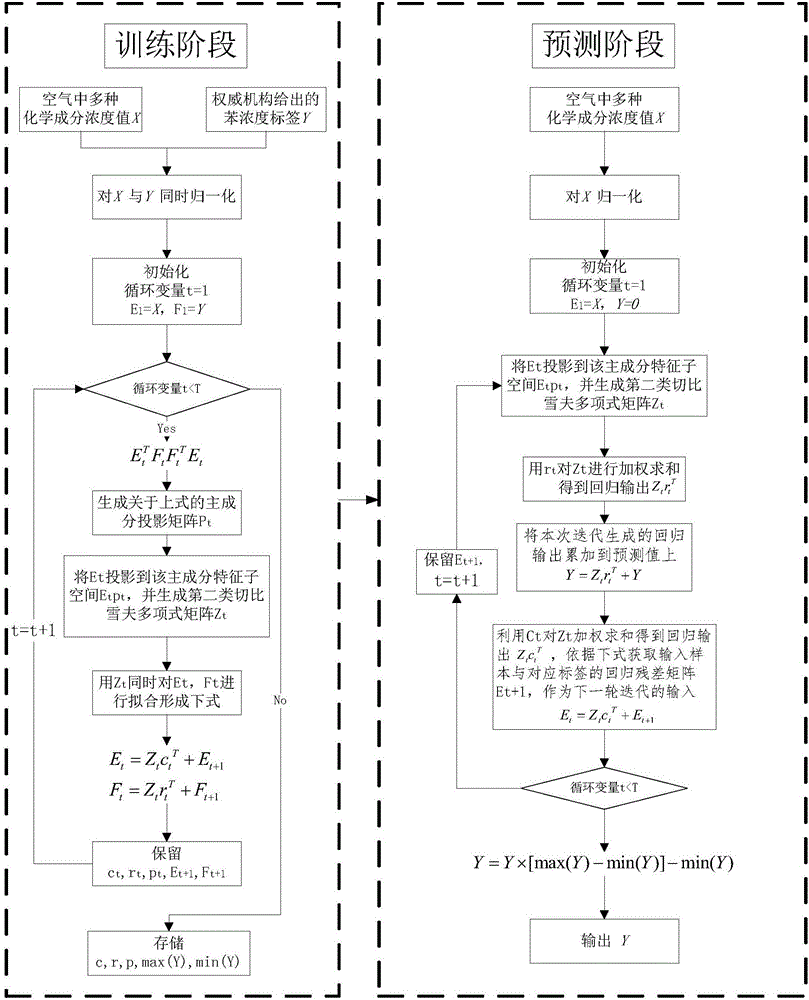

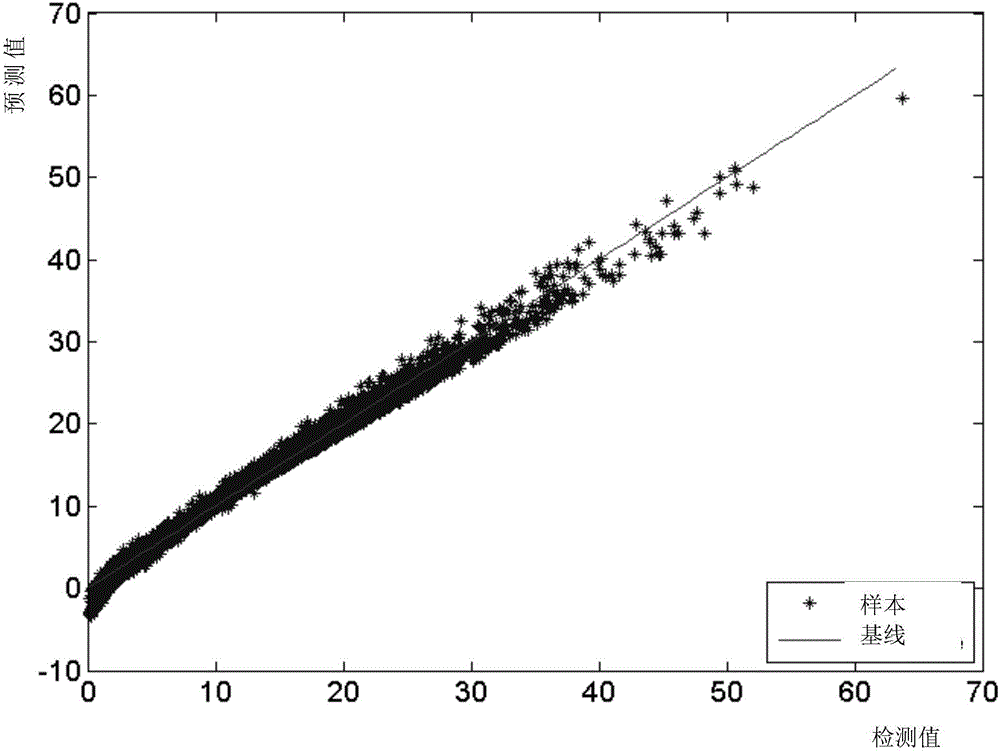

Air quality detection method and air quality detection system

The invention relates to an air quality detection method and an air quality detection system. The air quality detection method comprises the steps of obtaining proportions of different chemical radicals during each time period in air by utilizing multi-channel sensors to serve as variables; preprocessing data to obtain an input of a regression device; dividing the whole regression device into a training link and a detection link; in the training link, performing multi-time iteration on each training sample and a corresponding tag to obtain a regression coefficient and auxiliary parameters of a corresponding frequency; and in a test link, realizing estimation of air quality after multi-time superposition by directly utilizing related parameters and the regression coefficient obtained by training. According to the method and the system, the mapping from an input feature to a predicted value can be quickly and accurately finished for multivariant nonlinear regression problems at the same time, so that more accurate detection in environment monitoring can be realized conveniently.

Owner:BEIJING UNIV OF TECH

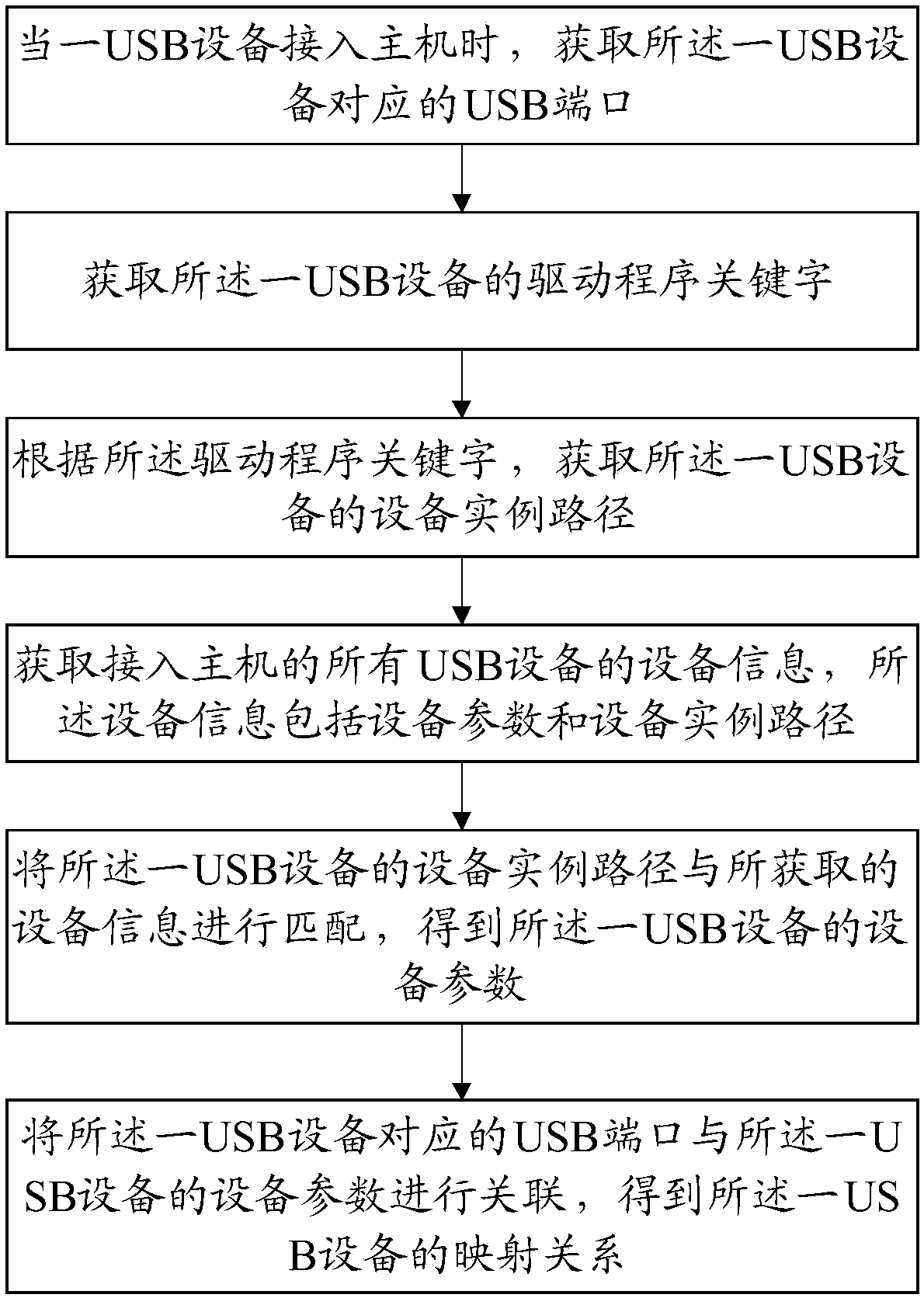

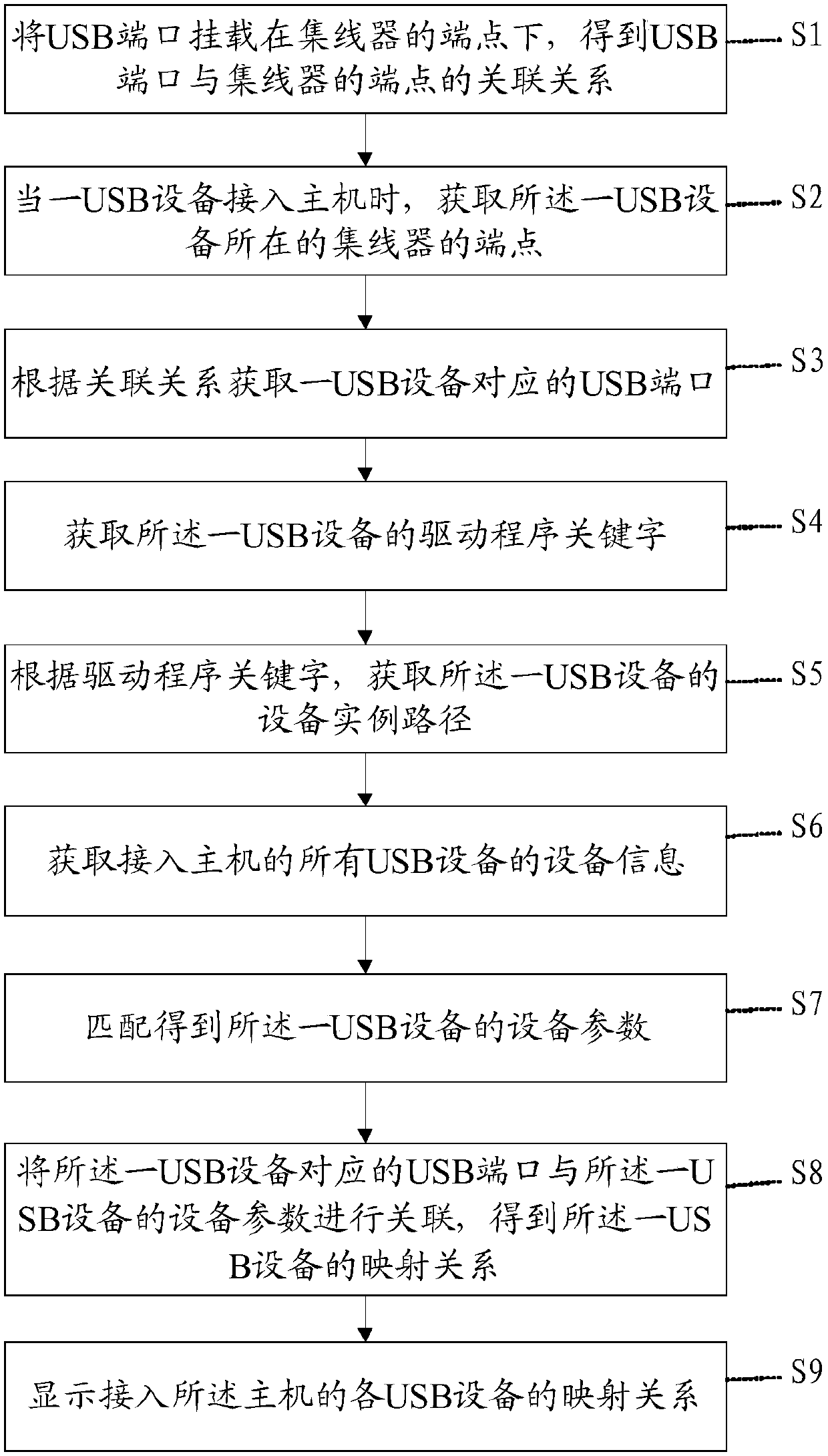

USB (Universal Serial Bus) port mapping method and computer readable storage medium

The invention discloses a USB (Universal Serial Bus) port mapping method and a computer readable storage medium. The method comprises the steps of acquiring a USB port corresponding to a USB device when the USB device is accessed to a mainframe; acquiring a drive program keyword of the USB device; acquiring a device instance route of the USB device according to the drive program keyword; acquiringdevice information of all USB devices accessed to the mainframe, wherein the device information includes a device parameter and the device instance route; matching the device instance route of the USB device with the acquired device information to obtain the device parameter of the USB device; and associating the USB port corresponding to the USB device with the device parameter of the USB deviceto obtain a mapping relation of the USB device. According to the USB port mapping method and the computer readable storage medium, rapid mapping between the USB port and the USB device can be realized to achieve the effect of rapid distinguishing, and the problem of complex parallel operations in the industry of mobile phone forensics is solved and the work efficiency is improved.

Owner:XIAMEN MEIYA PICO INFORMATION

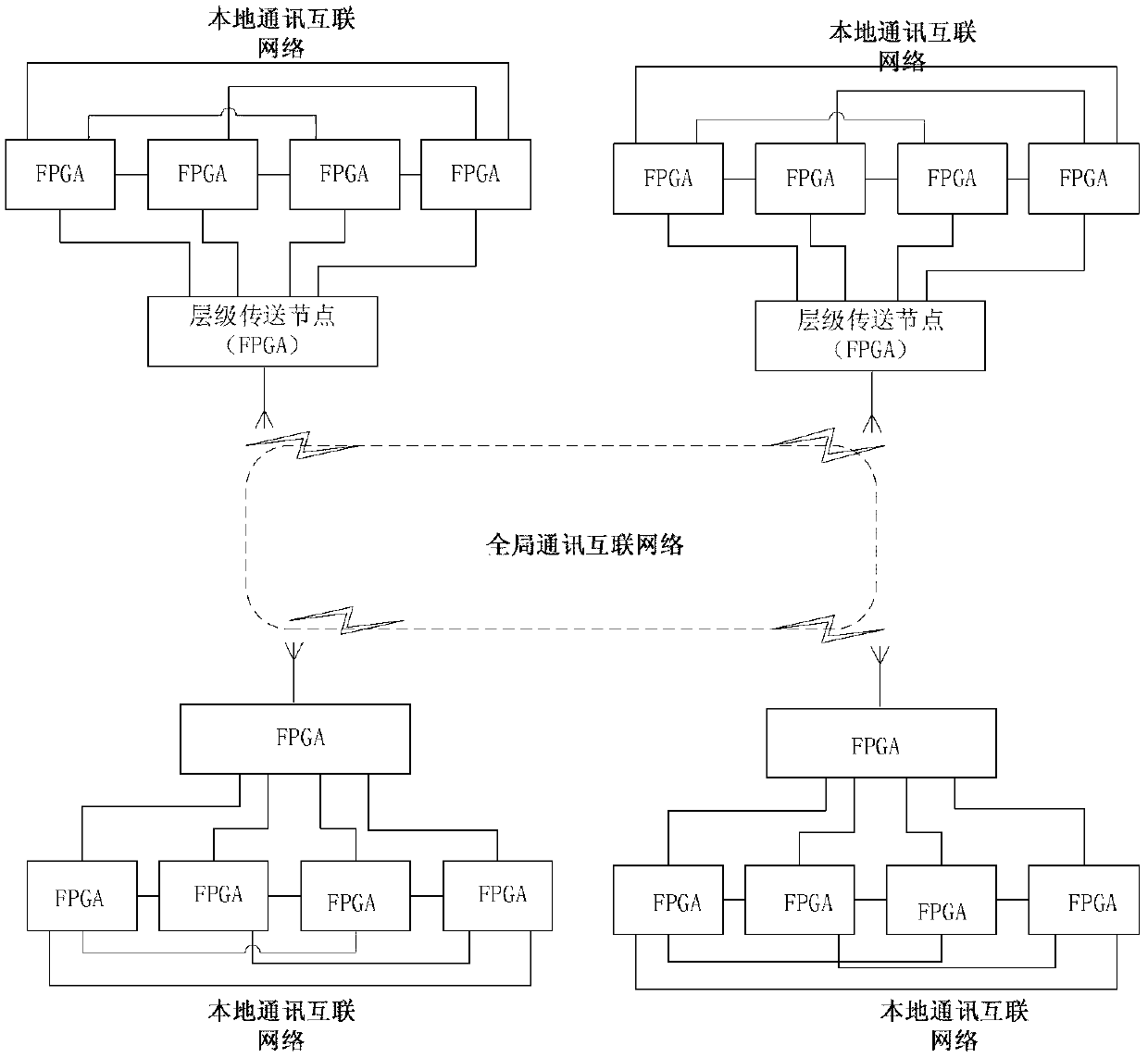

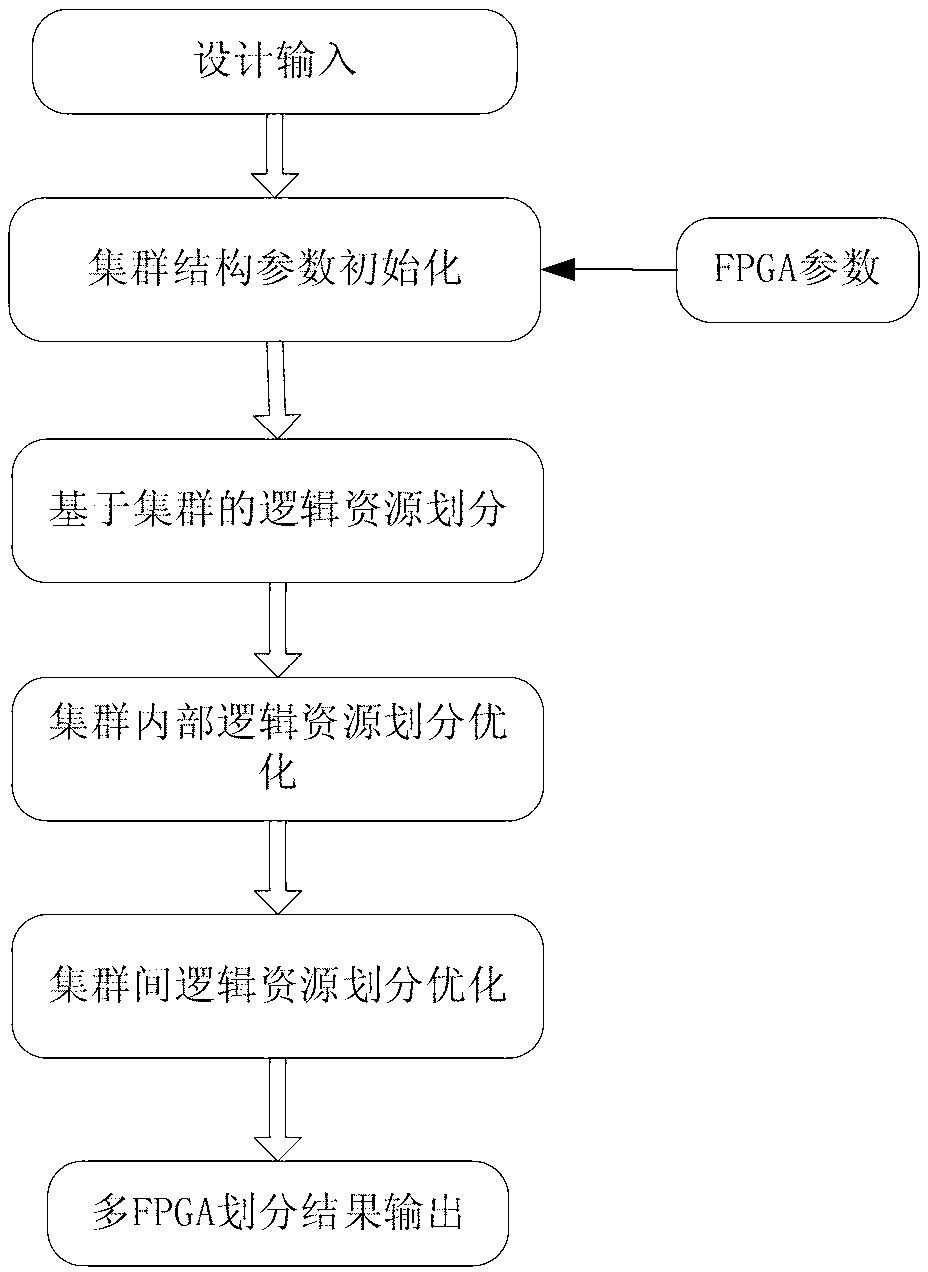

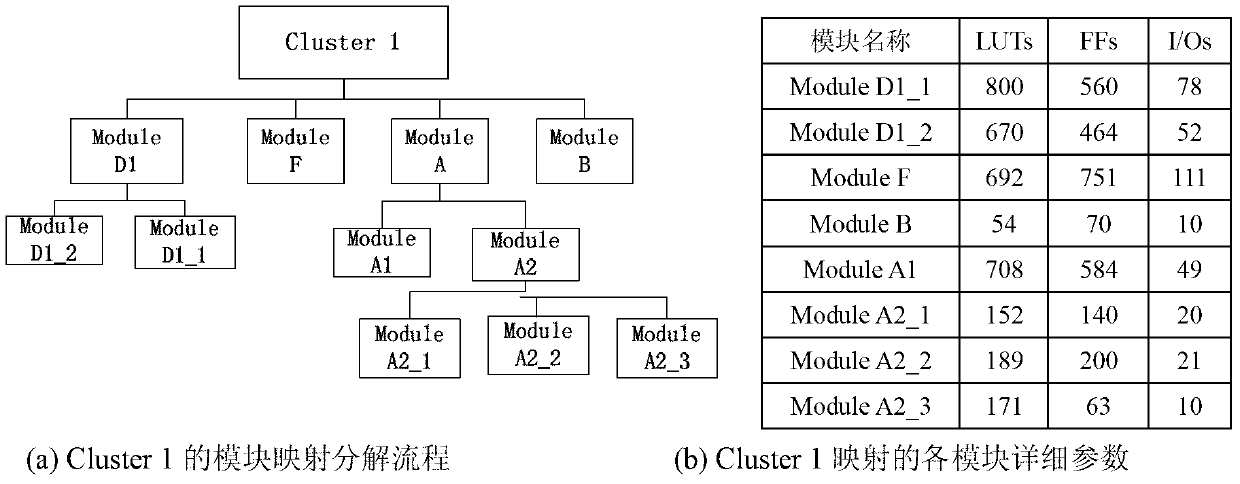

Multi-FPGA interconnection structure and logic partitioning method oriented to high-performance computing

InactiveCN103345458AReduce interconnection overheadMeet high performance requirementsResource allocationPerformance computingInterconnection

The invention provides a multi-FPGA interconnection structure oriented to high-performance computing. The multi-FPGA interconnection structure comprises local communication interconnection networks and a global communication interconnection network. The local communication interconnection networks are of a full interconnection structure, and FPGA nodes can directly conduct communication with other FPGA nodes in the same local communication interconnection network. The global communication interconnection network is a high-speed communication interconnection channel and used for conducting communication among the local communication interconnection networks. The invention further provides a multi-FPGA logic partitioning method oriented to high-performance computing. The method includes the following steps of cluster structure parameter initialization and logical resource mapping. The multi-FPGA interconnection structure and logic partitioning method fully utilize the characteristics of locality and heterogeneity of large-scale computing, combine the topological structure and a logic partitioning algorithm, reduce system communication interconnection cost, achieve rapid and efficient mapping of larger-scale design to a multi-FPGA high-performance computing platform, and speed up the implementation of the design of a high-performance configurable computing system.

Owner:BEIJING UNIV OF TECH

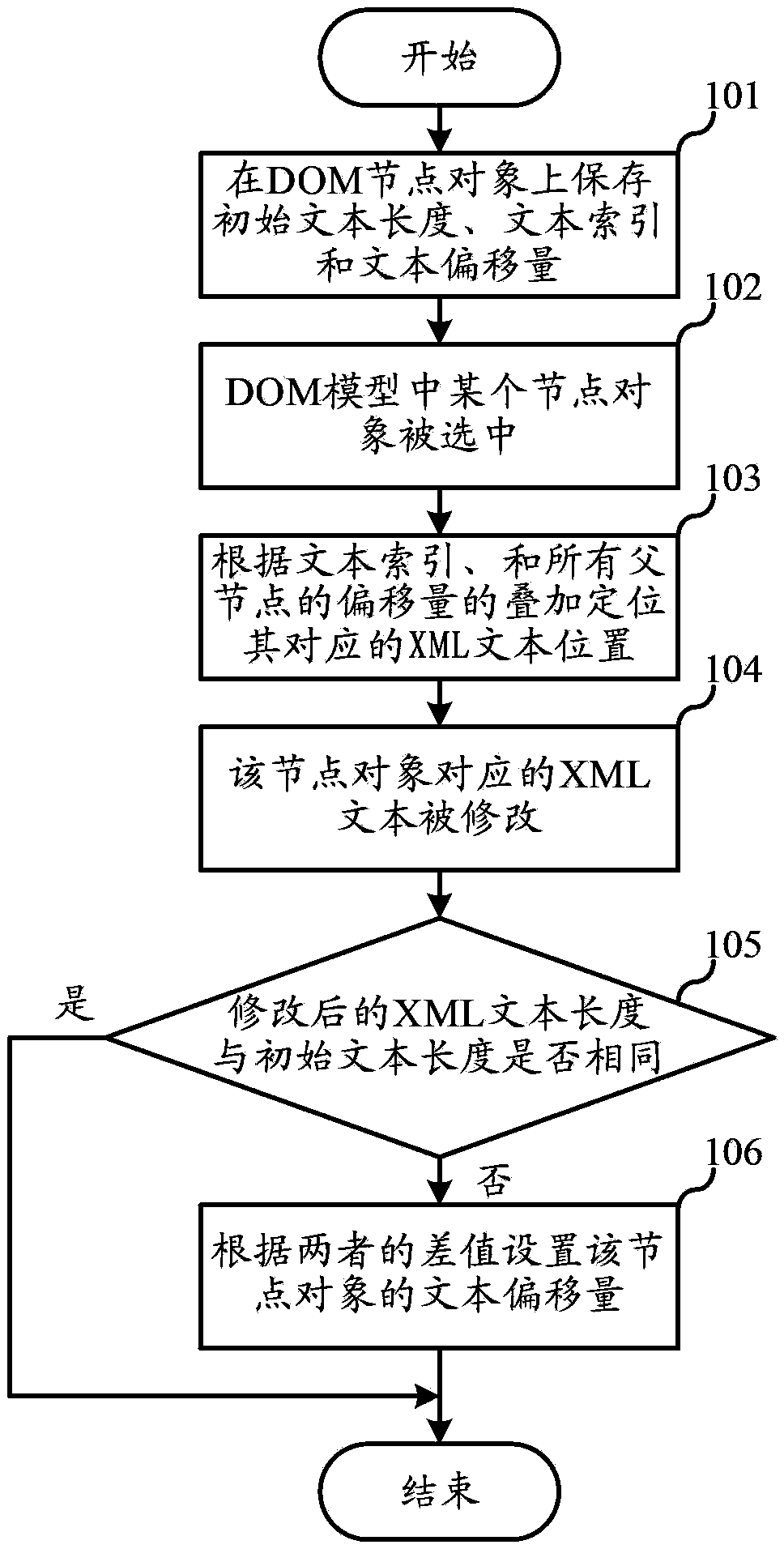

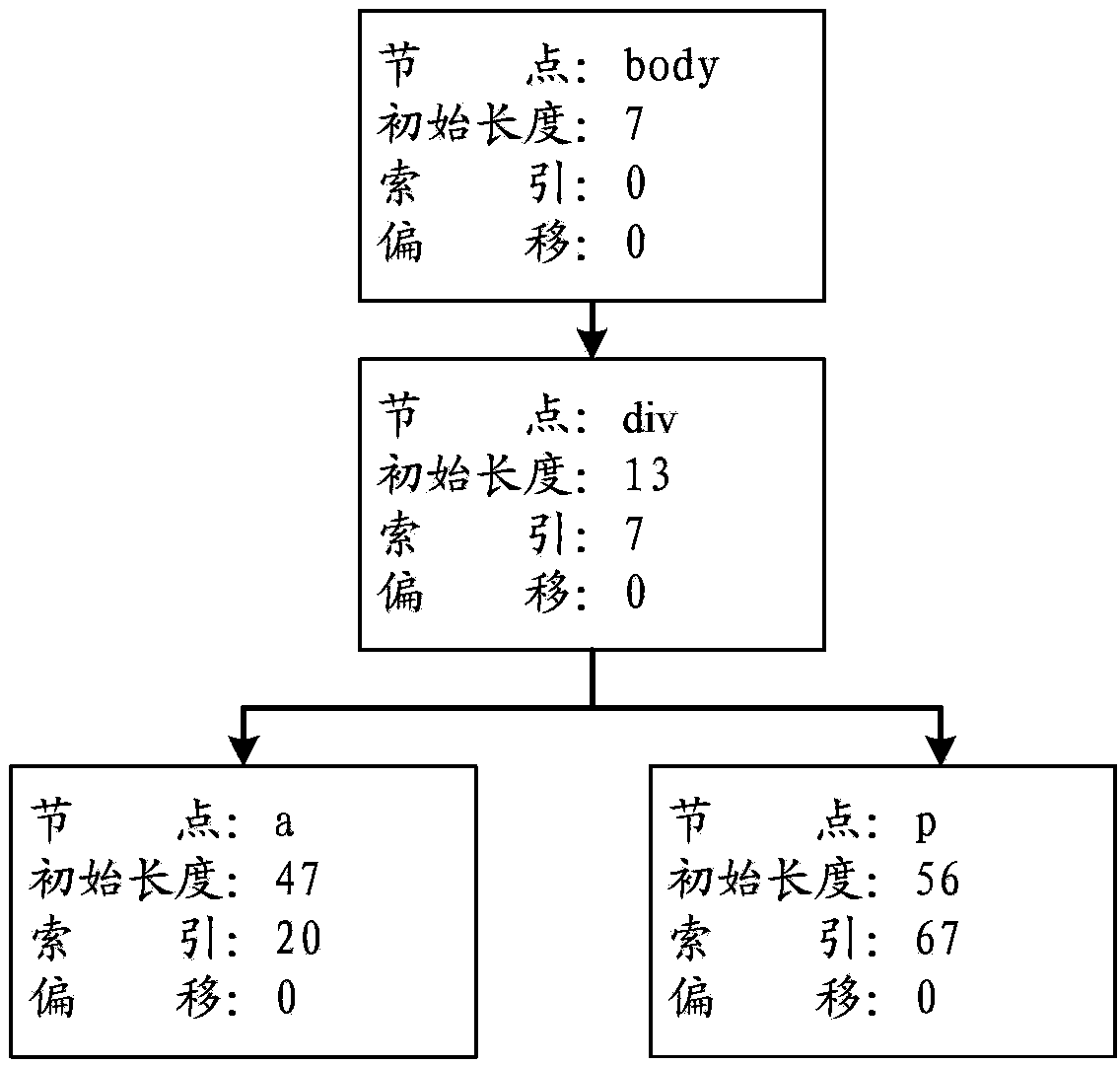

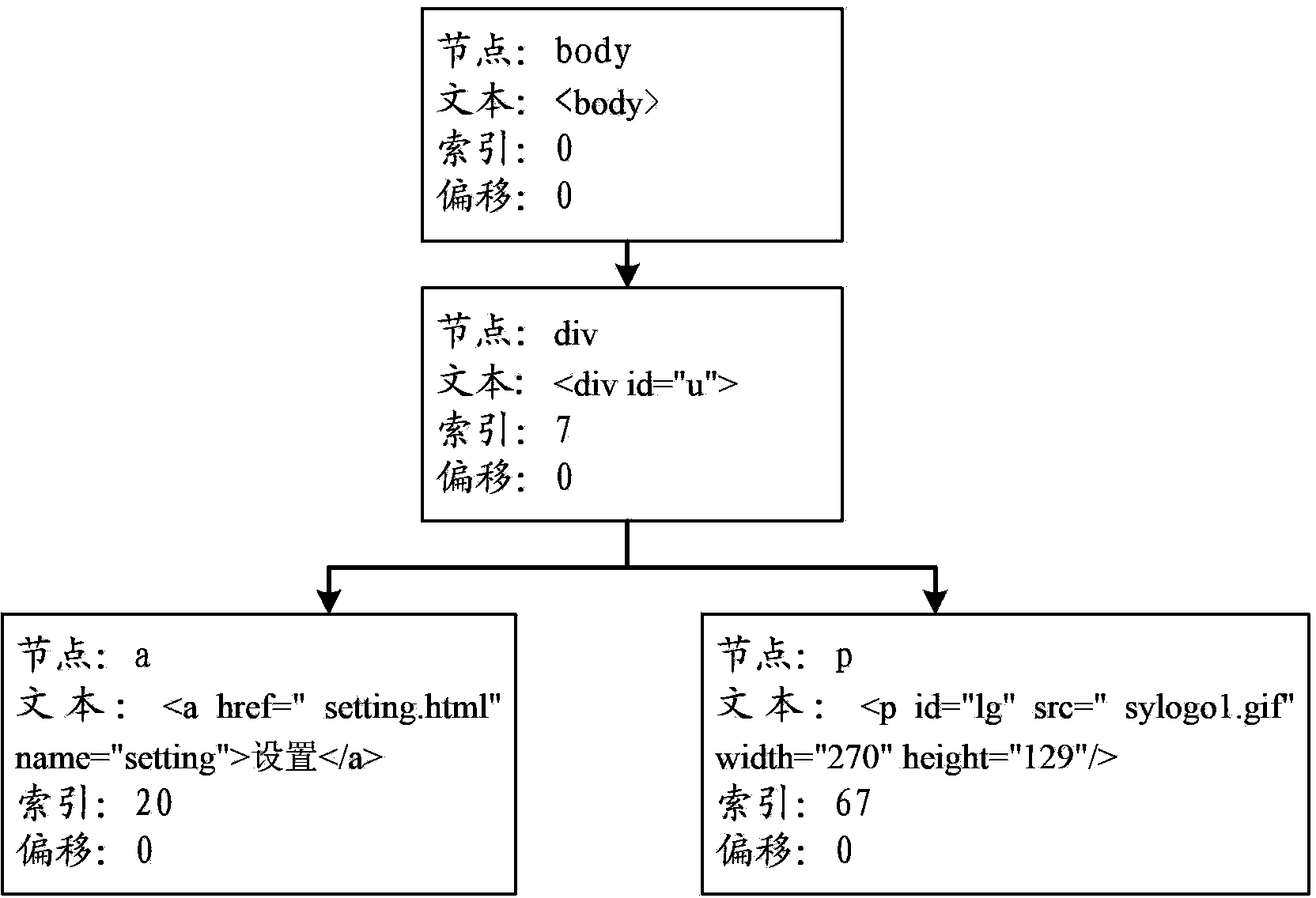

XML (X Exrensible Markup Language) text positioning method based on DOM (Document Object Model) model

InactiveCN103914437AImprove editing speedQuick mapSpecial data processing applicationsTheoretical computer scienceDocument Object Model

The invention discloses an XML (X Exrensible Markup Language) text positioning method based on a DOM (Document Object Model) model. The method comprises the following steps: storing the text index and text offset of a node object on the node object of the DOM model, wherein the text index is the initial position of the XML text of the node object in a whole XML text, and the text offset is a differential valve between the text length of the modified XML text of the node object and the initial text length; when the node object in the DOM model is selected, positioning an XML text position corresponding to the node object according to the overlapping of the text offsets of all male nodes of the node object and the text index of the node object. Therefore, the XML text position corresponding to the DOM model node object can be quickly positioned without the comparison of text contents.

Owner:ASAT CHINA TECH

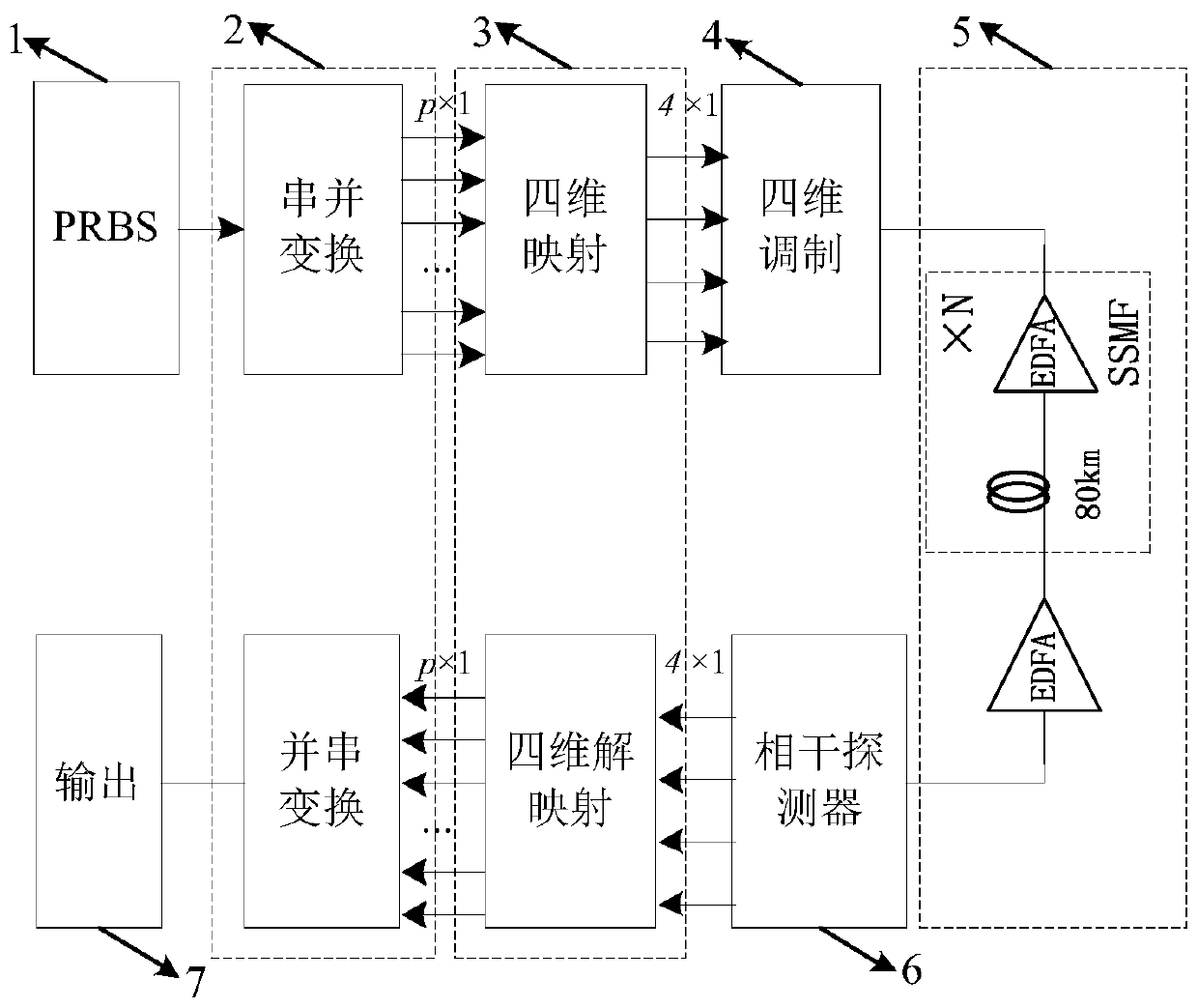

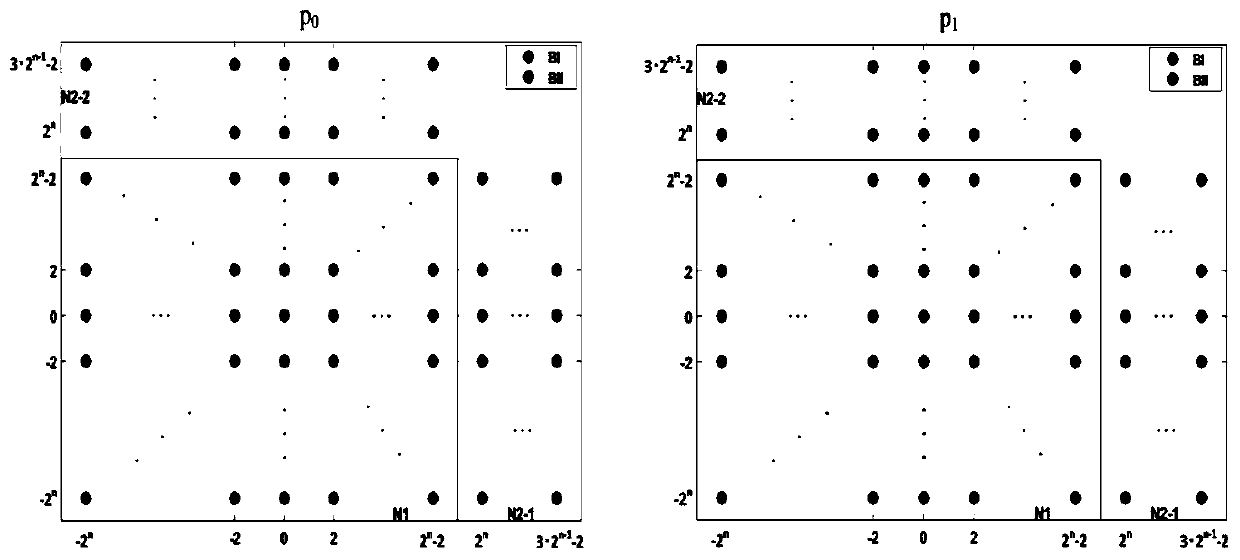

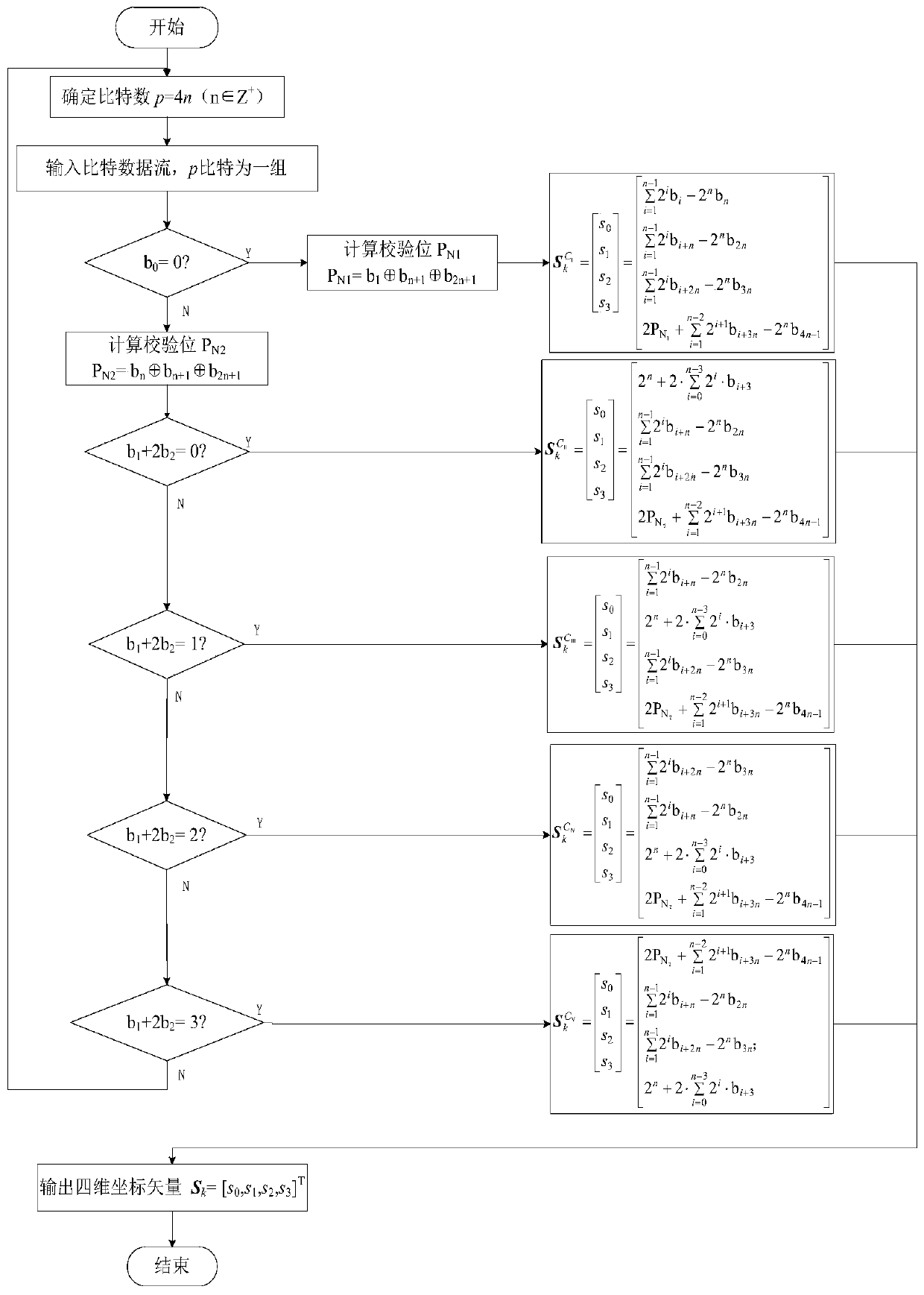

High-dimensional modulation mapping method based on subset selection

ActiveCN110113107AQuick mapImprove bit error performanceElectromagnetic transmissionMultiple carrier systemsRound complexityTheoretical computer science

The invention discloses a high-dimensional modulation mapping method based on subset selection, and belongs to the technical field of communication. The method comprises the following steps of firstly, taking a minimum Euclidean distance between constellation points as a constraint condition, and obtaining K high-dimensional constellation subsets with hypercube structures from a two-dimensional constellation set in a partition and diversity constellation point combination manner; then, dividing the bit tags obtained by serial-parallel conversion of the bit data flow into two parts, wherein onepart of the bit tags is used for the subset selection of a high-dimensional constellation point set, and the other part of the bit tags finally obtains a high-dimensional target coordinate vector through the arithmetic operation between the binary bits. According to the present invention, a subset selection method is adopted to realize a rapid high-dimensional mapping technology, the mapping storage space of the method is independent of the scale of the constellation point set, so that the method has the characteristics of low operation complexity and excellent system error code performance,and a better high-dimensional modulation mapping effect can be achieved.

Owner:JILIN UNIV

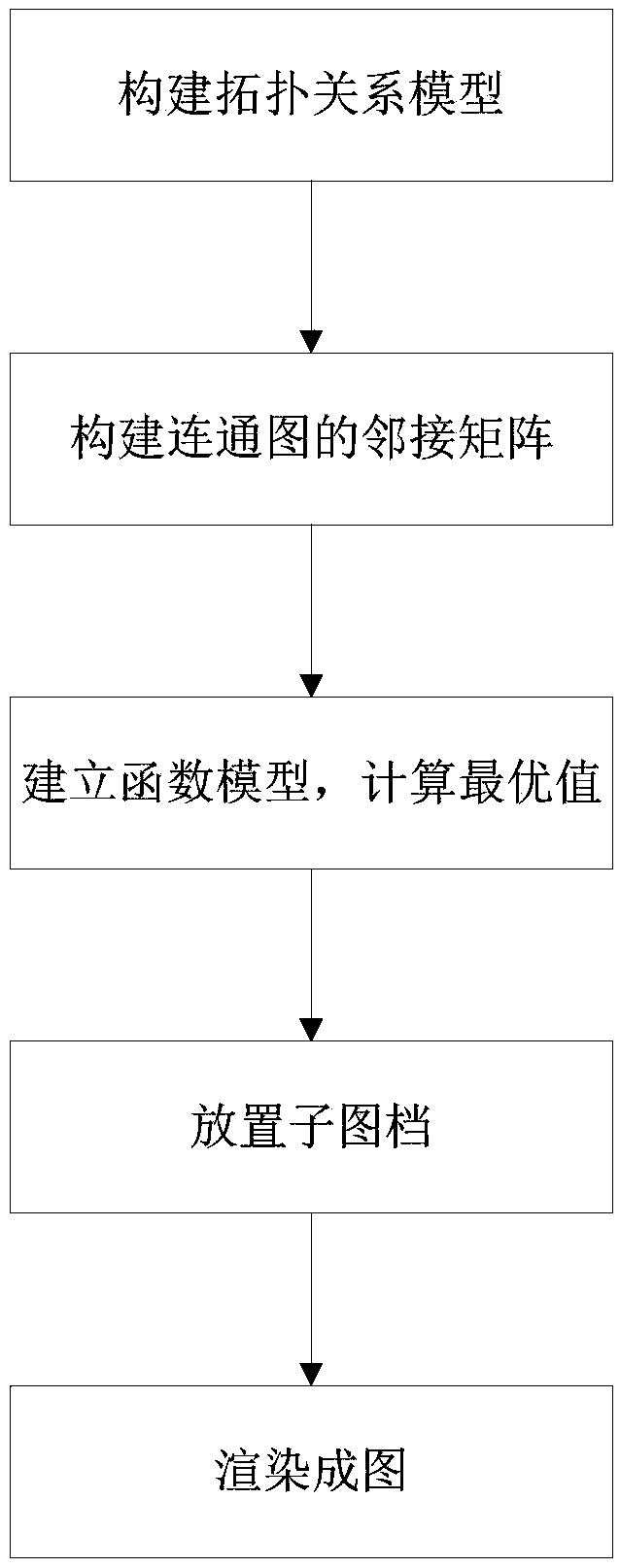

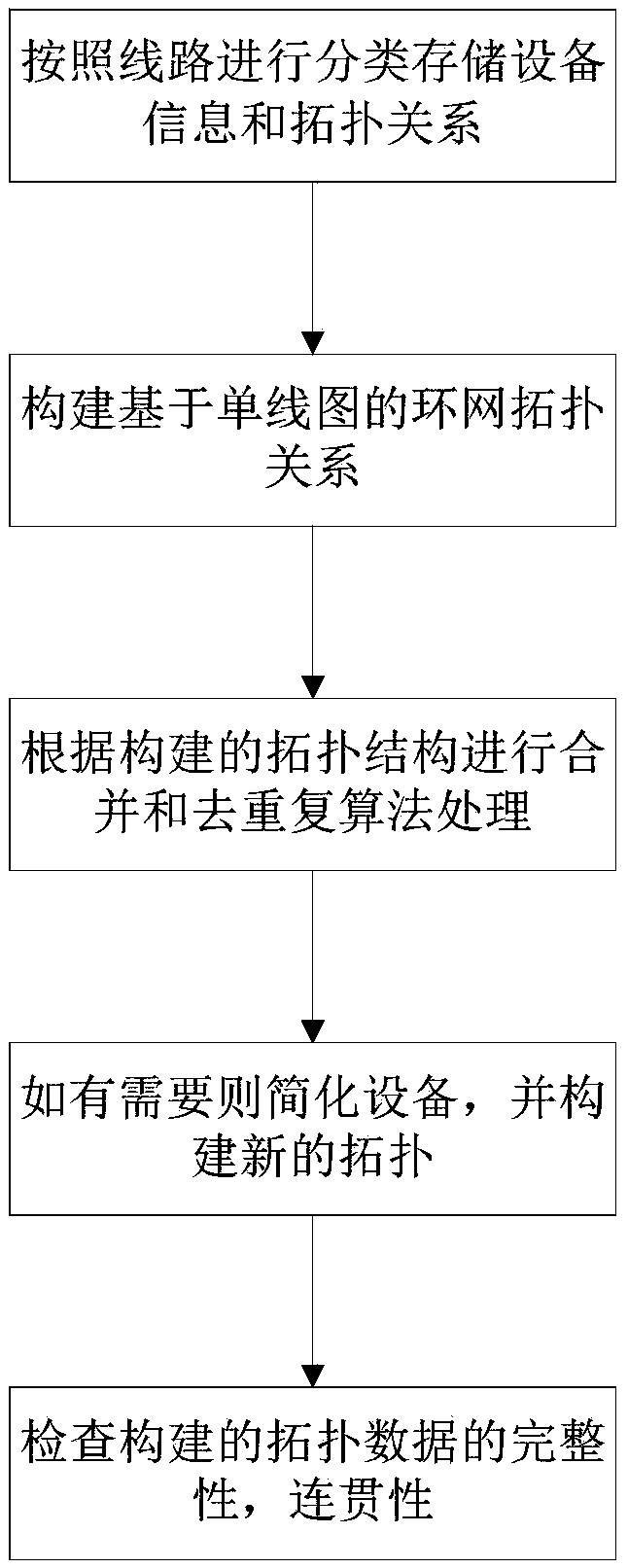

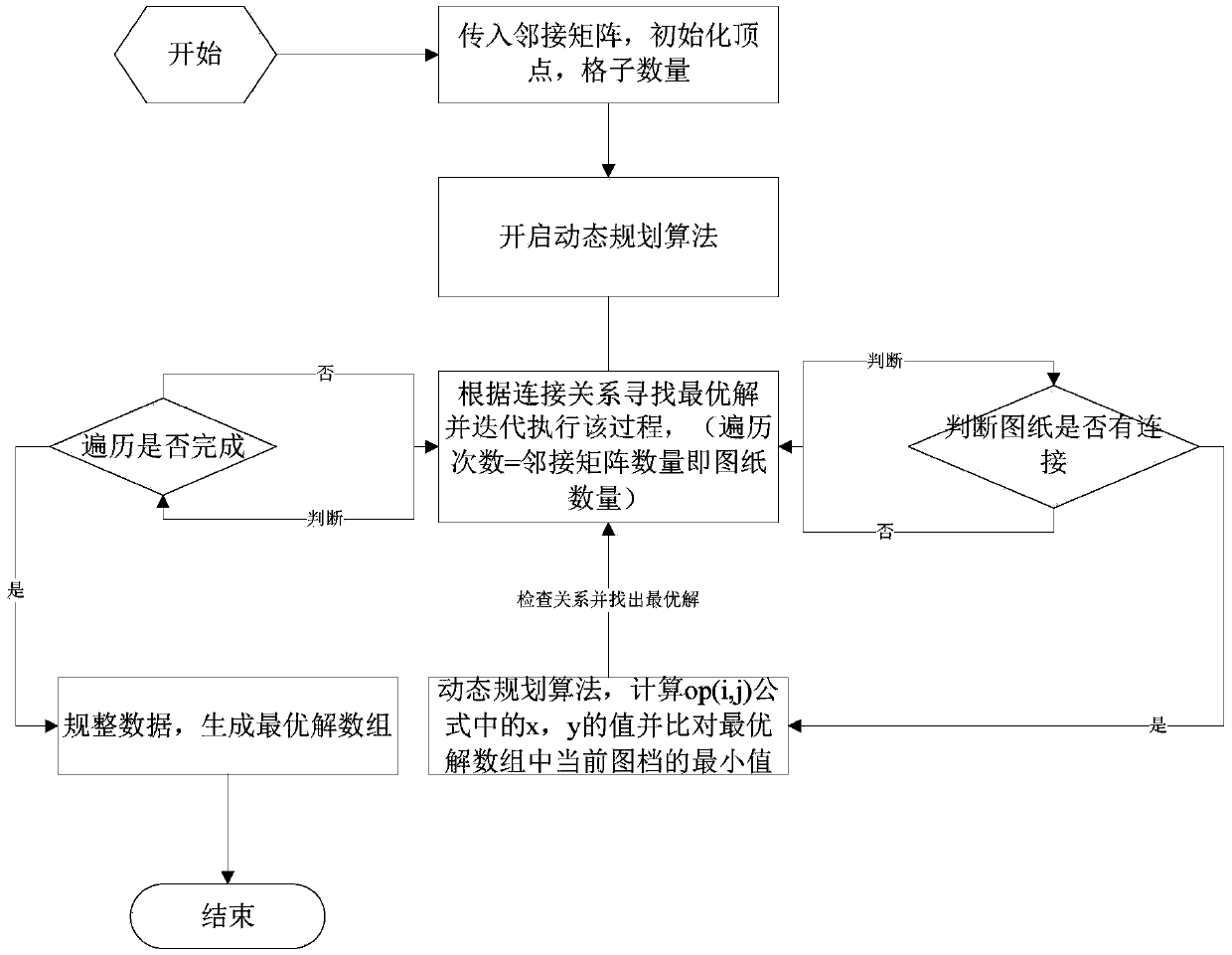

Dynamic programming algorithm-based grid theme graph layout method

ActiveCN105373661AQuick mapPerfect pictureSpecial data processing applicationsRelational modelElectric power system

The invention discloses a dynamic programming algorithm-based grid theme graph layout method. The dynamic programming algorithm-based grid theme graph layout method is characterized by comprising the following steps: (1) building a single-line graph-based ring network topological relation model according to spatial data of a power system; (2) building a connected graph formed by N vertexes and an N*N adjacent matrix according to the built topological relation model and the number N of sub-graph files; (3) building a function model, and calculating an optimal value according to a dynamic programming algorithm until the sub-graph files are completely traversed; (4) distributing the sub-graph files; and (5) rendering the sub-graph files into a graph. A layout method which is best for a power grid is extended and expanded on the basis of the dynamic programming algorithm; the graph can be quickly and perfectly formed; and the problem of the rendering efficiency of a grid system under a large amount of data is solved.

Owner:JIANGSU ELECTRIC POWER COMPANY YANGZHOU POWER +2