Method for forming stress layer in stress memorization technique

A stress memory technology and stress layer technology, applied in the field of semiconductor manufacturing, can solve problems affecting the deposition of stress layers, uneven stress, unfavorable ion implantation process, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention and are not intended to limit the invention.

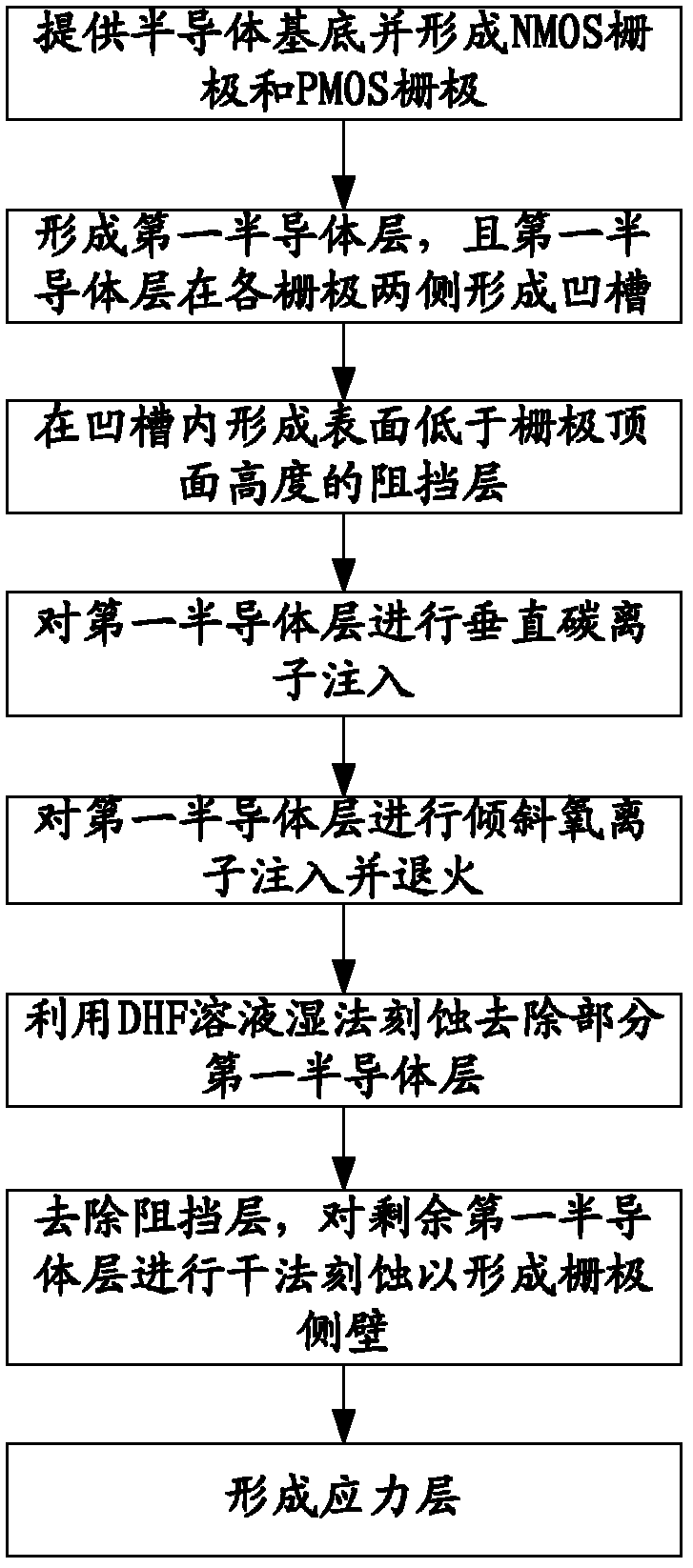

[0029] Such as figure 2 A method for forming a high-stress layer in a stress memory technology of the present invention shown, comprising steps:

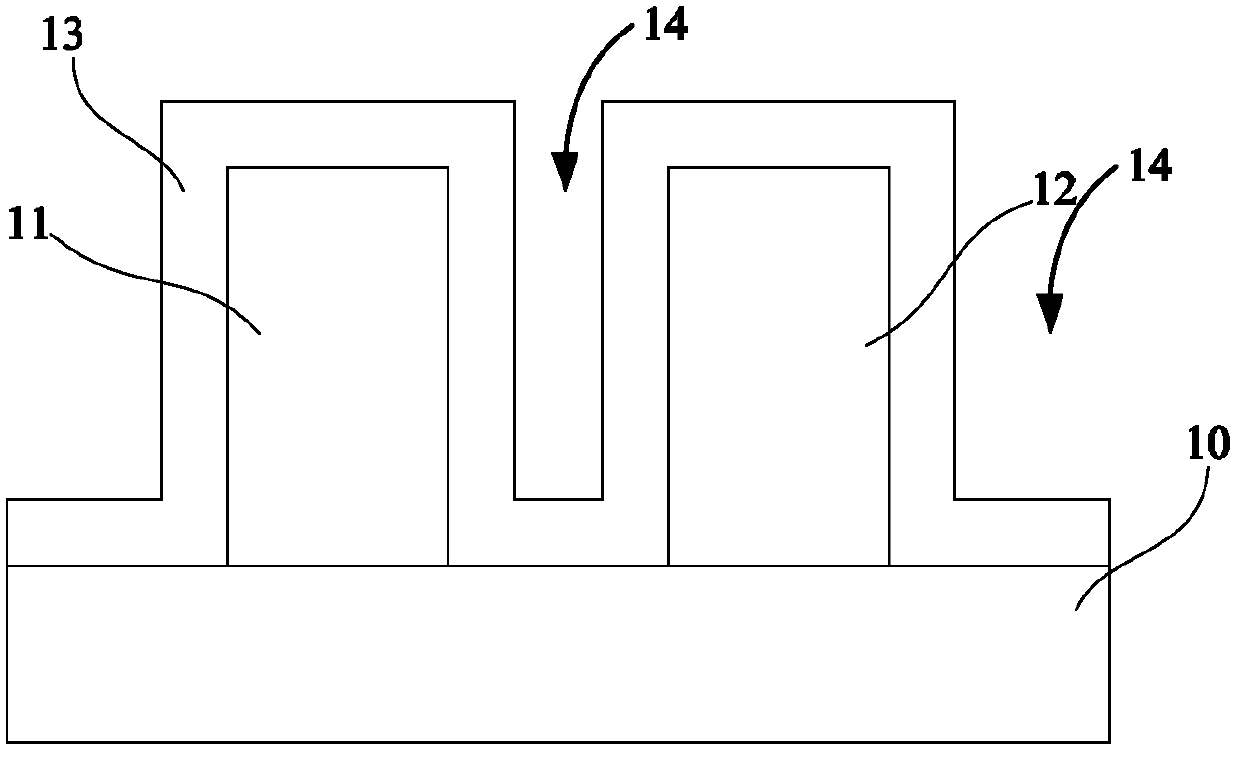

[0030] providing a semiconductor substrate having PMOS and NMOS regions;

[0031] forming a PMOS gate and an NMOS gate on the PMOS region and the NMOS region, respectively;

[0032] A first semiconductor layer is formed on the semiconductor substrate and the surface of the PMOS gate and the NMOS gate, and the first semiconductor layer forms grooves on both sides of each gate;

[0033] forming a barrier layer in the groove, the surface of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More