Layout modification method and system

A layout, modified technology, applied in the field of electronic design automation tools, can solve the problem of high IC cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The description of the exemplary embodiments is intended to be read in conjunction with the accompanying drawings, which are considered a part of this entire written description. During description, words such as "lower", "upper", "horizontal", "vertical", "above", "beneath", "upward" , "downward", "top" and "bottom" and their derivatives (for example, "horizontally", "downwardly", "upwardly", etc.) should be understood to refer to the described or the orientation shown in the drawings. These spatially relative positional terms are for convenience of description and do not require that the device be constructed or operated in a particular orientation.

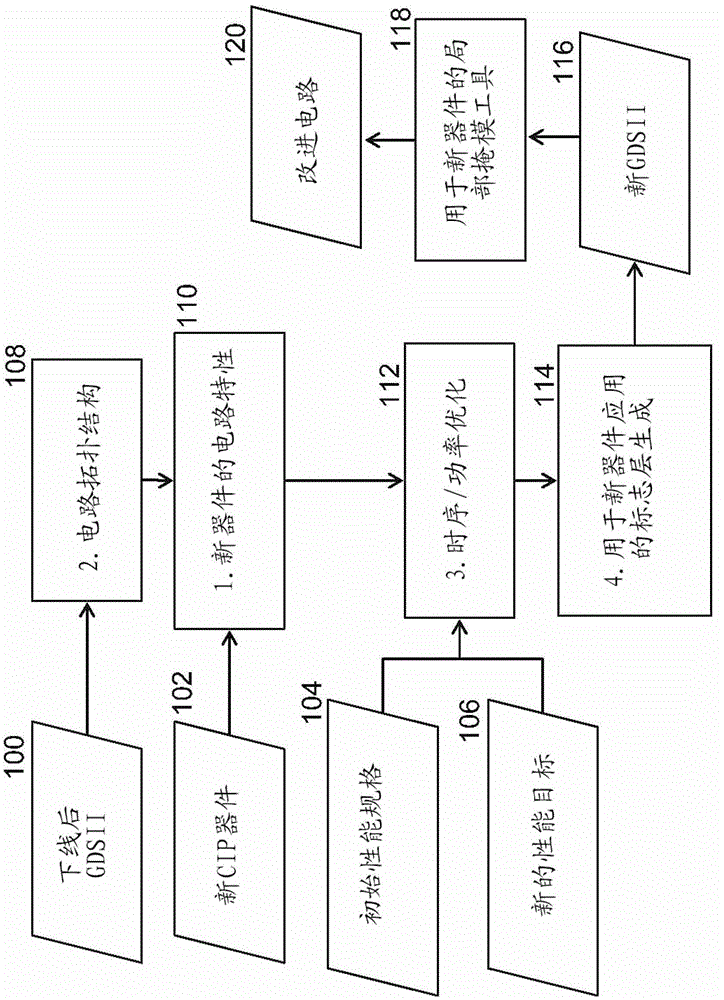

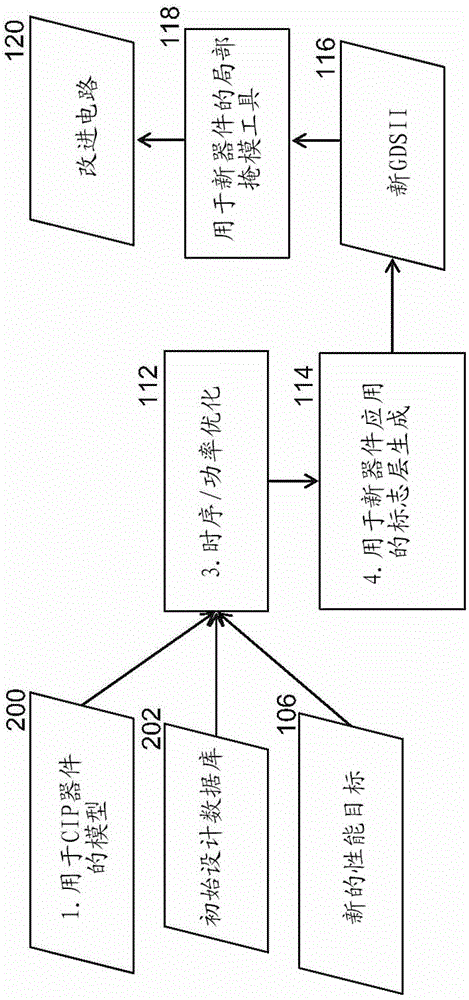

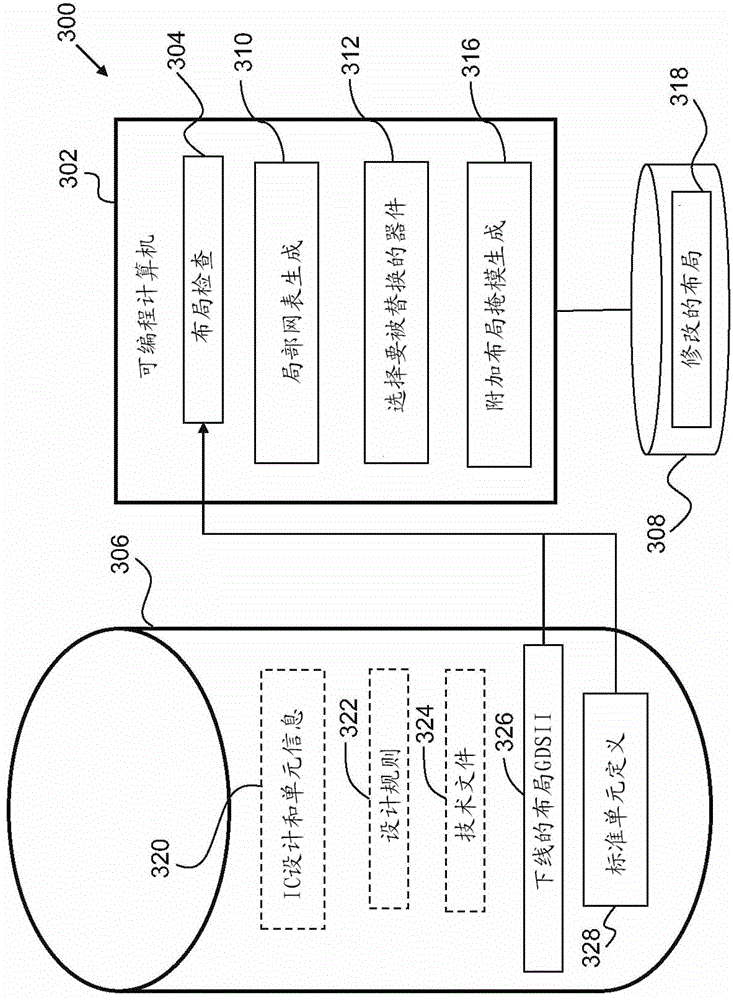

[0038] Methods and systems for modifying IC designs are described below. These methods and systems are suitable for use after design is complete (ie, after offline). Using these techniques, the completed design can be modified to take advantage of the same technology node cell design by adding one or more photomasks w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More