SOC (system on chip) and design method for same

A system-level chip and computing unit technology, applied in the SOC field, can solve problems such as serious losses, high R&D costs or authorization costs, and delays in product launch time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

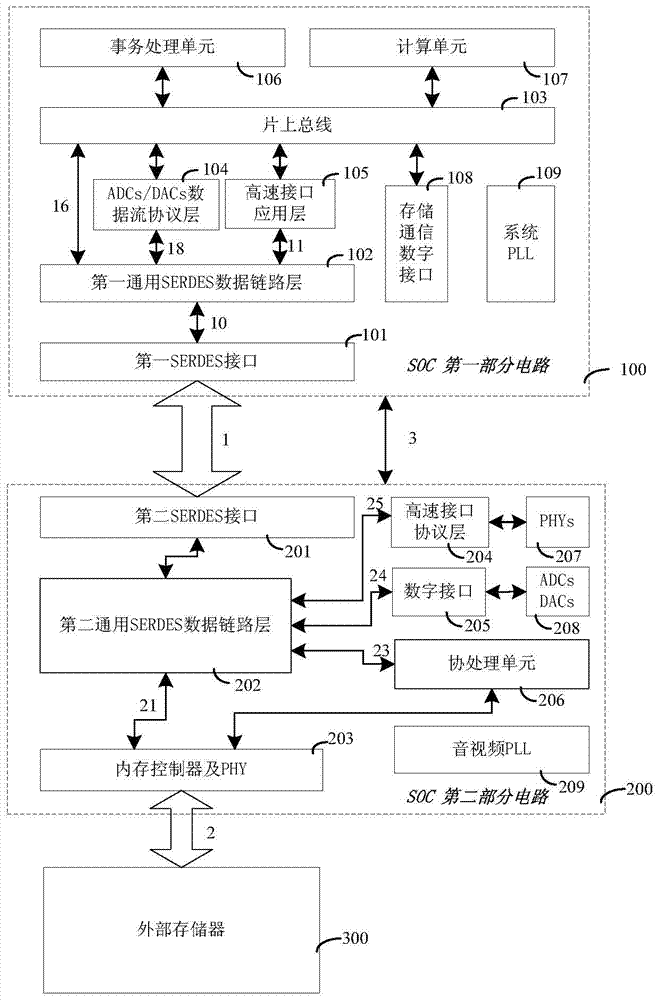

[0089] refer to figure 1 , the system-on-a-chip (or system-on-chip device) of the first embodiment is divided into two parts: the first part of the circuit 100 and the second part of the circuit 200, the two are arranged in different layouts, bare chips, chips or programmable devices and are connected to each other through the SERDES interface, and the data interaction between the two follows the relevant SERDES technical specifications. Among them, the first part of the circuit 100 mainly includes a general digital part, such as one or more SOC digital parts; the second part of the circuit 200 mainly includes a SOC high-speed interface and an analog part, such as one or more SOC analog parts.

[0090] As a preferred embodiment, the first part of the circuit 100 and the second part of the circuit 200 share the same external memory 300 . The external memory 300 can be various suitable volatile memories, such as DDR1 / 2 / 3, LPDDR and so on.

[0091] Further, the first part of th...

no. 2 example

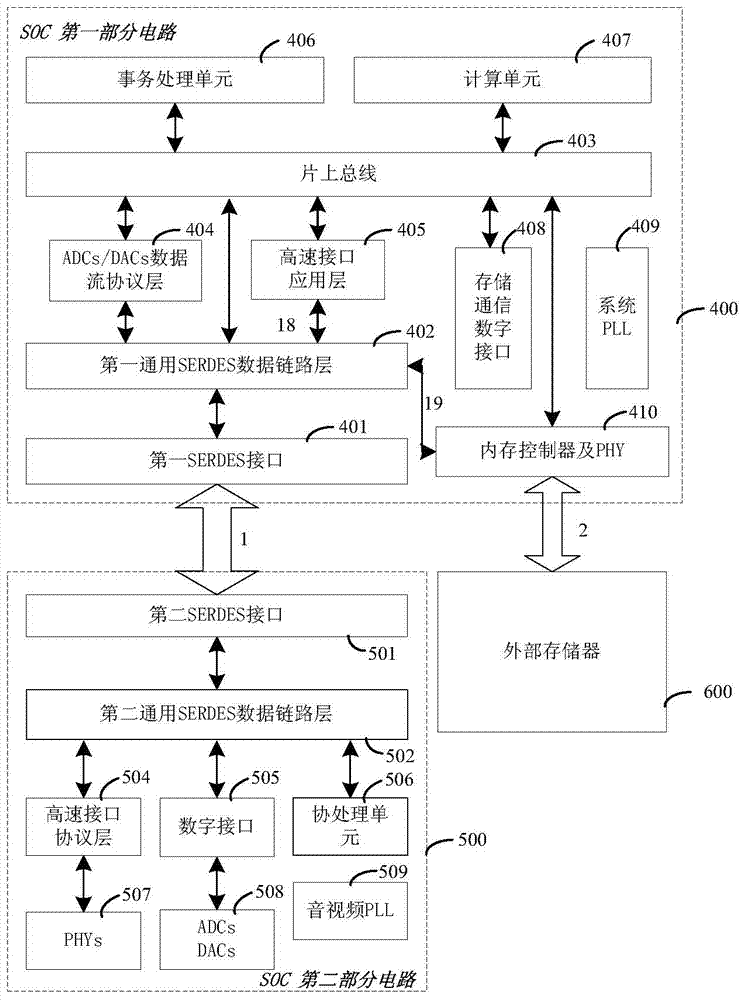

[0115] refer to figure 2 , figure 2 Shows the structural block diagram of the system-on-a-chip or device of the second embodiment, similar to the first embodiment, it is divided into two parts: the first part of the circuit 400 and the second part of the circuit 500, the two are arranged in different layouts, On the bare chip, chip or programmable device, and connected to each other through the SERDES interface, the data interaction between the two follows the relevant SERDES technical specifications. Among them, the first part of the circuit 400 mainly includes a general digital part, such as one or more SOC digital parts; the second part of the circuit 500 mainly includes a SOC high-speed interface and an analog part, such as one or more SOC analog parts.

[0116] As a preferred embodiment, the first part of the circuit 400 and the second part of the circuit 500 share the same external memory 600 . The external memory 600 can be various volatile memories, such as DDR1 / 2 / ...

no. 3 example

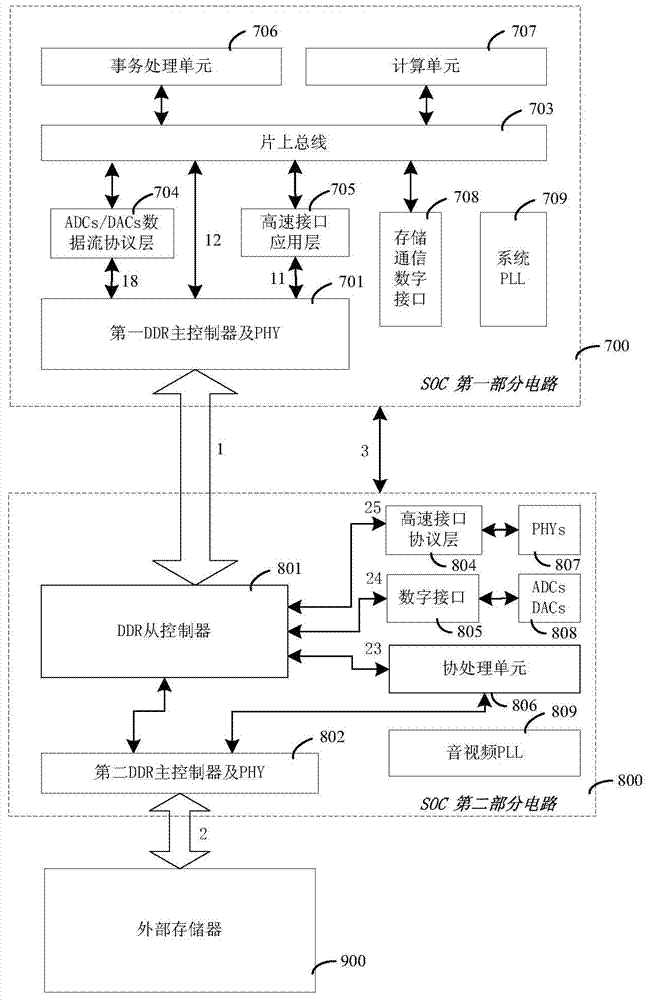

[0125] refer to image 3 , image 3Shows a structural block diagram of the system-on-a-chip or device of the third embodiment, similar to the first and second embodiments, it is divided into two parts: a first part of the circuit 700 and a second part of the circuit 800, the two are arranged in different On the layout, bare chip, chip or programmable device, and are connected to each other through the DDR interface, the data interaction between the two follows the relevant DDR technical specifications. Among them, the first part of the circuit 700 mainly includes a general digital part, such as one or more SOC digital parts; the second part of the circuit 800 mainly includes a SOC high-speed interface and an analog part, such as one or more SOC analog parts.

[0126] As a preferred embodiment, the first part of the circuit 700 and the second part of the circuit 800 share the same external memory 900 . The external memory 900 can be various volatile memories, such as DDR1 / 2 / 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More