Packaging test method

A technology for packaging testing and packaging components, which is applied in semiconductor/solid-state device testing/measurement, electrical components, semiconductor/solid-state device manufacturing, etc. Reduce costs, increase flexibility of use, and simplify processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

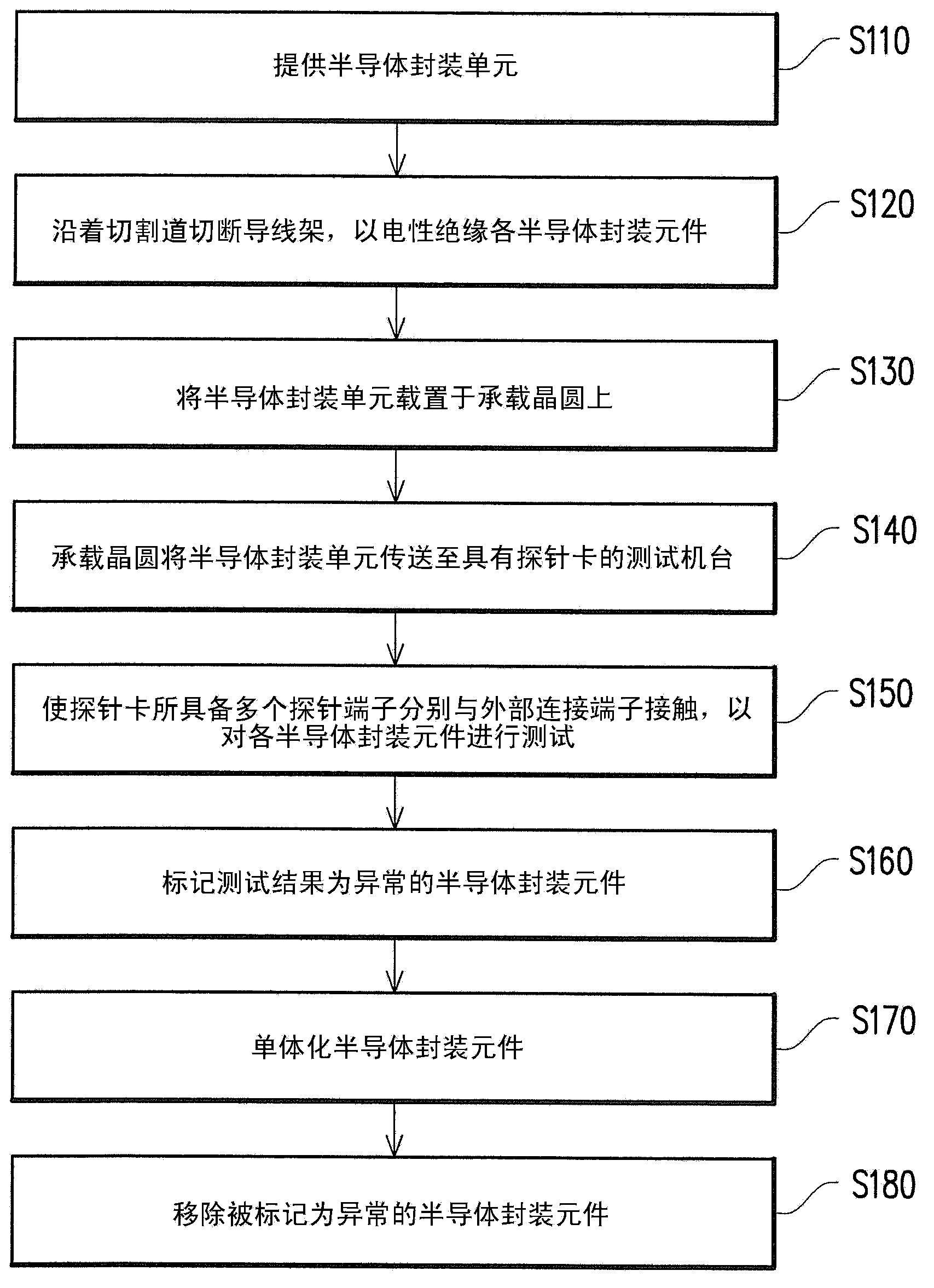

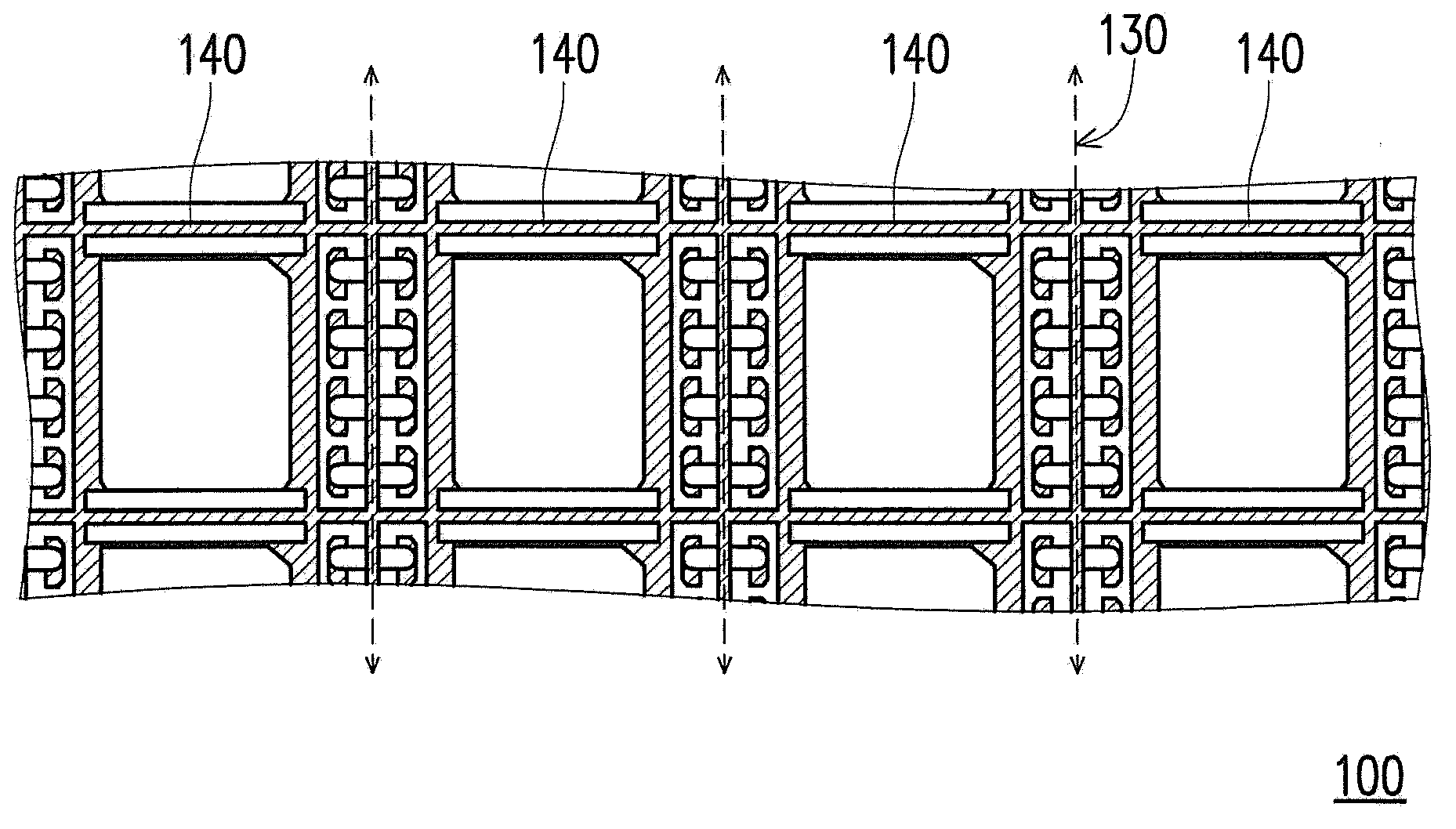

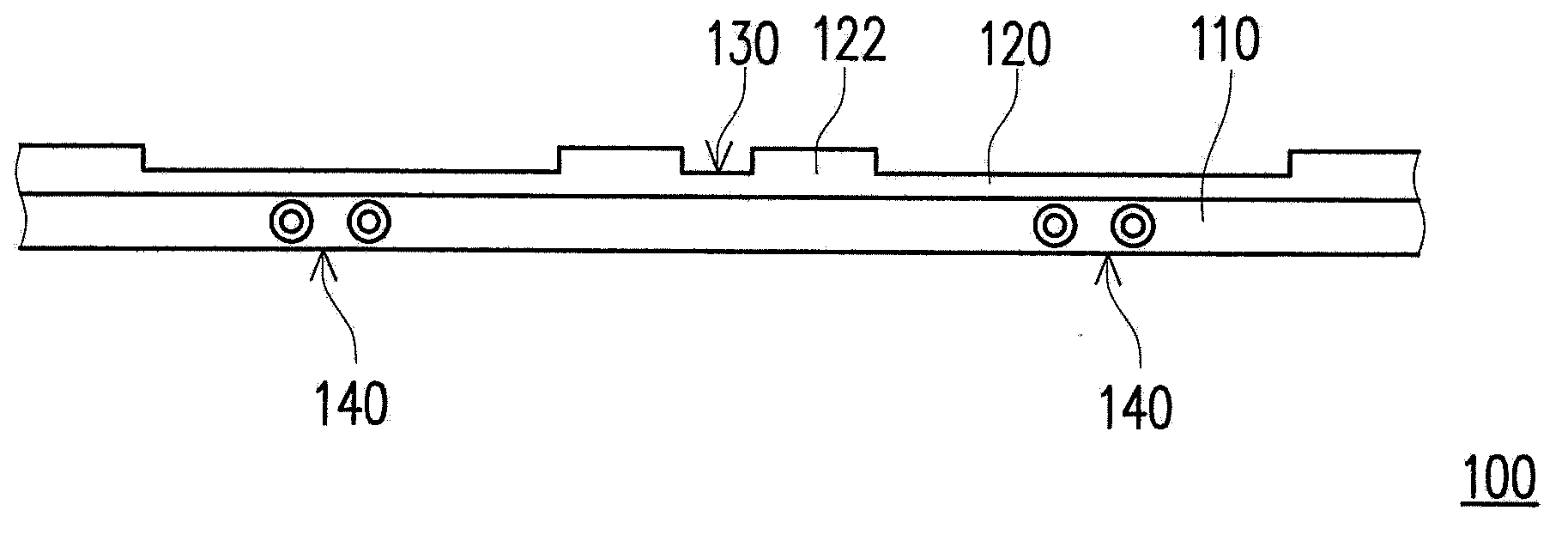

[0034] figure 1 It is a schematic flowchart of a packaging and testing method according to an embodiment of the present invention. figure 2 It is a partial schematic diagram of a semiconductor package unit according to an embodiment of the present invention. image 3 is a schematic cross-sectional view of a semiconductor package unit according to an embodiment of the present invention. Please also refer to figure 1 , figure 2 and image 3 , the packaging and testing method of this embodiment is suitable for performing a yield test on a semiconductor packaging unit 100, and the packaging and testing method includes the following steps: first, step S110 is performed, and the following steps are provided: figure 2 and image 3 A semiconductor package unit 100 is shown, which includes an encapsulant 110 , a lead frame 120 and a plurality of dicing lines 130 . The dicing line 130 defines a plurality of semiconductor package elements 140 on the semiconductor package unit 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com