Sequential equivalent sampling circuit and method based on delay signals

A technology of equivalent sampling and delaying signals, which is applied in the direction of logic circuit coupling/interface, logic circuit connection/interface layout, electrical components, etc. using field effect transistors, and can solve the problem of not taking into account the minimum delay step of fine delay at the same time and total delay, small delay step size, long total delay, etc., to achieve timing matching, reduce jitter, and expand total delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

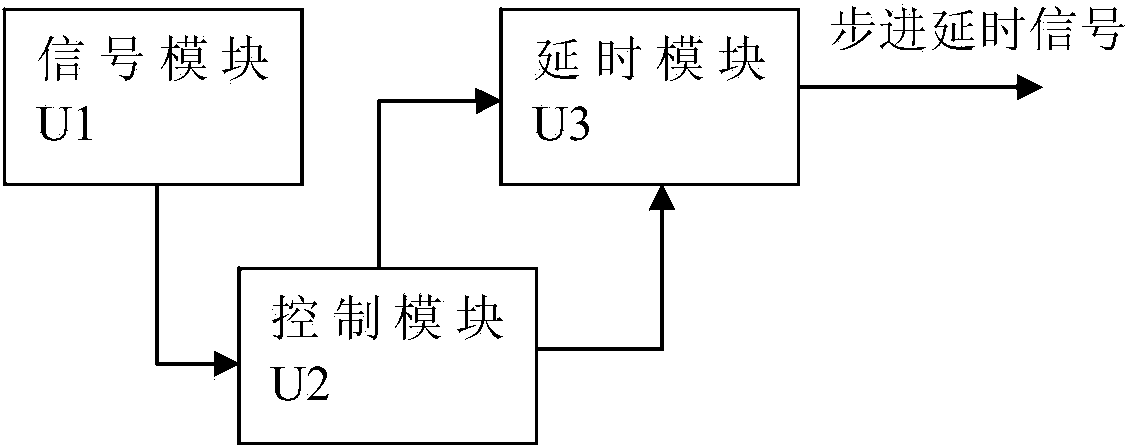

[0043] The invention is used to generate high-precision and large-scale step-delay signals, and the step-delay signal generation circuit and method are widely used in sequential equivalent sampling systems. see figure 1 , the generating circuit includes a signal module U1 for generating signals, a control module U2 for clock debounce and delay adjustment, and a delay module U3.

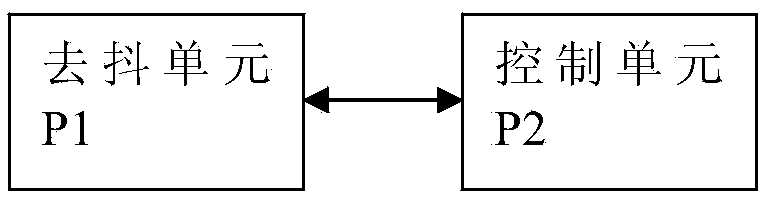

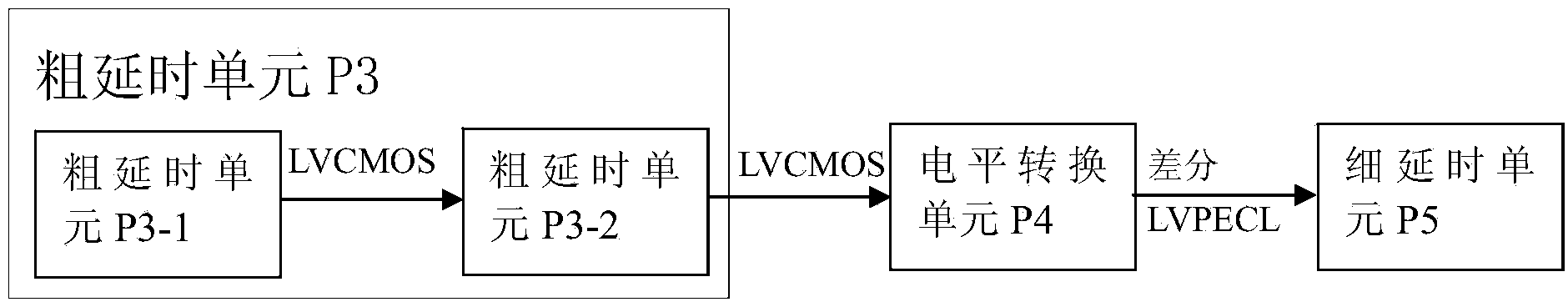

[0044] The control module U2 includes a debounce unit P1 and a control unit P2, see figure 2 . The control module U2 adopts the EP3C16Q240 in Altera's Cyclone III series FPGA. The debounce unit P1 uses the PLL IP core inside the FPGA to accurately divide and multiply the input signal, reduce the output jitter, and improve the signal quality. The main functions of the control unit P2 are: to adjust and control the delay step length of the coarse delay unit P3 and the fine delay unit P5 through the logic function of the FPGA, to realize the output of the delay adjustment signal through the internal l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More