Hybrid bonding mechanisms for semiconductor wafers

A hybrid bonding, semiconductor technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The making and using of embodiments of the invention are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

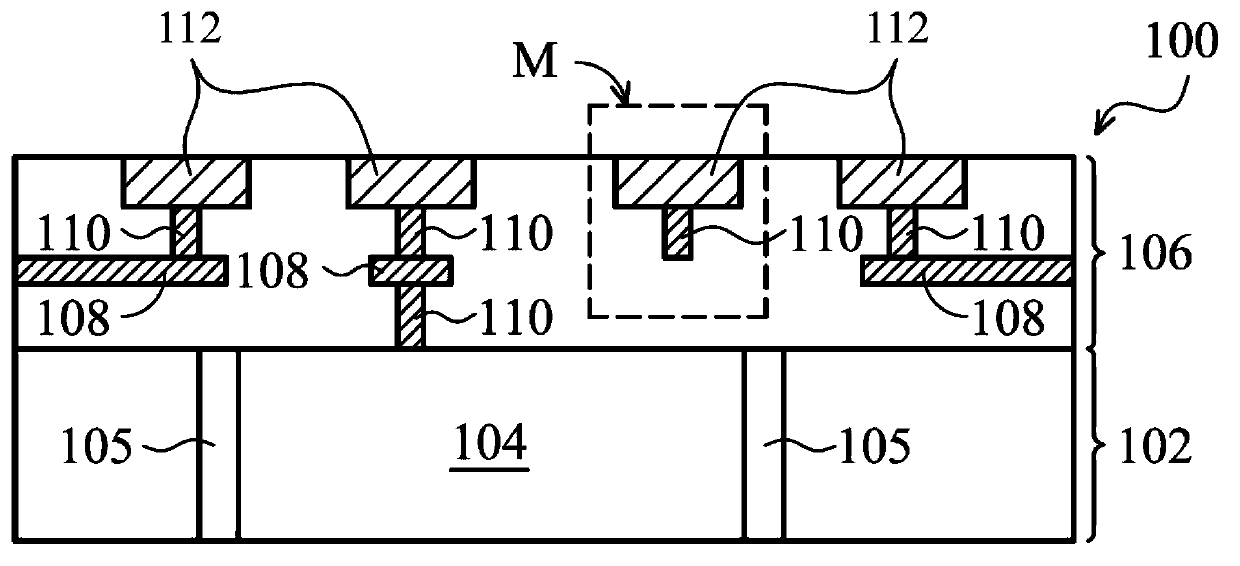

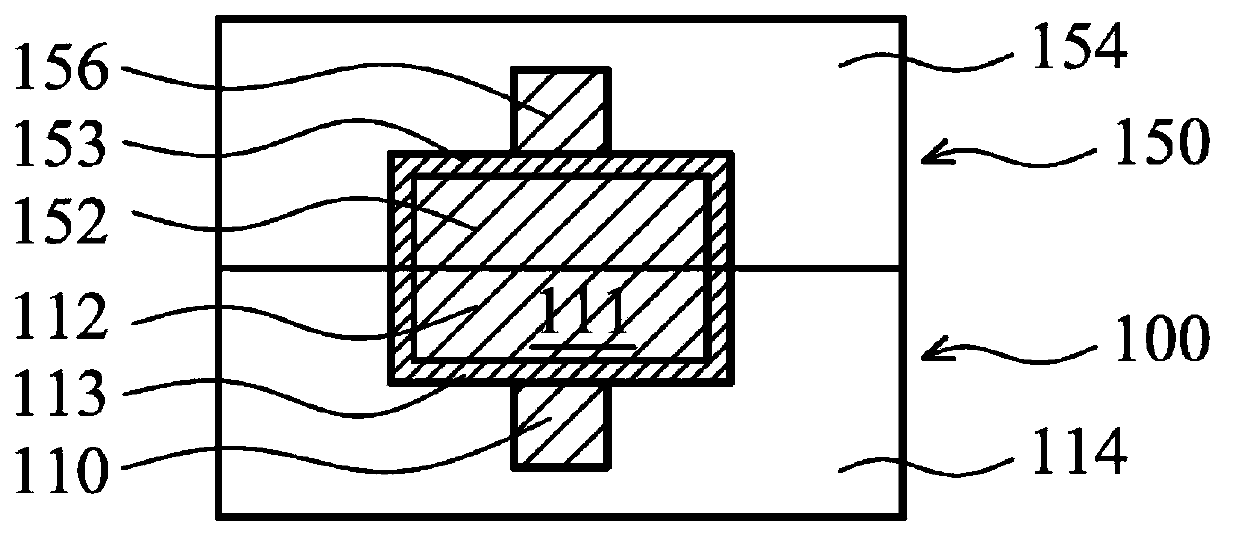

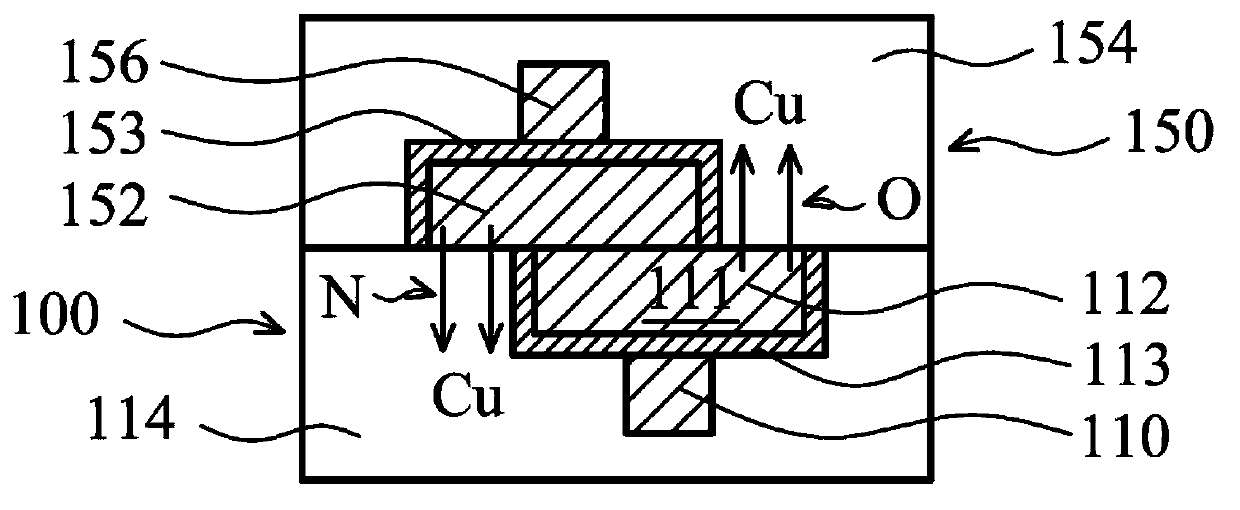

[0041]Hybrid bonding is a type of bonding method used for 3DIC in which two semiconductor wafers are bonded together using a hybrid bonding technique. Some methods and structures for 3DICs formed by hybrid bonding are described in U.S. Serial No. 13 / 488,745, entitled "Three Dimensional Integrated Circuit Structures and Hybrid Bonding Methods for Semiconductor Wafers," filed June 5, 2012 (Attorney Docket No. TSM3012-0241) and filed July 2012. US Serial No. 13 / 542,507, filed on the 5th, entitled "Hybrid Bonding Systems and Methods for Semiconductor Wafers" (Attorney Docket ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More