FPGA (Field Programmable Gate Array) based serial interface and PWM (Pulse Width Modulation) combined application IP (Intellectual Property) core

A serial interface and serial port technology, which is applied in the field of FPGA-based serial interface and PWM combination application IP core, can solve the problems of FPGA resource waste, FPGA occupation, complex configuration, etc., and achieve simple configuration, resource reduction, and convenient operation Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

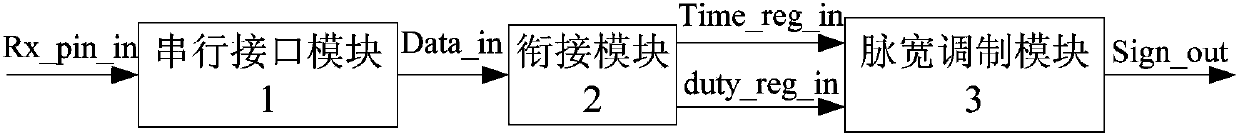

[0033] Such as figure 1 As shown, an FPGA-based serial interface and PWM combination application IP core (IntellectualProperty), including a serial interface module 1, a connecting module 2, and a pulse width modulation (PWM) module 3. Adhering to the top-down design method, complex functions are divided into simple functional modules, and finally encapsulated by IP cores to realize the development of IP cores.

[0034] 1) Serial interface module

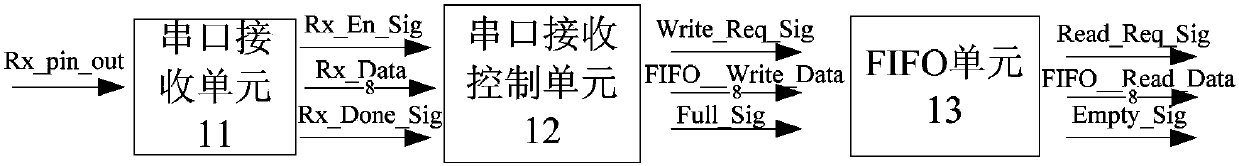

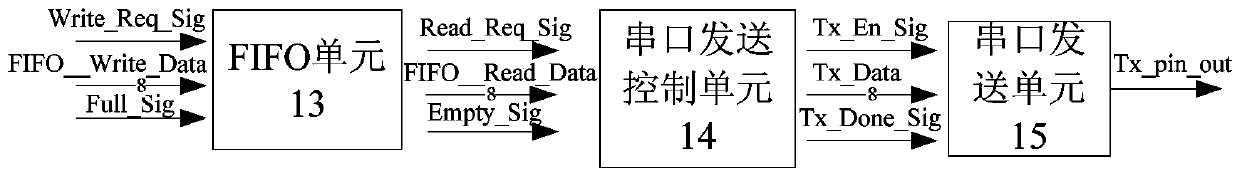

[0035] This module is designed and completed under the quartusII development environment. Such as Figure 2-Figure 3 As shown, the serial interface module 1 includes a serial port receiving unit 11, a serial port receiving control unit 12, a FIFO unit 13, a serial port sending control unit 14 and a serial port sending unit 15 connected in sequence; figure 2 As shown, the serial port receiving unit 11, the serial port receiving control unit 12 and the FIFO unit 13 form a serial port receiving submodule, and the serial port receiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More