Dislocation type electric leakage analysis method in grooved MOS device

A technology of MOS devices and analysis methods, applied in the direction of single semiconductor device testing, etc., can solve the problems of excluding dislocation defects, large limitations of TEM observation, affecting the overall analysis speed and accuracy, etc., to achieve comprehensive analysis of dislocation defects, Conducive to failure analysis and speed up the effect of process improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Such as Figure 4 Shown is the flow chart of the method of the embodiment of the present invention; the method for analyzing the dislocation type leakage in the trench MOS device of the embodiment of the present invention includes the following steps:

[0033] Step 1, using the EMMI analysis method to obtain defect positions in the trench MOS device chip.

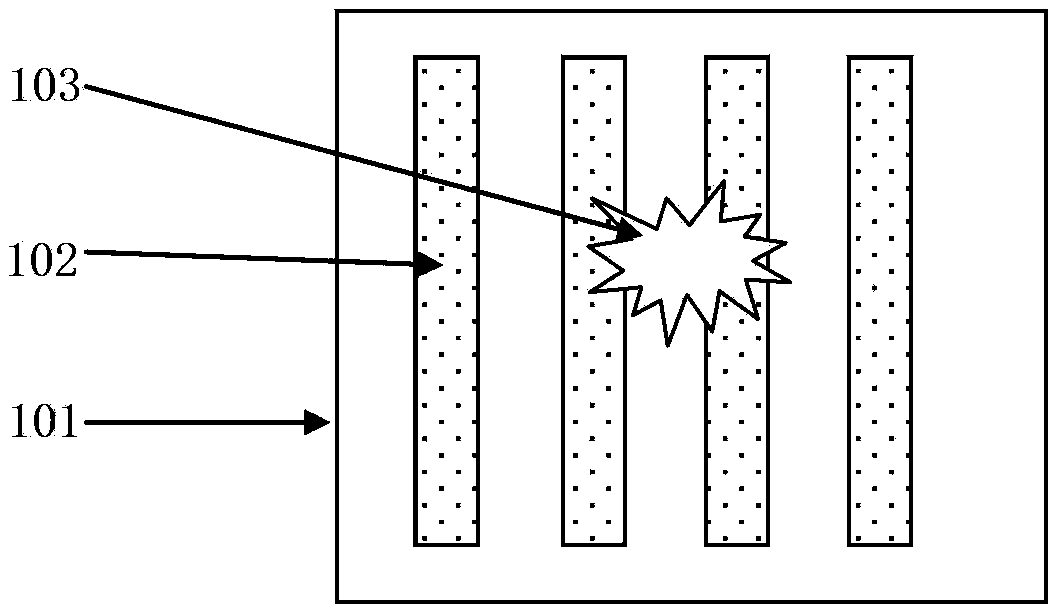

[0034] Such as Figure 5 As shown, it is a schematic diagram of EMMI positioning of failure feature points in the method of the embodiment of the present invention; a groove 2 is formed in a semiconductor substrate such as a silicon substrate 1, and a luminescent point 3 will be formed at the defect position during EMMI analysis. The defect position is revealed by using the luminous point 3 , that is, the defect position corresponds to the luminous point 3 .

[0035] The EMMI analysis conditions are controlled so that the diameter of the luminescent point 3 at the defect position is less than or equal to 1.5 micron...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com