PMOS transistor and manufacturing method thereof

A transistor and conductor technology, applied in the field of PMOS transistors and their preparation, can solve the problems of increasing static power consumption, device driving capability and speed reduction, large power consumption, etc., to avoid stress release, high carrier mobility, The effect of improving the working current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

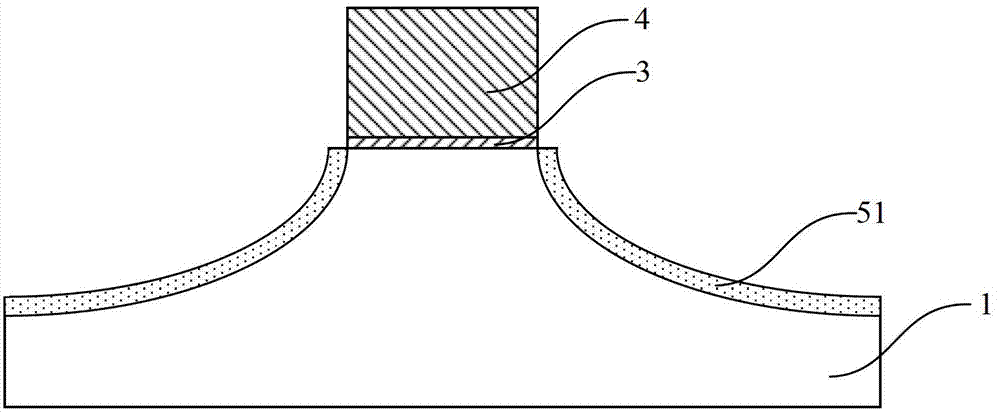

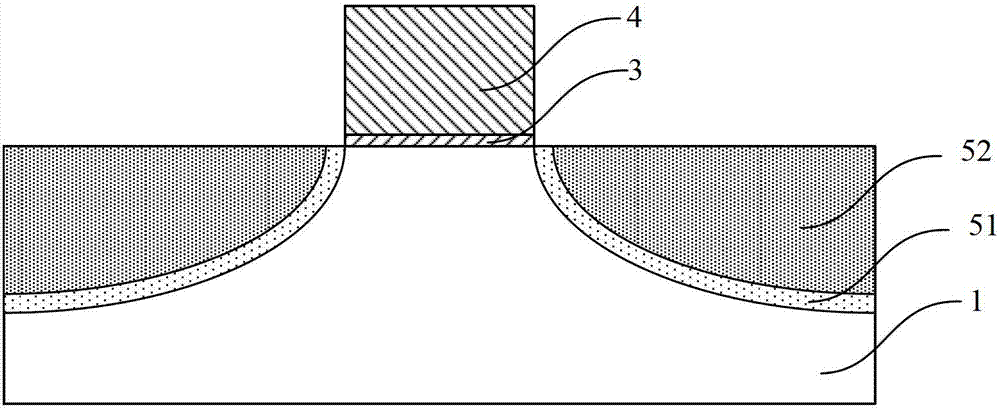

[0049] In view of this, the present invention provides a kind of preparation method of PMOS transistor, comprises the following steps at least: Provide a semiconductor substrate, form the source region, drain region and channel region on the top of the semiconductor substrate of prefabricated PMOS transistor active region, and the source region and the drain region exert compressive stress on the channel region; wherein, the specific steps of preparing the source region and the drain region are: 1) on the top of the substrate Pre-preparing the positions of the source region and the drain region respectively to form trenches; 2) In the trenches, first epitaxially grow the first stress adjustment layer, and then epitaxially grow the second stress adjustment layer, wherein the The lattice constants of the substrate, the first stress adjustment layer, and the second stress adjustment layer increase sequentially; 3) Repeat step 2) n times, where n is an integer and greater than or e...

Embodiment 1

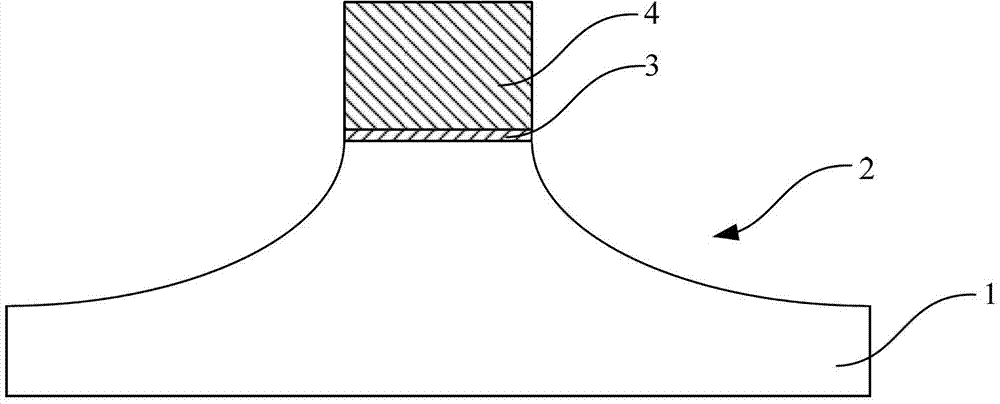

[0052] Such as Figure 1 to Figure 4 As shown, the present invention provides a preparation method of a PMOS transistor, the preparation method at least includes the following steps: providing a semiconductor substrate 1, forming a source region, a drain region and an The active region of the channel region, and the source region and the drain region exert compressive stress on the channel region; wherein, the specific steps of preparing the source region and the drain region are:

[0053] First perform step 1), such as figure 1 As shown, grooves 2 are respectively formed on the top of the substrate 1 where the source region and the drain region are pre-prepared, wherein the shape of the cross section of the groove 2 is not limited, and may be circular or sigma. etc., in this embodiment, the cross-sectional shape of the trench 2 is as figure 1 shown. It should be pointed out that, figure 1 Among them, between the trenches 2 and formed on the surface of the substrate 1 ar...

Embodiment 2

[0068] The technical solution of embodiment 2 is basically the same as that of embodiment 1, the only difference is that step 2) is repeated n times in step 3) of the preparation method in embodiment 1, and the value of n is 0; the PMOS transistor in embodiment 1 In the source region and the drain region, the value of m of the first stress adjustment layer and the second stress adjustment layer of m groups is 1; in the preparation method of the second embodiment, step 3) is to repeat step 2) n times, the value of n is an integer greater than 0; in the source region and the drain region of the PMOS transistor in the second embodiment, the value of m of the first stress adjustment layer and the second stress adjustment layer of m groups is greater than or equal to 2 , and m is an integer. The similarities between the second embodiment and the first embodiment are not described here one by one, and for the specific description of the similarities, please refer to the first embodi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More