A method for making ultra-thin odd-numbered-layer coreless board with low stress and low warpage

A low-warpage, odd-numbered layer technology, applied in multi-layer circuit manufacturing and other directions, can solve the problems of complex process, easy warpage, large warpage, etc., to simplify the preparation process, reduce mismatch, and reduce warpage. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

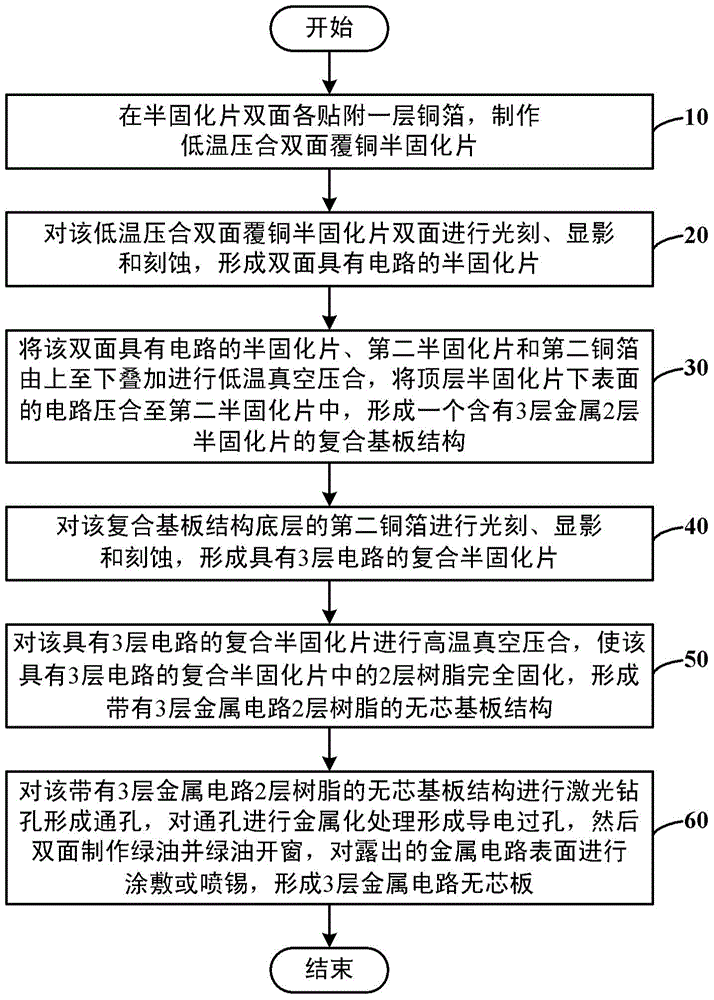

[0033] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

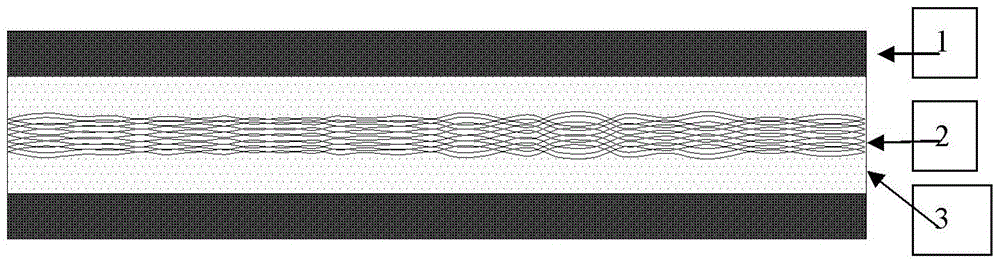

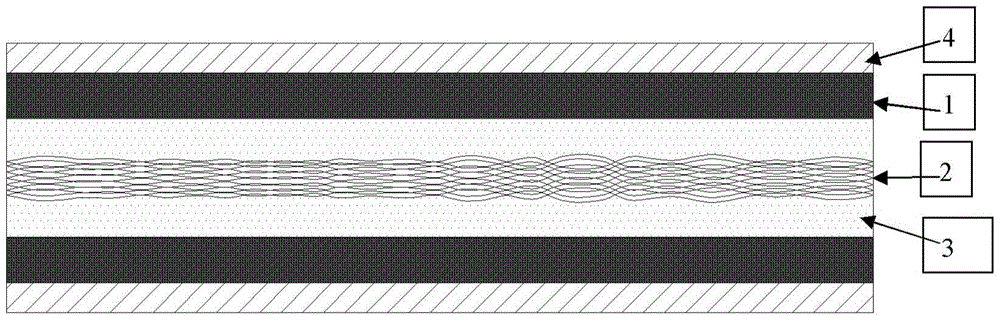

[0034] The present invention makes use of the characteristics of better resin fluidity of the prepreg at a certain low temperature, manufactures circuits on the surface of the prepreg at low temperature, and performs high-temperature vacuum lamination after manufacturing the three-layer circuit to form a three-layer circuit. Circuit board structure, two layers of prepreg are used in the three-layer circuit, and the high-temperature lamination conditions of the prepreg are exactly the same, and its structure is symmetrical with respect to the middle circuit layer, so, after lamination, its internal resin is relative to the middle The magnitude and direction of circuit stress can be compensated for each other, thus avoiding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More