A nor-type flash memory unit with raised common source area and preparation method thereof

A technology of flash memory unit and common source area, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc. It can solve the problems of increased source junction depth, difficulty in normal operation of memory cells, and punch-through, so as to overcome over-etching , It is beneficial to scale down and reduce the effect of short groove effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

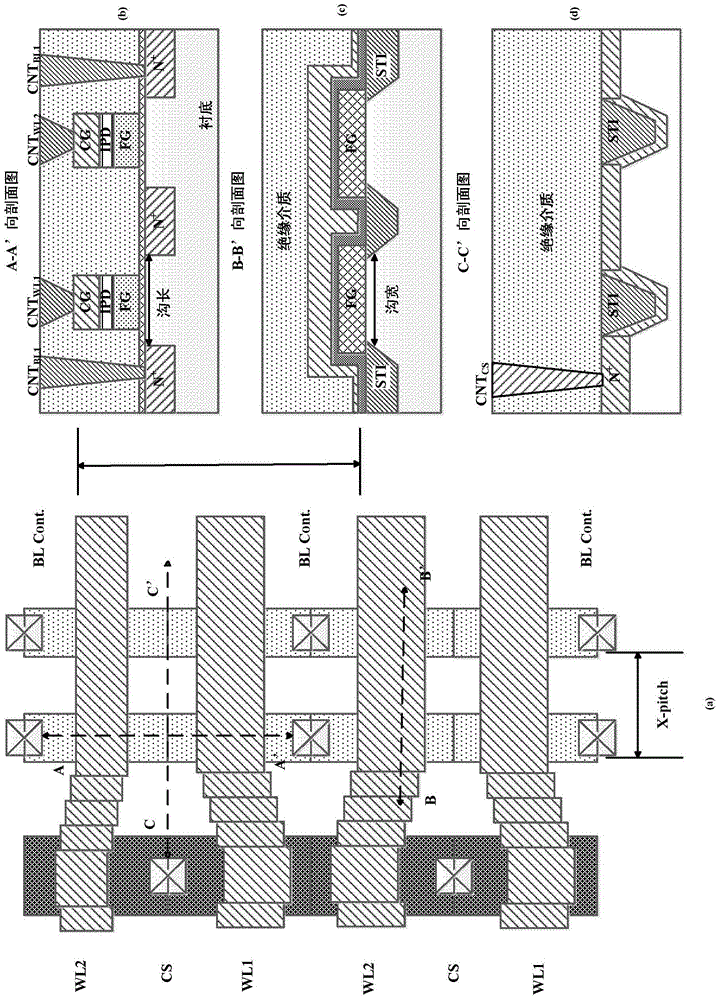

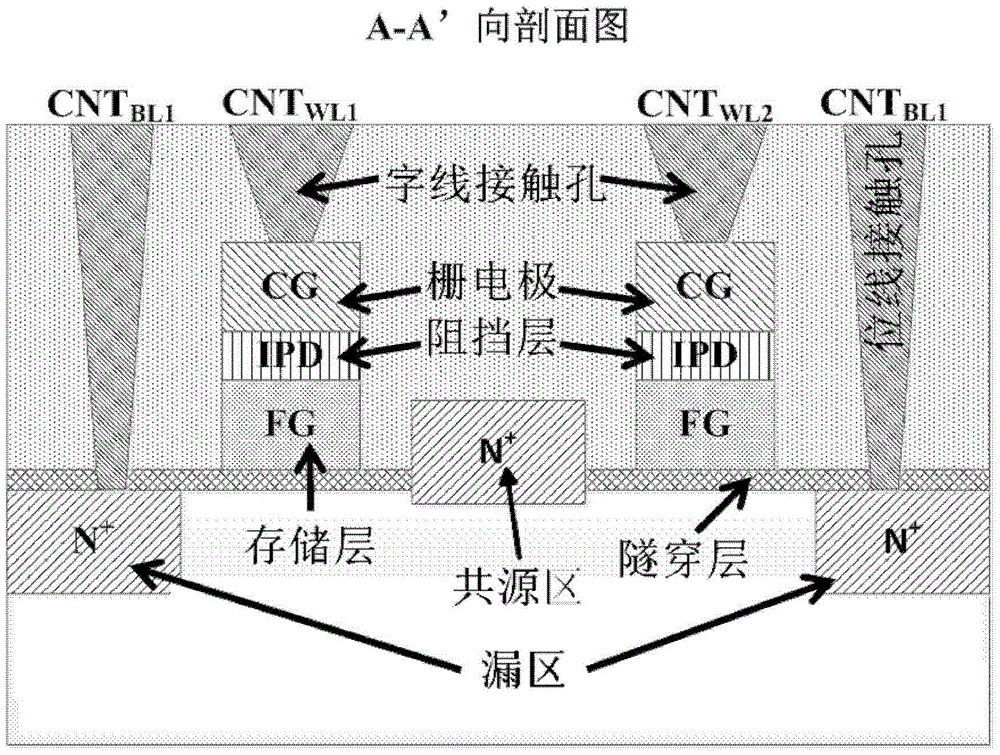

[0037] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0038] The key idea of the present invention is to modify the structure of the source area of the flash memory unit. Generally speaking, the shallow trench isolation (STI) region completes the isolation of the active region in the channel width direction of the memory cell, so the source region and the drain region are the same in the channel width direction. The injection of the common source region makes a lateral source deep junction appear. In addition, the etching of the STI region insulating layer in order to realize the connection of the common source region makes silicon over-etching appear in the source region. These two factors are the device trench The main factor that easily causes punch-through when the l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More